### **DISSERTATION**

### ANALYTICAL COST METRICS: DAYS OF FUTURE PAST

# Submitted by

Nirmal Prajapati

Department of Computer Science

In partial fulfillment of the requirements

For the Degree of Doctor of Philosophy

Colorado State University

Fort Collins, Colorado

Summer 2019

**Doctoral Committee:**

Advisor: Sanjay Rajopadhye

Wim Böhm Edwin Chong Louis-Noël Pouchet Copyright by Nirmal Prajapati 2019

All Rights Reserved

#### ABSTRACT

#### ANALYTICAL COST METRICS: DAYS OF FUTURE PAST

Future exascale high-performance computing (HPC) systems are expected to be increasingly heterogeneous, consisting of several multi-core CPUs and a large number of accelerators, special-purpose hardware that will increase the computing power of the system in a very energy-efficient way. Specialized, energy-efficient accelerators are also an important component in many diverse systems beyond HPC: gaming machines, general purpose workstations, tablets, phones and other media devices. With Moore's law driving the evolution of hardware platforms towards exascale, the dominant performance metric (time efficiency) has now expanded to also incorporate power/energy efficiency.

This work builds analytical cost models for cost metrics such as time, energy, memory access, and silicon area. These models are used to predict the performance of applications, for performance tuning, and chip design. The idea is to work with domain specific accelerators where analytical cost models can be accurately used for performance optimization. The performance optimization problems are formulated as mathematical optimization problems. This work explores the analytical cost modeling and mathematical optimization approach in a few ways. For stencil applications and GPU architectures, the analytical cost models are developed for execution time as well as energy. The models are used for performance tuning over existing architectures, and are coupled with silicon area models of GPU architectures to generate highly efficient architecture configurations. For matrix chain products, analytical closed form solutions for off-chip data movement are built and used to minimize the total data movement cost of a minimum op count tree.

#### **ACKNOWLEDGEMENTS**

I would like to thank my advisor, Sanjay Rajopadhye, for his guidance and support. He has been a continuous source of motivation. His brilliant ideas and farsightedness have awed me throughout my Ph.D. I learnt a lot from him and enjoyed being his student. I not only gained technical knowledge in the field but also learnt values of a good human being like patience, kindness, selflessness, compassion, and dedication. I feel honored to have the opportunity to work with him.

I am thankful to my committee members Wim Böhm, Louis-Noël Pouchet, and Edwin Chong for their valuable time and inputs. Their expertise and insights have helped me improve the quality of my work. In addition to the committee members, my co-authors Hristo Djidjev, Rumen Andonov, Tobias Grosser, and Nandkishore Santhi have mentored me at various stages of my Ph.D. and have been a great source of knowledge. I would like to thank all the members of the mélange group at Colorado State University for the pleasant and joyful company.

My family has supported me throughout my education. I would like to thank my parents Amrutbhai Prajapati and Nayanaben Prajapati for believing me. They recognized my love for science early in my childhood and encouraged me to pursue my passion. My parents marched against the social norms of educating a girl and invested their blood, sweat and tears to help me achieve my dreams. I would like to thank my lovely sister Anjali Prajapati and my amazing brother Vishal Prajapati for being the never ending source of energy and happiness. It is because of my siblings that I saw hopes in my darkest times.

I would like to thank Ritesh Banka, Amrapalli Garanaik, Anantkumar Shah, Aditi Prasad, Ankitaben Patel, and Athith Rao for their selfless love and support. All of these awesome, crazy people have been a huge source of motivation during the highs and lows of my Ph.D. life. Thanks to them, I survived this roller coaster!

Finally, I would like to thank everyone who contributed to my education. I would like to thank Cindy Norris, Jay Fenwick, and Alice McRae for giving me an amazing flavor of research during my Masters at Appalachian State University. I would also like to thank my middle school teacher

Late Mrs. Annama Thomas for recognizing the potential in me and molding my brain since my early childhood. She cultivated the problem solving skills in me and constantly motivated me to push my boundaries. She is no more but her lessons and values are alive in me. I would like to extend my thanks to all my relatives who have been looking forward to my graduation. I am proud to be the first generation Ph.D. in the family!

## **DEDICATION**

I would like to dedicate this thesis to the memory of my loving grandparents,

Amthiben Shankarlal Prajapati, and Kalidas Maganlal Prajapati.

You are gone but your belief in me has made this journey possible.

# TABLE OF CONTENTS

| ABSTRACT         |                                                    | i  |

|------------------|----------------------------------------------------|----|

| <b>ACKNOWL</b>   | EDGEMENTS                                          | ii |

| <b>DEDICATIO</b> | ON                                                 | ٦  |

| LIST OF TA       | BLES                                               | Х  |

| LIST OF FIG      | GURES                                              | X  |

| Chapter 1        | Introduction                                       | 1  |

| 1.1              | Specialization                                     | 3  |

| 1.2              | Breaking Abstractions                              | 7  |

| Chapter 2        | The Landscape and Navigation                       | 11 |

| 2.1              | Domain Specificity                                 | 11 |

| 2.1.1            | Comparison with Polyhedral Methods                 | 12 |

| 2.1.2            | Limitations of current domain-specific compilation |    |

| 2.2              | Design Landscape                                   |    |

| 2.3              |                                                    | 16 |

| 2.3.1            |                                                    | 17 |

| 2.3.2            |                                                    | 19 |

| 2.3.3            | 1 1                                                | 22 |

| 2.3.4            | Bottleneckology                                    |    |

| 2.4              | <del></del>                                        | 25 |

| Chapter 3        | Related Work                                       | 27 |

| 3.1              | Stencil Computations and Code Generation           |    |

| 3.2              | Performance Modeling                               |    |

| 3.3              | Chip Reverse Engineering and Area Modeling         | 29 |

| 3.4              |                                                    | 3( |

| 3.5              | Codesign                                           | 31 |

| Chapter 4        | Models and Validation                              | 32 |

| 4.1              | Execution Time Model for GPGPU Stencils            | 32 |

| 4.2              | Energy Model for Tiled Nested-Loop Codes           | 33 |

| 4.3              | Memory Access Model for GPGPU Stencils             | 35 |

| 4.4              | Silicon Area Model for GPUs                        | 36 |

| 4.5              | Data Movement Model for Matrix Multiplication      | 36 |

| Chapter 5        | Single-Metric Tuning                               | 38 |

| 5.1              | Tune for Speed                                     | 39 |

| 5.2              | Optimize for Energy                                | 39 |

| 5.3              | Minimize Data Movement                             | 40 |

| Chapter 6        | Multi-Metric Tuning                                | 41 |

| Chapter 7    | Accelerator Codesign                                                       | 42  |

|--------------|----------------------------------------------------------------------------|-----|

| Chapter 8    | Conclusions                                                                |     |

| 8.1          | Future Work                                                                |     |

| 8.1.1        | Codesign Trade-offs                                                        |     |

| 8.1.2        | Overhead Analysis                                                          | 48  |

| 8.1.3        | The effect of the hyper-threading                                          | 50  |

| 8.1.4        | Evaluation of Minimum Data Movement Algorithm for Matrix Chain             |     |

|              | Products                                                                   | 50  |

| 8.2          | Limitations of our approach                                                | 51  |

| 8.3          | Open Questions                                                             | 51  |

| Bibliography |                                                                            | 53  |

| Appendix A   | Simple, Accurate, Analytical Time Modeling and Optimal Tile Size Selection |     |

|              | for GPGPU Stencils                                                         | 75  |

| A.1          | Introduction                                                               | 75  |

| A.2          | Related work                                                               | 78  |

| A.3          | Stencils and their parallelization                                         | 79  |

| A.3.1        | Hybrid hexagonal/classical tiling                                          | 82  |

| A.3.2        | Details of the HHC compiler                                                | 84  |

| A.4          | Execution Time Model                                                       |     |

| A.4.1        | Model for hexagonal tiling                                                 |     |

| A.4.2        | Hybrid hexagonal-classic tiling for 2D stencils                            | 90  |

| A.4.3        | Hybrid hexagonal-classic tiling for 3D stencils                            |     |

| A.5          | Experimental Validation                                                    | 95  |

| A.5.1        | Baseline Experiments                                                       | 96  |

| A.5.2        | Validation results                                                         |     |

| A.6          | Tile size optimization                                                     | 100 |

| A.6.1        | The optimization problem                                                   | 100 |

| A.6.2        | Validation of the results                                                  | 102 |

| A.6.3        | Model Predicted tile sizes                                                 | 103 |

| A.6.4        | Experimental results                                                       | 103 |

| A.7          | Conclusion                                                                 | 104 |

| A.7.1        | More Analysis/ Open Questions                                              | 106 |

| Appendix B   | Energy Modeling and Optimization for Tiled Nested-Loop Codes               | 107 |

| B.1          | Introduction                                                               | 107 |

| B.2          | Related work                                                               | 109 |

| B.3          | Stencil Computations                                                       | 110 |

| B.3.1        | Smith-Waterman Algorithm (SW)                                              |     |

| B.3.2        | Jacobi 1D Stencil (J1D)                                                    |     |

| B.3.3        | Jacobi 2D Stencil (J2D)                                                    |     |

| B.4          | Tiling of Stencils                                                         |     |

| B.4.1        | Orthogonal tiling of the SW stencil                                        |     |

| B.4.2          | Tiling and parallelization of the J1D stencil                                                                                                   |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| B.4.3          | Tiling and parallelization of the J2D stencil                                                                                                   |

| B.5            | GPU implementation of tiled stencils                                                                                                            |

| B.5.1          | Overview of GPU architecture                                                                                                                    |

| B.5.2          | GPU implementation                                                                                                                              |

| B.6            | Energy model                                                                                                                                    |

| B.6.1          | Generic model                                                                                                                                   |

| B.6.2          | Energy model for the 1D kernels                                                                                                                 |

| B.6.3          | Energy model for the 2D kernels                                                                                                                 |

| B.7            | Model validation                                                                                                                                |

| B.7.1          | Computing energy parameters                                                                                                                     |

| B.7.2          | Energy parameter values and error analysis                                                                                                      |

| B.8            | Optimizing energy efficiency                                                                                                                    |

| B.8.1          | The optimization problem                                                                                                                        |

| B.8.2          | Validation of the results                                                                                                                       |

| B.9            | Conclusion                                                                                                                                      |

|                |                                                                                                                                                 |

| Appendix C     | Optimization Approach to Accelerator Codesign                                                                                                   |

| C.1            | Introduction                                                                                                                                    |

| C.1.1          | Overall approach                                                                                                                                |

| C.1.2          | Domain Specificity                                                                                                                              |

| C.1.3          | Contributions                                                                                                                                   |

| C.2            | Area Model                                                                                                                                      |

| C.2.1          | Analytical Model for GPU Area                                                                                                                   |

| C.2.2          | Calibrating the Model                                                                                                                           |

| C.2.3          | Validating the Model                                                                                                                            |

| C.3            | Optimizing software and hardware parameters                                                                                                     |

| C.3.1          | Problem formulation                                                                                                                             |

| C.3.2          | Solving the optimization problem                                                                                                                |

| C.4            | Insights                                                                                                                                        |

| C.4.1          | Insight 1: Pruning the Design Space                                                                                                             |

| C.4.2          | Insight 2: Workload Sensitivity                                                                                                                 |

| C.4.3          | Insight 3: Shared Memory Requirements                                                                                                           |

| C.4.4          | Insight 4: Resource Allocation                                                                                                                  |

| C.5            | Related work                                                                                                                                    |

| C.6            | Conclusion and Discussion                                                                                                                       |

| Appendix D     | Minimizing Data Movement for Matrix Chain Products                                                                                              |

| D.1            | Related Work                                                                                                                                    |

| D.1<br>D.2     | Off-chip Data Movement for Single Matrix Multiplication                                                                                         |

| D.2<br>D.3     | Off-chip Data Movement for Two Matrix Multiplications                                                                                           |

|                | 1                                                                                                                                               |

| D.3.1<br>D.3.2 | Option 1: $R = (A_1 A_2) A_3 \dots \dots$ |

|                | Option 2: $R = A_1(A_2A_3)$                                                                                                                     |

| D.4            | Optimal Parenthesization: Op Count                                                                                                              |

| D 5            | withinizing Data Movement for Minimilm On Collnt Tree 177                                                                                       |

| D.6 | Hyper-node Parenthesization of Minimum Op Count Tree | 180 |

|-----|------------------------------------------------------|-----|

| D.7 | Reduction in Data Movement                           | 185 |

| D.8 | Conclusion                                           | 189 |

# LIST OF TABLES

| 8.1         | Workload sensitivity. The optimal architecture configuration for a single benchmark varies significantly                                                                                                                                                                                                                     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A.1         | List of the parameters. E/C stand for elementary/composite, and S/H/P for software/hard-ware/problem type; $M_{\rm io}$ is measured in 4-byte words                                                                                                                                                                          |

| A.2         | GPU configuration                                                                                                                                                                                                                                                                                                            |

| A.3         | Parameter values for the micro-benchmarks                                                                                                                                                                                                                                                                                    |

| A.4         | Values of $C_{\text{iter}}$ in seconds                                                                                                                                                                                                                                                                                       |

| B.1         | List of the parameters. S/H/P stand for software/hardware/problem type, D/I stand for problem dependent/independent, and E/C—for elementary/composite; MA stands for multiply-add operation. $M_{\rm io}$ is measured in 4-byte words. Also, for 1-dimensional problems, the subscript on the space dimension may be dropped |

| B.2         | Table of the energy parameter values from the micro-benchmark approach and the                                                                                                                                                                                                                                               |

| <b>D</b> .2 | regression approach as described in Section B.7.2                                                                                                                                                                                                                                                                            |

| B.3         | Energy optimization error                                                                                                                                                                                                                                                                                                    |

| C.1         | Area model parameters. The top two groups are elementary parameters, and the third one is composite (some function of the elementary parameters). Of the elementary                                                                                                                                                          |

| $\alpha$    | ones, the second one are treated as variables in our optimization formulation 138                                                                                                                                                                                                                                            |

| C.2         | Workload sensitivity. The optimal architecture configuration for a single benchmark varies significantly                                                                                                                                                                                                                     |

| D.1         | Reduction(%) in total off-chip data transfers for matrix sequences                                                                                                                                                                                                                                                           |

| D.2         | Tile sizes and closed form solutions for Single MM                                                                                                                                                                                                                                                                           |

| D.3         | Tile sizes and closed form solutions for Two MM                                                                                                                                                                                                                                                                              |

# LIST OF FIGURES

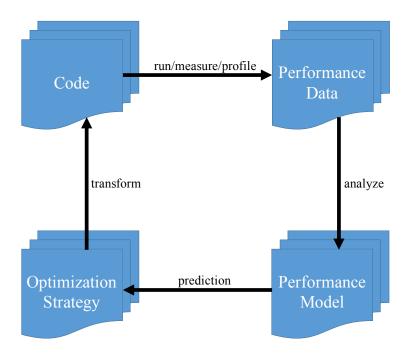

| 1.1        | HPC application performance improvement cycle. The layers represent different architectures.                                                                                                                                                                                                                                                                                                                                                                                   | 7   |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

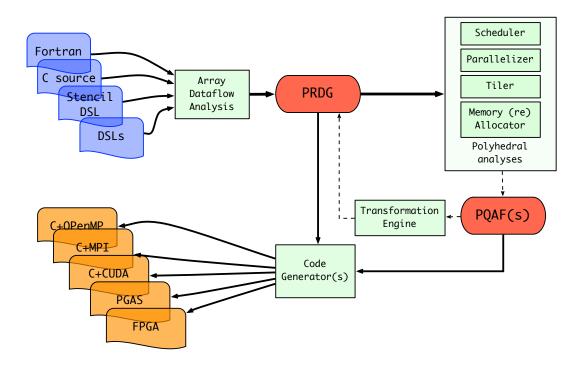

| 1.2<br>1.3 | Polyhedral Compilation                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8   |

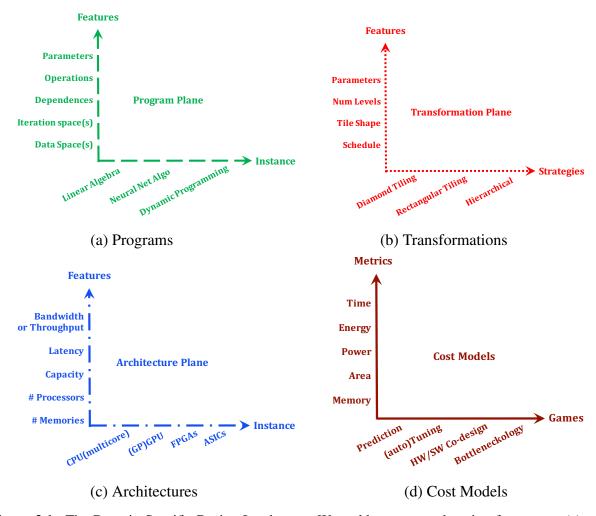

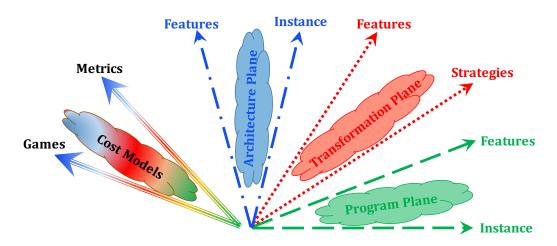

| 2.1        | The Domain-Specific Design Landscape. We tackle a narrow domain of programs (a) each one described by a small number of features. Similarly the mappings/transformations (b) we can apply are drawn form a small set, each one parameterized by a set of features. Architectures (c) are also drawn from a similarly small set, and are parameterized by their features. In each plane, the features may be hierarchical. The cost metrics (d) and the games that we can play. | 14  |

| 2.2        | The main novelty of our work! The Domain-Specific Design Landscape that we must navigate is thus the cross-product of the four planes in Fig. 2.1                                                                                                                                                                                                                                                                                                                              |     |

| 8.1        | Resource Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47  |

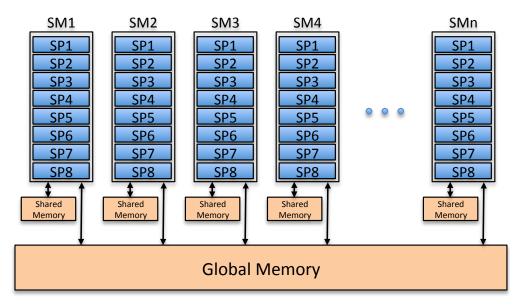

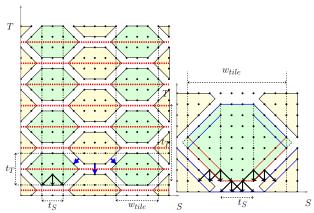

| A.1<br>A.2 | The GPU architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81  |

| A.3<br>A.4 | iterations writing to global memory)                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

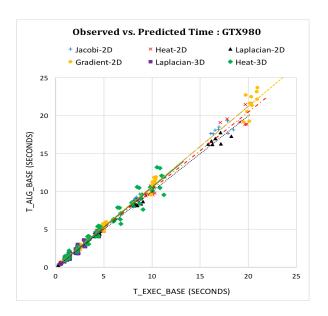

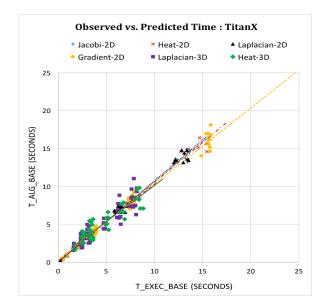

| ۸ 5        | tion time for the baseline experiments                                                                                                                                                                                                                                                                                                                                                                                                                                         | 99  |

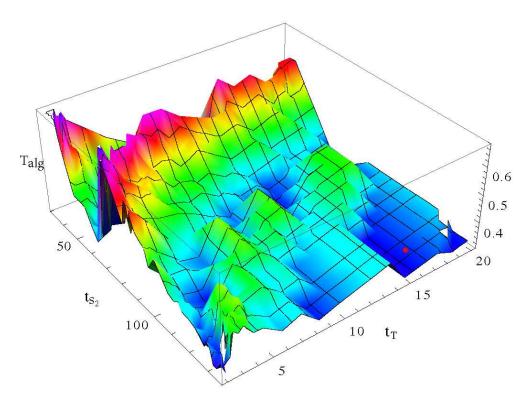

| A.5        | $T_{\rm alg}$ for Heat2D and GTX 980 as a function of $t_{\rm T}$ and $t_{\rm S_2}$ and with $t_{\rm S_1}$ fixed at 8. The red dot shows $T_{\rm alg\_min}$ , the point of minimum over all $T_{\rm alg}$                                                                                                                                                                                                                                                                      | 101 |

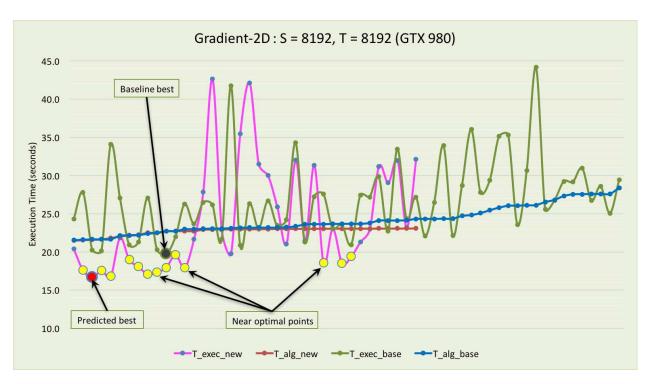

| A.6        | Predicted tile size performance of Gradient-2D for $S_1 = 8192$ , $S_2 = 8192$ and $T = 8192$ on GTX 980                                                                                                                                                                                                                                                                                                                                                                       | 104 |

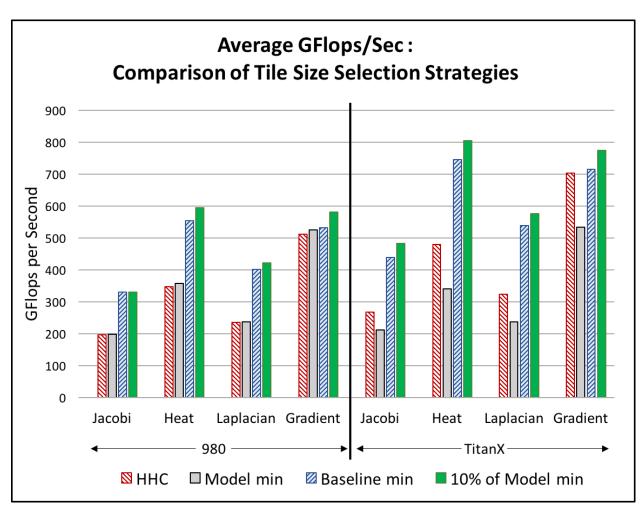

| A.7        | Average (over 10 problem sizes) GFlops/Sec achieved by different tile size selection strategies for 2D stencils                                                                                                                                                                                                                                                                                                                                                                | 105 |

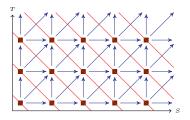

| B.1        | Orthogonal tiling for SW stencil. Small dark red squares represent tiles. Data flow of the tiles are shown in blue arrows. Red lines along the northwest-southeast diagonals represent wavefronts. The tiles that belong to the same wavefront can be processed in                                                                                                                                                                                                             |     |

| D 4        | parallel. Wavefronts are executed sequentially from southwest to northeast corner                                                                                                                                                                                                                                                                                                                                                                                              | 113 |

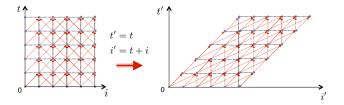

| B.2        | The original computation space (left) and the same space after the chosen transformation (right).                                                                                                                                                                                                                                                                                                                                                                              | 115 |

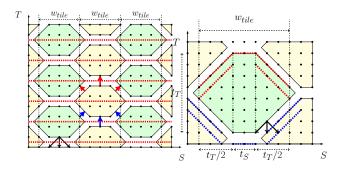

| В.3  | The computational space in hexagonal tiling is partinionned in hexagons (left). On the right side we zoom on and visualize the input/output data for a given tile. The data read from the global memory is blue colored, while the data written to the global memory is red colored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B.4  | The computational space is partitioned in hexagons (left). On the right side we zoom in and visualize the I/O data for a given tile. Blue - data read from global memory. Red - data written to global memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

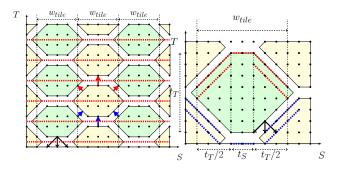

| C.1  | Best effort annotation of functional blocks in a GTX980 die photograph [1] based on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| G 2  | current understanding of the NVIDIA Maxwell architecture and chip layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

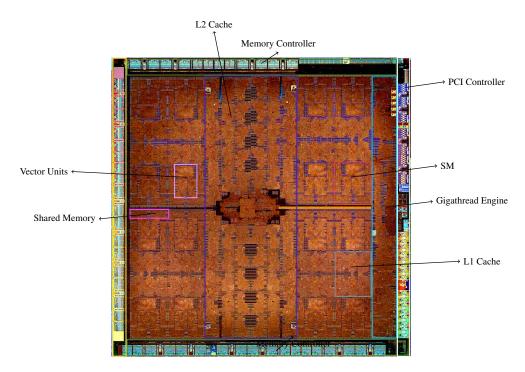

| C.2  | Linear regression models for various memory types on a Maxwell series GPU. The Cacti predicted area used to obtain the linear model are also shown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

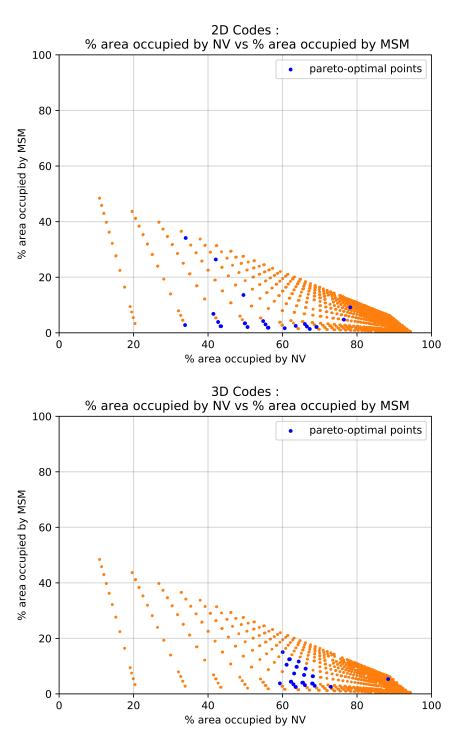

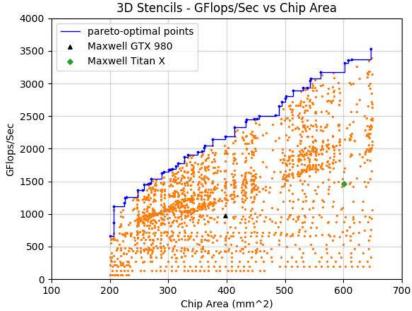

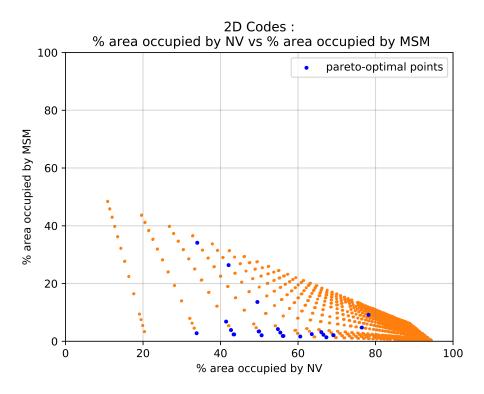

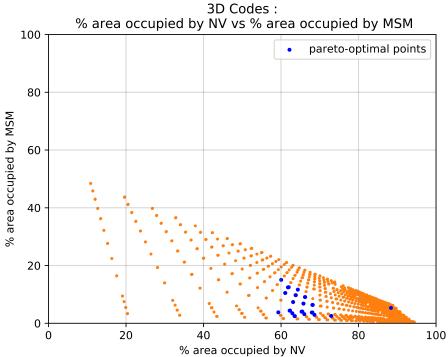

| C.3  | Optimal performance (in GFLOPs/Sec) of each feasible design point as a function of total chip area for 2D stencils (left) and 3D stencils (right). Each benchmark and input size combination is assumed to occur with equal frequency. Of the many thousands of points ( $\approx 3000$ for 2D stencils and $\approx 2000$ for 3D) many are <i>dominated</i> by other design choices—a different architecture with smaller area yields better performance. So, only a few tens of design points (the Pareto optimal points, shown in blue) need to be explored further, a nearly 100-fold savings in design cost. In addition, the performance of the existing NVIDIA Maxwell GTX980 and Titan X are also shown. The optimized designs for comparable area budget could improve performance of 2D stencils by as much as 104% (c.f. 69%) relative to the GTX980 (c.f., the TitanX). The performance of 3D stencils can be improved by as much as 123% (c.f. 126%) relative to the GTX980 (c.f., the TitanX). |

| C.4  | Resource Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

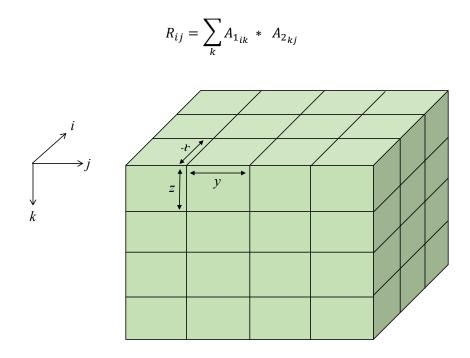

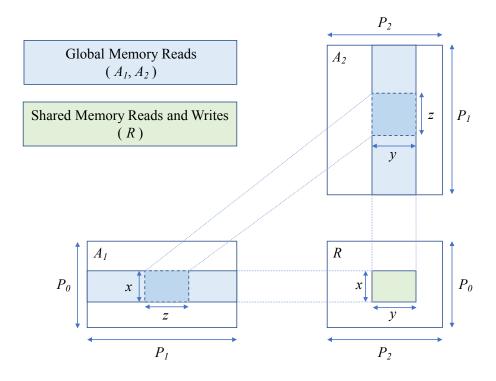

| D.1  | 3D blocking of Matrix Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D.2  | Retain the output matrix $R$ in the shared memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

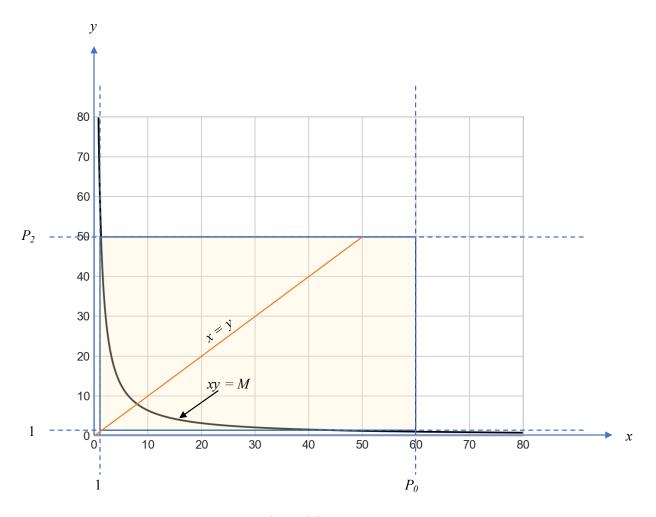

| D.3  | Minimizing the value of $(x+y)/xy$ for the case when matrix $R$ is stored on-chip 166                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

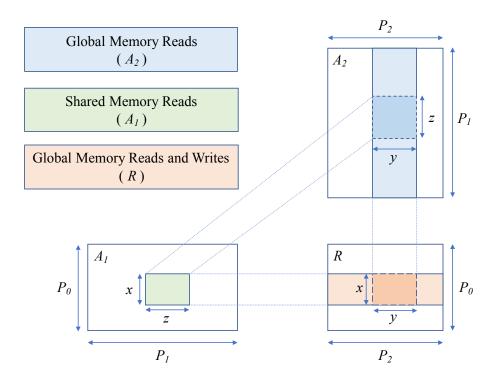

| D.4  | Retain the input matrix $A_1$ in the shared memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

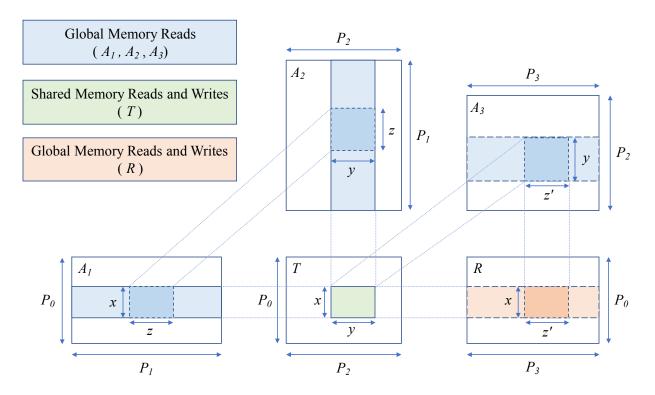

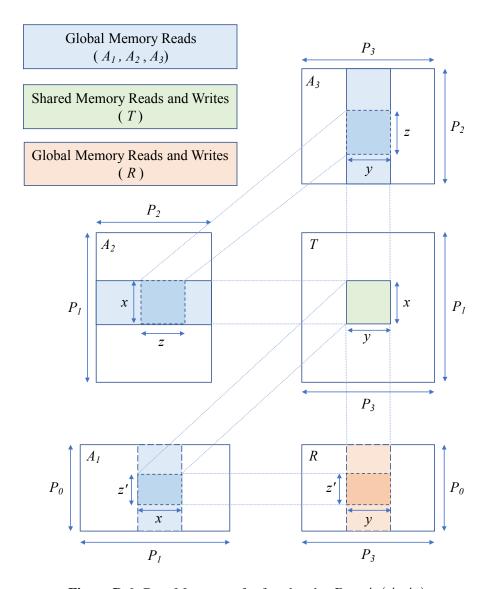

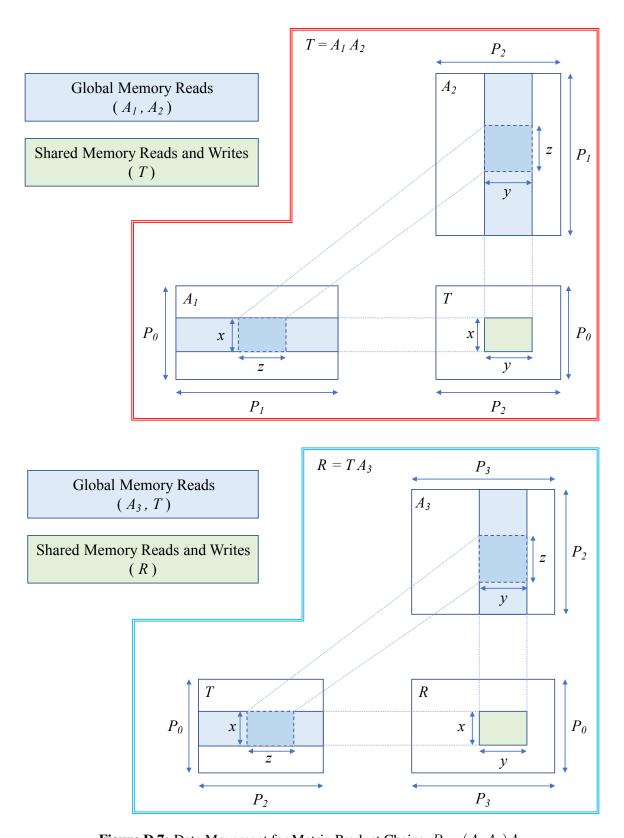

| D.5  | Data Movement for fused code: $R = (A_1 A_2) A_3 \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D.6  | Data Movement for fused code: $R = A_1(A_2A_3) \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | Data Movement for Matrix Product Chains, $R = (A_1 A_2) A_3 \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

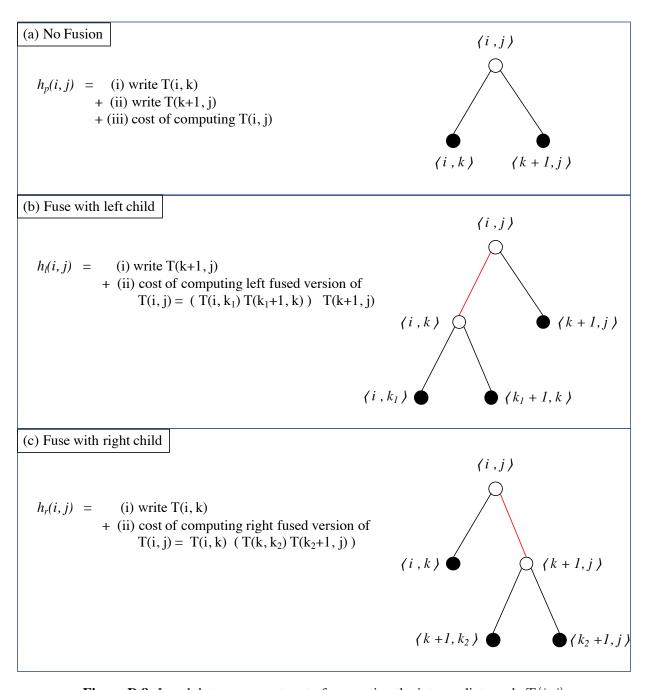

| D.8  | Local data movement cost of computing the intermediate node $T\langle i,j\rangle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D.9  | Global Data Movement Cost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

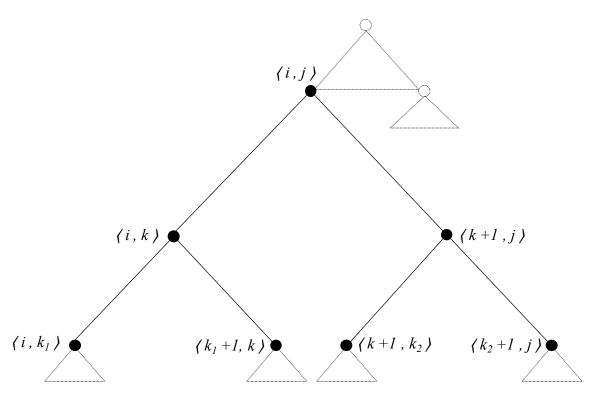

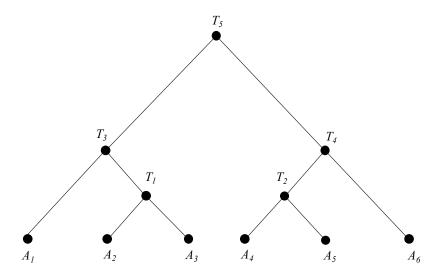

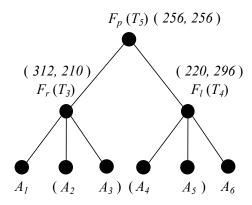

|      | Minimum Op Count Tree for the example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| וו.ע | Calculating data movement cost of the intermediate nodes of the minimum Op-Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| D 10 | Tree in figure D.10. All values(except tile sizes) are multiples of $10^4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D.12 | Minimum Op Count Tree with hyper-nodes (fused nodes) for the example 187                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# **Chapter 1**

# Introduction

"When you change the way you look at things, the things you look at change." - Max Planck

As we move towards the exascale era, the new architectures must be capable of running the massive computational problems efficiently. Scientists and researchers are continuously investing in tuning the performance of extreme-scale computational problems. These problems arise in almost all areas of computing, ranging from big data analytics, artificial intelligence, search, machine learning, virtual/augmented reality, computer vision, image/signal processing to computational science and bioinformatics.

With Moore's law driving the evolution of hardware platforms towards exascale, the dominant performance metric (time efficiency) has now expanded to also incorporate power/energy efficiency. Therefore the major challenge [2, 3, 4, 5, 6] that we face in computing systems research is: "how to solve massive-scale computational problems in the most time/power/energy efficient manner?"

The architectures are constantly evolving making the current performance optimizing strategies less applicable and new strategies need to be invented. The solution is for the new architectures, new programming models, and applications to go forward together. Doing this is, however, extremely hard. There are too many design choices in too many dimensions. The algorithms/applications may have a wide range of parameters, making them either intensely bandwidth bound or heavily compute bound, limited only by the hardware's operational throughput. This significantly affects the algorithms used to obtain the best solution. At the hardware end, the target platform affects not only the parallelization methods but also the tool-chains used. To overcome this complications, cost models and simulators are used.

We propose the following strategy to solve the problem, i.e., "how to solve massive-scale computational problems in the most time/power/energy efficient manner?":

- 1. **Models** Develop accurate analytical models (e.g. *execution time, energy, silicon area*) to predict the cost of executing a given program.

- 2. **Complete System Design** Simultaneously optimize all the cost models for the programs (computational problems) to obtain the most *time/area/power/energy efficient* solution. Such an optimization problem evokes the notion of codesign.

Codesign—the simultaneous design of hardware and software—has two common interpretations [7, 2]. *System codesign* [8, 9] is the problem of simultaneously designing hardware, run-time system, compilers, and programming environments of entire computing systems, typically in the context of large-scale, high-performance computing (HPC) systems and supercomputers. *Application codesign*, also called *hardware-software codesign* [10, 11, 12], is the problem of systematically and simultaneously designing a dedicated hardware platform and the software to execute a single application (program). The proposed approach is applicable to both contexts.

Solving the problem of *System codesign* in its full generality is very difficult [8, 5, 2, 3] because of the wide range of (i) computational problems, (ii) the programming languages and abstractions used to express them, and (iii) varying target architectures, from data centers and cloud-based platforms, to distributed heterogeneous mobile platforms such as phones, and even "things." Therefore, we suggest the following breakdown:

- 1. **Employ Domain-Specificity** Choose (i) a (small set/class) of programs, (ii) highly optimized hardware accelerators, and (iii) the optimal compiler transformations.

- Develop Cost Models Develop accurate analytical cost (Time/Data/Area/Energy) models for performance prediction and optimization.

- 3. **Mini Sub Prob Specialize** Solve the codesign problem for the specific domain in (1) using the models in (2) i.e. optimize the program, compiler and hardware parameters simultaneously.

- 4. **Large Prob Generalize** Repeat the above process to cover various important classes of programs, assign a weight to each class of programs and formulate an optimization problem

for this weighted set of program parameters. Simultaneously, solve for all the parameters and for all classes of programs.

# 1.1 Specialization

Application codesign [13] is particularly important for embedded systems. In many uses of these systems (e.g., self-driving cars, computational fluid dynamics, neural networks, medical imaging, smart cameras, and cyber-physical systems) general purpose platforms based on standard CPUs deliver inadequate "performance" on a combination of many cost metrics: speed/throughput, power/energy, weight, size, and manufacturing/fabrication cost, especially in volumes that the market can sustain. As a result, specialized hardware is essential.

Hardware platforms for embedded systems are usually heterogeneous, with (instruction-set) programmable processors (CPUs and micro-controllers), accelerators that are either instruction-set programmable (e.g., GPUs), or "hardware programmable" ones like FPGAs and reconfigurable logic, as well as Application Specific Integrated Circuits (ASICs). For HPC systems, ASICs are usually not a designer option. In either case, the platforms have specialized, highly parallel, often fine-grain, components like FPGAs, GPUs, or DSPs, called *accelerators*.

The challenge is exacerbated when we consider the fact that accelerators are not one single architecture, and moreover, are constantly evolving. For example,

- Google developed the TPU (Tensor-flow Processing Unit), an ASIC to accelerate machine learning computations. It is completely invisible to end users, who access it via the Tensor-Flow tool, and whose back end presumably makes direct library calls to TPUs.

- Microsoft released *Catapult*, an FPGA based fabric for accelerating large-scale data-center services. It is a custom design, written in Verilog, and accessed via library calls.

- At the other end of the spectrum, Facebook is developing its large scale machine learning applications using off-the-shelf GPUs and conventional tool chains: CUDA/OpenCL.

Mapping an application to an accelerator platform, *even when the hardware is fixed*, is extremely difficult. Codesign seeks to *simultaneously design* the hardware itself, and is, therefore, an even harder problem. Multiple cost metrics must be optimized, while still providing flexibility to the programmer and end user, and the design space is huge.

The key element of our approach is to exploit multiple forms of *domain-specificity* [2]. First, we tackle a specific (family of) computations that are nevertheless very important in many embedded systems. This class of computations, called *dense stencils*, includes the compute-intensive parts of many applications such as computational fluid dynamics, neural networks, medical imaging, smart cameras, image processing kernels, simulation of physical systems relevant to realistic visualization, as well as the solution of partial differential equations (PDEs) that arise in many cyber-physical systems such as automobile control and avionics.

Second, we target NVIDIA GPUs, which are *vector-parallel programmable accelerators*. Such components are now becoming de-facto standard in most embedded platforms and MPSoCs since they provide lightweight parallelism and energy/power efficiency. We further argue that they will become ubiquitous for the following reasons. Any device on the market today that has a screen (essentially, *any device*, period) has to render images. GPUs are natural platforms for this processing (for speed and efficiency). So all systems will have an accelerator, by default. If the system now needs any additional dense stencil computations, the natural target for performing it in the most speed/power/energy efficient manner is on the accelerator.

The third element of domain specificity is that we exploit a formalism called the *polyhedral model* as the tool to map dense stencil computations to GPU accelerators. Developed over the past thirty years [14, 15, 16, 17, 18], it has matured into a powerful technology, now incorporated into gcc, llvm and in commercial compilers like Rstream. Tools targeting GPUs are also available [19, 20].

Thus, we formulate the domain-specific optimization problem: *simultaneously optimize com*pilation and hardware/architectural parameters to compile stencil computations to GPUs.

Previously, we presented [21] an approach to solve the above problem as follows:

### 1. Develop Models

- (a) **Time Model [22]** We show that the elements of the domain specificity can be combined to develop simple, analytical (as well as accurate) models for the execution time of tiled stencil codes on GPUs and that these model can be used to solve for optimal tile size selection. Our model was able to predict tile sizes that achieve 30% of theoretical machine peak on NVIDIA Maxwell GTX 980 and Titan X.

- (b) **Area Model [21]** We develop a simple, analytical model for the silicon area of programmable accelerator architectures, and calibrate it using the NVIDIA Maxwell class GPUs. Our model proved to be accurate to within 2% when validated.

- (c) **Energy Model [23]** We also developed energy models, as an explicit analytic function of a set of compiler and hardware parameters, that predict the energy consumption by analyzing the source code. We used these energy models to obtain optimal solutions to tile size selection problem.

- 2. **Codesign [21]** We combine the proposed execution time model [22] and the area model [21] with a workload characterization of stencil codes to formulate a mathematical optimization problem that minimizes a common objective function of all the hardware and compiler parameters. We propose a set of Pareto optimal designs that represent optimal combination of the parameters that would allow up to 126% improvement in performance (GFlops/sec).

Despite domain specificity, the problem remains difficult. Even when done by hand for single target architecture and an application kernel, it is more art than science. Although smart designers and implementers have worked for many decades on such problems for the "application/architecture du jour," each one was usually a point-solution [24, 25, 26]. Designers invested blood, sweat and tears to find the best implementation, used it to solve their problem of interest, usually published a paper explaining the design, and moved on. Their invested effort, particularly the trade-offs they made, and lessons they learned, are lost: future designers are left to reinvent wheels.

The high-level objective is to optimize stencil codes while tuning the hardware accelerator (GPUs) developing a complete ecosystem. The goal is to *automatically and provably optimally*, *using time and/or energy as the objective function*, *map stencils to the hardware accelerators*. The idea is to obtain *provably optimal* mappings through rigorous mathematical optimizations. The proposed approach can have the following benefits.

- Automation with Optimality: the most time/power/energy efficient implementations can be derived, reducing programmers' effort. Compilation tools can be used to guide the optimal choice of transformations which will, in turn, optimize the performance of the workloads such as deep learning, image rendering, cyber-physical systems, autonomous vehicle systems, etc.

- *Future proofing:* Porting applications to new GPU architectures will require less effort. Instead of a redesign of each program, our methods can be used to develop new parallelization strategies and transformations, refine/redefine objective functions and constraints, and re-target the compiler. This one-time effort can then be amortized over many application kernels.

- *Codesign:* By casting hardware/architectural parameters as *variables* in the mathematical optimization framework, we can *solve* for their optimal values. This will enable us to systematically explore alternate GPU architectures and simultaneously tune compilation parameters. Such a codesign approach will help speed up the research work and the chip design process. The cost models can be used to quickly recognize the performance sinks and help *identify the design flaws in its early stages saving billions of dollars*.

Generalization Future exascale high-performance computing (HPC) systems are expected to be increasingly heterogeneous, consisting of several multi-core CPUs and a large number of accelerators, special-purpose hardware that will increase the computing power of the system in a very energy-efficient way [6]. Consequently, highly specialized coprocessors will become much more common in exascale than in the current HPC systems. Such specialized, energy-efficient acceler-

ators are also an important component in many diverse systems beyond HPC: gaming machines, general purpose workstations, tablets, phones and other media devices. In order to attain exascale level performance, accelerators have to become even more energy-efficient, and experts anticipate that a large part of this must come through increased specialization [2].

Our approach can be used to solve the problem of *System codesign* by applying proposed accelerator codesign techniques to all the classes of programs that optimize for all the parameters simultaneously. We provide a proof of concept of our approach, which is a stepping stone towards solving the larger problem of *transforming the GPUs into accelerators for HPC Systems*.

# 1.2 Breaking Abstractions

**Figure 1.1:** HPC application performance improvement cycle. The layers represent different architectures.

Since a long time the HPC developers and tool builders are using certain abstractions to improve the performance of applications. Figure 1.1 shows the performance improvement life cycle of an HPC application. The layers represent a separate life cycle for every architecture (e.g. GPUs, CPUs, FPGAs). A different Programming Language and System, each with its own Programming

Environment & Tools is used based on the underlying hardware architecture. Therefore, there are different codes for the same application on different hardware. Usually, the scientists who develop the algorithms/applications are completely isolated from the HPC performance tuning specialists. For every application, a profiler is used to get performance data which is analyzed to derive a performance model. The performance models are used to predict the performance and select an optimization strategy. Optimal transformation strategy is applied to get code. This cycle repeats until the satisfactory performance is obtained.

Figure 1.2: Polyhedral Compilation

Polyhedral compilers (see Figure 1.2) have a Polyhedral Reduced Dependence Graph (PRDG) as the intermediate representation of loops. Polyhedral analysis (such as scheduling, parallelizing, memory allocation, etc.) is performed on this graph. Piecewise Quasi-Affine Functions (PQAFs) are mathematical functions that transform the PRDG using cost functions. A transformed PRDG is used to generate codes. Notice the similarities and differences between Figures 1.1 and 1.2 and their performance cycles. The optimization strategies in Figure 1.1 are represent the PQAFs.

The performance models are subsumed in the polyhedral analysis phase. Our work focuses on using cost models for polyhedral analysis, in turn, breaking the cycle and reducing the time to find optimal solutions.

#### **Design Space**

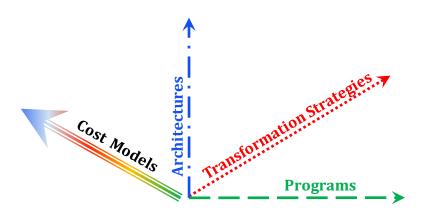

1. The main idea of our work comes out as a consequence of some of the exascale challenges [2]. For exascale system design, various architectures, programs and transformation strategies are to be explored simultaneously in order to find the optimal. We add cost models to this design space and provide *a unified view of the optimization space*. Figure 1.3 shows this view (more details in Section 2.2).

Figure 1.3: Unified View of the Design Space.

2. The above design space, however, is very large, has too many parameters and is too complicated to develop precise models. Therefore, we explore *domain specificity and identify regions* where optimization across multiple axes become possible.

We show how the analytical cost models can be used to optimize the performance of domain specific programs using transformation strategies for a given architecture in Chapter 2.

The rest of this document is organized as follows: Chapter 2 explains our proposed approach of navigating the design landscape. Chapter 3 discusses the relevant literature. Chapters 4, 5, 6, and 7 discuss the contributions. Finally, Chapter 8 concludes the document.

# **Chapter 2**

# The Landscape and Navigation

# 2.1 Domain Specificity

As we move to address the challenges of exascale computing, one approach that has shown promise is *domain specificity:* the adaptation of application, compilation, parallelization, and optimization strategies to narrower classes of domains. An important representative of such a domain is called *Stencil Computations*, and includes a class of typically compute bound parts of many applications such as partial differential equation (PDE) solvers, numerical simulations in domains like oceanography, aerospace, climate and weather modeling, computational physics, materials modeling, simulations of fluids, and signal and image-processing algorithms. One of the thirteen Berkeley dwarfs/motifs [27], is "structured mesh computations," which are nothing but stencils. Many *dynamic programming* algorithms also exhibit a similar dependence pattern. The importance of stencils has been noted by a number of researchers, indicated by the recent surge of research projects and publications on this topic, ranging from optimization methods for implementing such computations on a range of target architectures, to Domain Specific Languages (DSLs) and compilation systems for stencils [28, 29, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 40]. Workshops and conferences devoted exclusively to stencil acceleration have recently emerged.

A second aspect of domain specificity is reflected in the emergence of specialized architectures, called *accelerators*, for executing compute intensive parts of many computations. They include GPGPU, general purpose computing on graphics processing units (GPUs), and other coprocessors (Intel Xeon Phi, Knight's Landing, etc.). Initially they were "special purpose," limited to highly optimized image rendering libraries occurring in graphics processing. Later, researchers realized that these processors could be used for more general computations, and, eventually, the emergence of tools like CUDA and OpenCL enabled general purpose parallel programming on these platforms.

Exploiting the specificity of the applications and the specificity of target architectures leads to domain-specific tools to map very high level program specifications to highly tuned and optimized implementations on the target architecture. Many such tools exist, both academic research prototypes and productions systems.

As indicated earlier, our domain specificity comes in multiple flavors. First, we investigate only stencil computations. They belong to a class of programs called *uniform dependence computations*, which are themselves a proper subset of "affine loop programs." Such programs can be analyzed and parallelized using a powerful methodology called the polyhedral model [14, 15, 49, 16, 17, 18, 50, 51], and many tools are widely available, e.g., PPCG, developed by the group at ENS, Paris [52]. Second, we tackle a specific target platform, namely a single GPU accelerator, and PPCG includes a module that targets GPUs and incorporates a sophisticated code generator developed by Grosser et al. [19] that employs a state-of-the-art tiling strategy called *hybrid hexagonal classic tiling*. An open source compiler, implementing this strategy is also available, henceforth called the HHC compiler.

# 2.1.1 Comparison with Polyhedral Methods

The landscape described (in Figure 1.3) allows us to place our work in context. Although our methods are for domain specific purposes, an extreme situation with CPUs as the architecture, and the set of polyhedral programs allows us to compare with conventional compilation.

The optimization problem a compiler "solves" is: *pick transformation parameters so as to optimize the program property of interest, typically execution time.* Since it has a single (or a small handful of) predetermined strategies, it is a limited kind of mathematical optimization problem. The objective function is a surrogate for execution time.

Now consider PLuTO [51], a state-of-the art polyhedral compiler based on a mathematical representation of both programs and transformations. By considering only polyhedral programs and transformations, the optimization problems are rigorous. By default, PLuTO targets multicore CPUs, and uses a transformation strategy that combines one level of tiling, loop fusion and

(loop/wavefront) parallelization of tiles. It solves a mathematical optimization problem where the schedule parameters (coefficients of tiling and schedule hyperplanes) are the unknown variables, and the cost function is the number of linearly independent tiling hyperplanes, combined with a quantitative measure of the length of the inter-tile dependences. This is again, a surrogate for the total execution time, and leads to solutions that while reasonable, are not *provably* optimal. Moreover, parameters like tile sizes, vectorization and inter-tile schedule are chosen using simple heuristics, and are not part of the optimization.

## 2.1.2 Limitations of current domain-specific compilation

Consider how polyhedral compilation has recently evolved. Bondhugula et al. [53] proposed an extension of PLuTO for periodic stencil computations, and Bandishti et al. [54] developed another extension to allow concurrent starts. Since the objective functions in these strategies are all surrogates for the execution time, there is no way to compare across the strategies. Authors leave the choice of strategy to the user, via compiler flags. Recently it was shown (in [55], both quantitatively and empirically) that while concurrent start may be faster for iteration spaces with a certain aspect ratio of the program size parameters, the best performance for the same program with different aspect ratio is provided by the basic PLuTO algorithm.

As another example, Grosser et al. [19] proposed a novel combination of hexagonal and classic tiling for stencil programs on GPUs. They demonstrated—only empirically—performance gains compared to previous strategies, but did not quantitatively explore cases where HHC was better.

As a consequence, polyhedral compilation remains difficult. Every time a new strategy is developed, the authors publish a paper, and empirically show that their results are better than previous ones. They usually do not provide a quantitative, analytical comparison, thereby preventing a better, collective understanding of how to solve the bigger, global problem. Our intention is not to criticize the field: the problems today are difficult enough that significant effort is needed for even developing such "point solutions." Our approach is a step towards addressing these limitations.

# 2.2 Design Landscape

To place our work into context, to precisely formulate the problems we address, and to describe the approach we take to solve them, we show the design landscape of domain-specific optimization problems. It has six dimensions, organized into three planes (Fig. 2.1 (a), (b) and (c)). Each plane has two axes: *instances*, and *features*. The feature axis may be hierarchical, and parameterized.

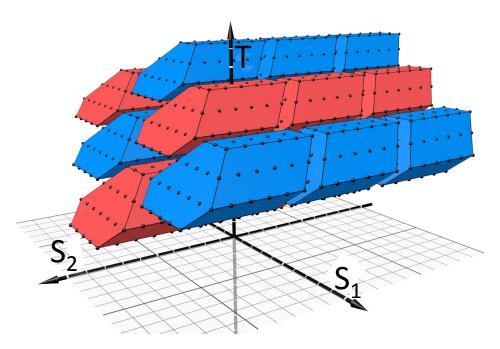

**Figure 2.1:** The Domain-Specific Design Landscape. We tackle a narrow domain of programs (a) each one described by a small number of features. Similarly the mappings/transformations (b) we can apply are drawn form a small set, each one parameterized by a set of features. Architectures (c) are also drawn from a similarly small set, and are parameterized by their features. In each plane, the features may be hierarchical. The cost metrics (d) and the games that we can play.

The *program plane* (Fig. 2.1(a)) consists of instances of *dense stencil computations*, such as *Convolutional Neural Net* (a machine learning kernel), *Heat-3D* (a stencil computation from computational science), *Clustal-3D* (a dynamic programming kernel from bioinformatics). Because of domain specificity, each program is *compactly* described with a small set of *features*, such as: (i) a set of *iteration spaces* (ii) a set of *data spaces*, (iii) a set of *dependences*, (iv) a set of *computational operators* (e.g., loop bodies), and (iv) one or more *size parameters*.