# **DISSERTATION**

# RELIABILITY-AWARE AND ENERGY-EFFICIENT SYSTEM LEVEL DESIGN FOR NETWORKS-ON-CHIP

# Submitted by

Yong Zou

Department of Electrical and Computer Engineering

In partial fulfillment of the requirements

For the Degree of Doctor of Philosophy

Colorado State University

Fort Collins, Colorado

Spring 2015

**Doctoral Committee:**

Advisor: Sudeep Pasricha

Sourajeet Roy Tom Chen Wim Bohm Copyright by Yong Zou 2015

All Rights Reserved

#### **ABSTRACT**

# RELIABILITY-AWARE AND ENERGY-EFFICIENT SYSTEM LEVEL DESIGN FOR NETWORKS-ON-CHIP

With CMOS technology aggressively scaling into the ultra-deep sub-micron (UDSM) regime and application complexity growing rapidly in recent years, processors today are being driven to integrate multiple cores on a chip. Such chip multiprocessor (CMP) architectures offer unprecedented levels of computing performance for highly parallel emerging applications in the era of digital convergence. However, a major challenge facing the designers of these emerging multicore architectures is the increased likelihood of failure due to the rise in transient, permanent, and intermittent faults caused by a variety of factors that are becoming more and more prevalent with technology scaling. On-chip interconnect architectures are particularly susceptible to faults that can corrupt transmitted data or prevent it from reaching its destination. Reliability concerns in UDSM nodes have in part contributed to the shift from traditional busbased communication fabrics to network-on-chip (NoC) architectures that provide better scalability, performance, and utilization than buses.

In this thesis, to overcome potential faults in NoCs, my research began by exploring fault-tolerant routing algorithms. Under the constraint of deadlock freedom, we make use of the inherent redundancy in NoCs due to multiple paths between packet sources and sinks and propose different fault-tolerant routing schemes to achieve much better fault tolerance capabilities than possible with traditional routing schemes. The proposed schemes also use replication opportunistically to optimize the balance between energy overhead and arrival rate.

As 3D integrated circuit (3D-IC) technology with wafer-to-wafer bonding has been recently proposed as a promising candidate for future CMPs, we also propose a fault-tolerant routing scheme for 3D NoCs which outperforms the existing popular routing schemes in terms of energy consumption, performance and reliability. To quantify reliability and provide different levels of intelligent protection, for the first time, we propose the network vulnerability factor (NVF) metric to characterize the vulnerability of NoC components to faults. NVF determines the probabilities that faults in NoC components manifest as errors in the final program output of the CMP system. With NVF aware partial protection for NoC components, almost 50% energy cost can be saved compared to the traditional approach of comprehensively protecting all NoC components. Lastly, we focus on the problem of fault-tolerant NoC design, that involves many NP-hard sub-problems such as core mapping, fault-tolerant routing, and fault-tolerant router configuration. We propose a novel design-time (RESYN) and a hybrid design and runtime (HEFT) synthesis framework to trade-off energy consumption and reliability in the NoC fabric at the system level for CMPs. Together, our research in fault-tolerant NoC routing, reliability modeling, and reliability aware NoC synthesis substantially enhances NoC reliability and energy-efficiency beyond what is possible with traditional approaches and state-of-the-art strategies from prior work.

#### **ACKNOWLEDGEMENT**

First and foremost, I would like to extend my sincere gratitude to my advisor Dr. Sudeep Pasricha who continuously inspired me and provided vast guidance towards the completion of this research. The course and research work I did under the guidance of Dr. Sudeep Pasricha truly helped me to develop expertise from silicon-to-system. His words of wisdom enabled me to learn cutting edge technologies by understanding and addressing many of the challenges faced by industry as well as the research community. By providing focus on critical and valuable research problems and practical solutions, he helped me to get visibility for my research within well-known conferences, journals and institutions. Dr. Sudeep Pasricha is dynamic, enthusiastic, energetic and full of many ideas, which truly makes him one of the greatest advisers and Professors I have known and worked with. The regular brainstorming sessions with Dr. Sudeep Pasricha provided me great insight on many technological areas. I am truly grateful for his excellent guidance and support over the past six years. Without his guidance and help, this research work was definitely not possible. I recall our brainstorming sessions for every research paper or publication that I worked on, and always felt that I was full of ideas to try solving the next set of challenges every time walking out of his office. I performed many "what-if' analysis cases" to obtain the best possible solutions. Dr. Sudeep Pasricha always kept raising the bar and always pushed me to do better in every aspect of research. I was also fortunate to attend a number of conferences and present my work in front many researchers and the engineering community. The exciting feedback and awards received during these conferences speaks for itself about the high standard that Dr. Sudeep Pasricha adheres to in all aspects of research that includes every major and minor aspect of research. If I look back, not only have I gained

technical knowledge but his guidance has also helped to improve my presentation, communication, and writing skills.

I would like to take this opportunity to thank the respected members of my PhD committee, Dr. Sourajeet Roy, Dr. T. W. Chen and Dr. Wim Bohm for their insightful feedback and encouragement for my research. The feedback they provided me helped to enhance and broaden my research. I am also thankful to the many students in Dr. Pasricha's MECS lab for their support and help during my PhD: Ishan Thakkar, Yi Xiang, C Sai Vineel Reddy, Tejasi Pimpalkhute, Nishit Kapadia, Mark Oxley, Dalton Young and Srinivas Desai. Weekly team meetings managed by Dr. Sudeep Pasricha helped to institutionalize the knowledge through the presentations and discussions with all team members.

Last but not least, I would like to thank my family for their support to continue my research. My wife Eva encouraged and supported me to continue my studies and inspired me to keep going while managing multiple priorities with my family, studies, and job. This achievement was not possible without their immense support.

# DEDICATION

To my parents, beautiful wife Eva, all of my friends and family

# TABLE OF CONTENTS

| ABSTRACT                                         | ii  |

|--------------------------------------------------|-----|

| ACKNOWLEDGEMENT                                  | iv  |

| DEDICATION                                       | vi  |

| TABLE OF CONTENTS                                | vii |

| LIST OF TABLES                                   | xi  |

| LIST OF FIGURES                                  | xii |

| CURRICULUM VITAE                                 | xvi |

| CHAPTER 1 INTRODUCTION                           | 1   |

| 1.1 Motivation                                   | 1   |

| 1.1.1 Network-on-chip (NoC)                      | 1   |

| 1.1.2 Fault tolerance in NoC                     | 4   |

| 1.2 Fault-tolerant NoC routing                   | 6   |

| 1.3 3D NoC interconnection                       | 7   |

| 1.4 NoC reliability modeling                     | 9   |

| 1.5 NoC system level reliability aware synthesis | 10  |

| 1.6 Contribution                                 | 13  |

| 1.7 Thesis outline                               | 16  |

| CHAPTER 2 LITERATURE SURVEY                      | 18  |

| 2.1 Fault-tolerant NoC routing                   | 18  |

| 2.2 NoC reliability modeling                     | 21  |

| 2.3 NoC reliability aware synthesis              | 23  |

| CHAPTER 3 FAULT-TOLERANT ROUTING ALGORITHM DESIGN | 26 |

|---------------------------------------------------|----|

| 3.1 OE+IOE fault-tolerant routing scheme          | 26 |

| 3.1.1 OE and inverted OE turn models              | 26 |

| 3.1.2 OE+IOE routing scheme: overview             | 28 |

| 3.1.3 Router architecture                         | 34 |

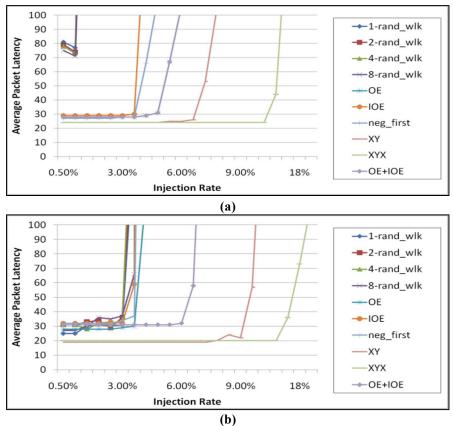

| 3.1.4 Experimental studies                        | 36 |

| 3.1.5 Summary                                     | 46 |

| 3.2 NARCO neighbor aware fault-tolerant routing   | 47 |

| 3.2.1 NARCO: fault-tolerant routing overview      | 48 |

| 3.2.2 Experimental results                        | 51 |

| 3.2.3 Summary                                     | 55 |

| 3.3 NS-FTR fault-tolerant routing.                | 55 |

| 3.3.1 NS-FTR routing scheme                       | 56 |

| 3.3.3 Router architecture and control network     | 62 |

| 3.3.4 Experimental studies                        | 64 |

| 3.3.5 Summary                                     | 72 |

| 3.4 Fault-tolerant routing for 3D NoCs            | 73 |

| 3.4.1 Proposed 4NP-First routing scheme           | 73 |

| 3.4.2 4NP-first router implementation             | 80 |

| 3.4.3 Experiments                                 | 83 |

| 3.4.4 Summary                                     | 90 |

| 3.5 Chapter summary                               | 90 |

| CHAPTER 4 RELIABILITY MODELING FOR NOCS           | 91 |

| 4.1 Motivation                               | 91  |

|----------------------------------------------|-----|

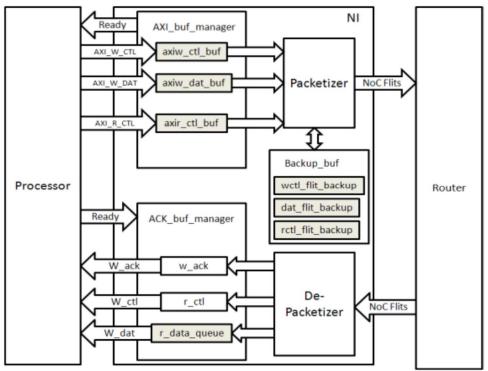

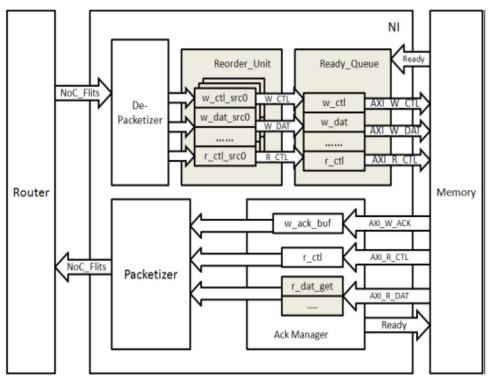

| 4.2 Network interface architecture           | 92  |

| 4.3 Network vulnerability factor (NVF)       | 95  |

| 4.3.1 Idle state                             | 95  |

| 4.3.2 Write-write                            | 96  |

| 4.3.3 Read mask                              | 97  |

| 4.3.4 AXI protocol                           | 97  |

| 4.3.5 Other scenarios                        | 98  |

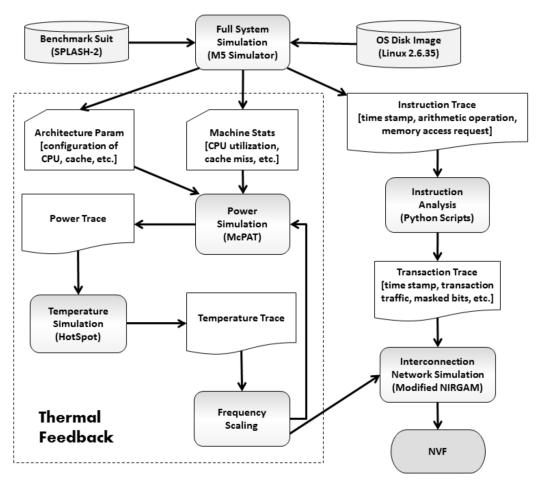

| 4.4 NVF estimation flow                      | 98  |

| 4.5 Evaluation studies                       | 100 |

| 4.5.1 Experiment setup                       | 100 |

| 4.5.2 Thermal-aware NVF estimates for NIs    | 101 |

| 4.5.2 NI reliability                         | 105 |

| 4.6 Chapter summary                          | 108 |

| CHAPTER 5 FAULT-TOLERANT NOC SYNTHESIS       | 109 |

| 5.1 Design time fault-tolerant NoC synthesis | 109 |

| 5.1.1 Motivation                             | 110 |

| 5.1.2 Problem formulation                    | 111 |

| 5.1.3 Reliability model                      | 113 |

| 5.1.4 Power model                            | 116 |

| 5.1.5 RESYN synthesis framework              | 117 |

| 5.1.6 Experimental results                   | 123 |

| 5.1.7 Summary                                | 127 |

| 5.2 HEFT design/run time hybrid fault-tolerant NoC synthesis | 128 |

|--------------------------------------------------------------|-----|

| 5.2.1 Motivation                                             | 128 |

| 5.2.2 Problem formulation                                    | 129 |

| 5.2.3 Reliability and power modeling                         | 132 |

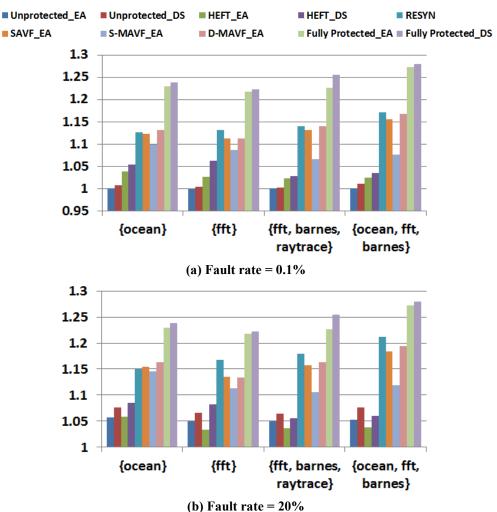

| 5.2.4 HEFT synthesis framework                               | 135 |

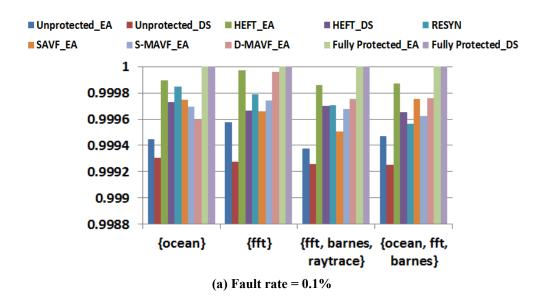

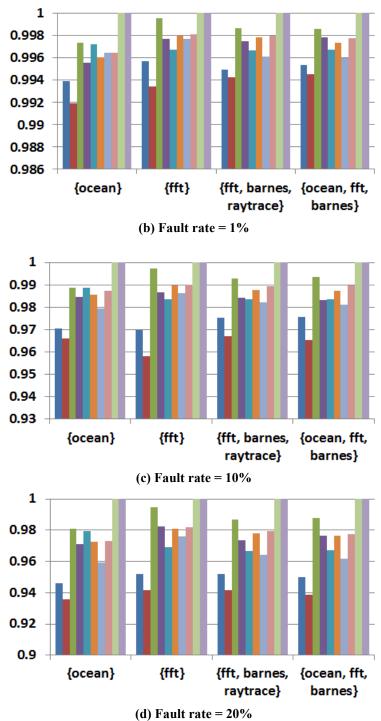

| 5.2.5 Experimental results                                   | 145 |

| 5.2.6 Summary                                                | 157 |

| 5.3 Chapter summary                                          | 157 |

| CHAPTER 6 SUMMARY AND FUTURE WORK DIRECTIONS                 | 158 |

| 6.1 Research summary                                         | 158 |

| 6.2 Future research                                          | 161 |

| REFERENCES                                                   | 164 |

# LIST OF TABLES

| Table 1 HECC vs. TMR overhead comparison                      | 12  |

|---------------------------------------------------------------|-----|

| Table 2 Instructions with masking potential                   | 97  |

| Table 3 Network interface buffer description                  | 101 |

| Table 4 Router module power library (45nm)                    | 117 |

| Table 5 HECC vs. TMR overhead comparison                      | 131 |

| Table 6 unACE bits across flit types (x indicates unACE bits) | 133 |

| Table 7 Splash-2 workloads                                    | 147 |

| Table 8 Synthesis framework                                   | 152 |

# LIST OF FIGURES

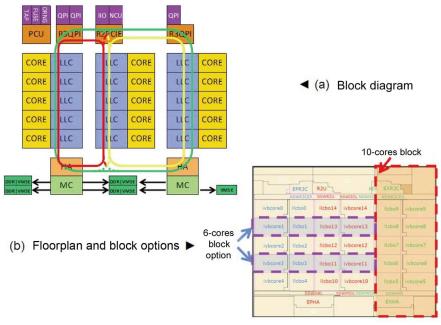

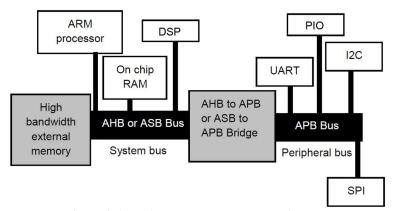

| Figure 1 Block diagram and die diagram of Ivytown                                   | 2               |

|-------------------------------------------------------------------------------------|-----------------|

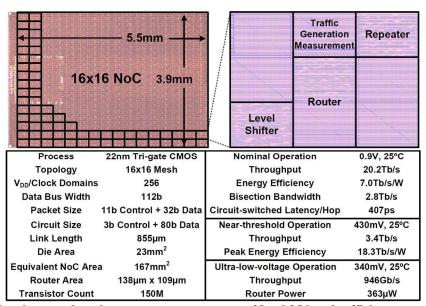

| Figure 2 AMBA bus-based system architecture                                         | 2               |

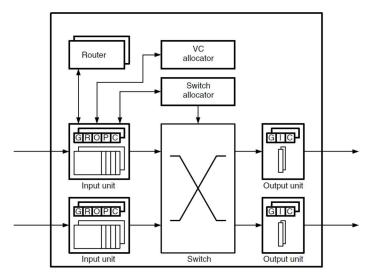

| Figure 3 Die micrograph and measurement summary of Intel 256-node efficient netw    | vork-on-chip    |

|                                                                                     | 3               |

| Figure 4 Virtual-channel NoC router block diagram [1]                               | 3               |

| Figure 5 Routing path diversity                                                     | 6               |

| Figure 6 Reliability aware NoC synthesis framework                                  | 10              |

| Figure 7 Core to tile mapping                                                       | 11              |

| Figure 8 Router fault-tolerant configuration                                        | 13              |

| Figure 9 OE and IOE prohibited turns based on column; black arrows indicate prohib  | oited turns in  |

| OE, while red arrows indicate prohibited turns in IOE                               | 27              |

| Figure 10 SystemC pseudocode for OE turn restrictions.                              | 32              |

| Figure 11 Choosing minimal paths (a) destination to the north-east of source, (b) d | estination to   |

| the north-west of source                                                            | 33              |

| Figure 12 Router architecture                                                       | 34              |

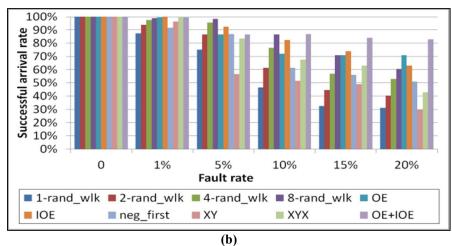

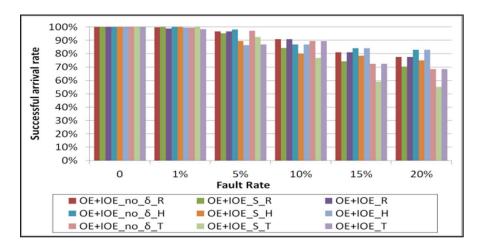

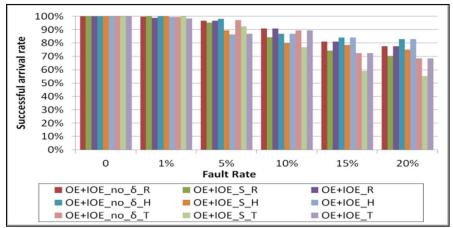

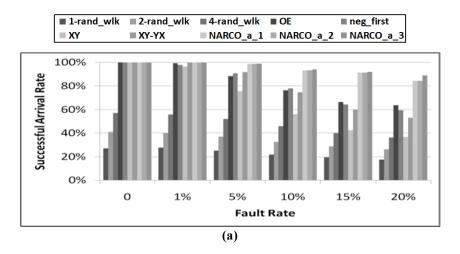

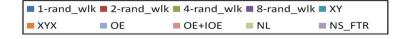

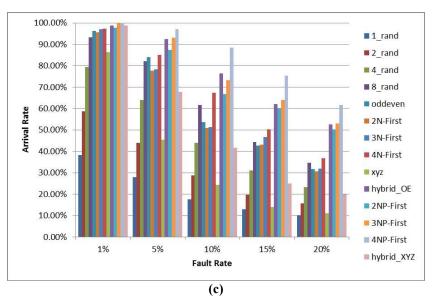

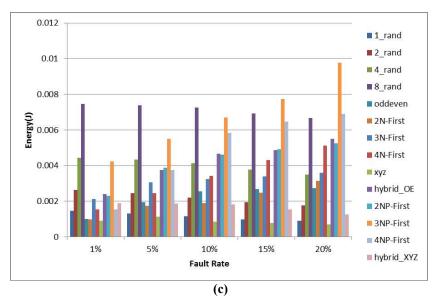

| Figure 13 Packet arrival rate for 6×6 NoC (a) Uniform random traffic, (b) Hotspo    | ot traffic, (c) |

| Transpose traffic                                                                   | 39              |

| Figure 14 Packet arrival rate for 9×9 NoC (a) Uniform random traffic, (b) Hotspo    | ot traffic, (c) |

| Transpose traffic                                                                   | 41              |

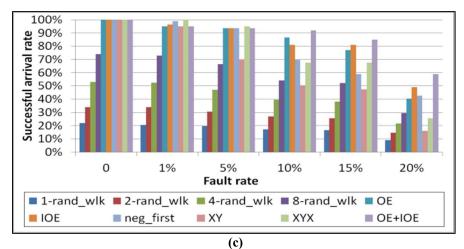

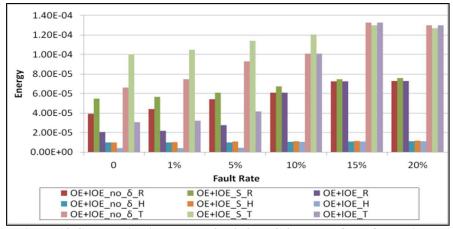

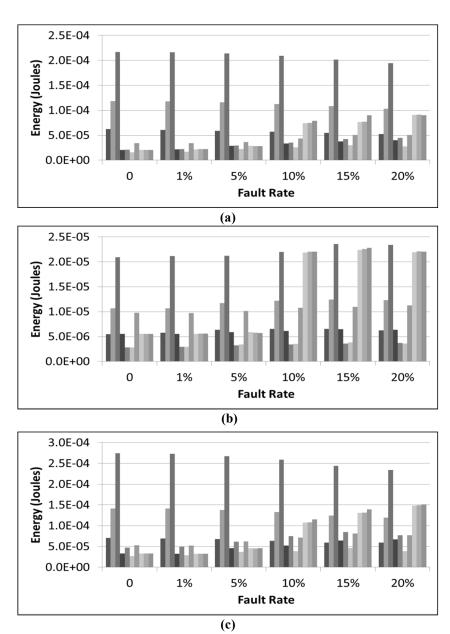

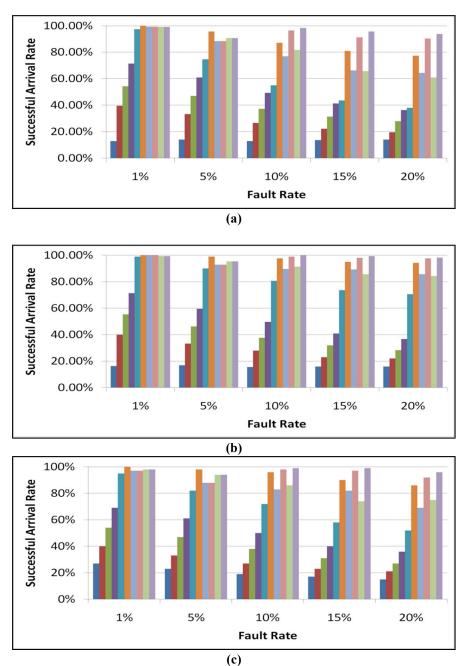

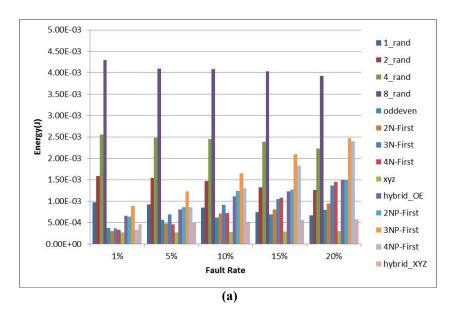

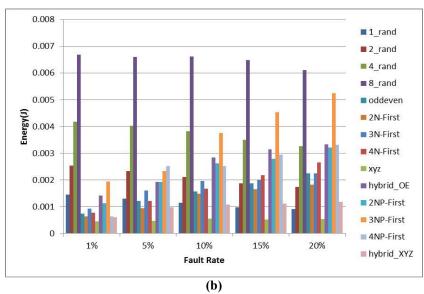

| Figure 15 Communication energy for 9x9 NoC (a) Uniform random traffic, (b) Ho       | tspot traffic,  |

| (c) Transpose traffic                                                               | 43              |

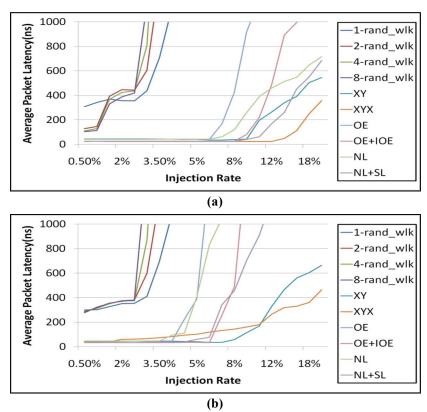

| Figure 16 Average packet latency for 9x9 NoC with uniform random traffic (a) 1% fault rate, (b   |

|--------------------------------------------------------------------------------------------------|

| 20% fault rate 44                                                                                |

| Figure 17 Packet arrival rate for 9x9 NoC for three OE+IOE variants under uniform randon         |

| traffic (R), hotspot traffic (H), and transpose traffic (T)                                      |

| Figure 18 Communication energy for 9x9 NoC for three OE+IOE variants under uniform               |

| random traffic (R), hotspot traffic (H), and transpose traffic (T)                               |

| Figure 19 SystemC pseudocode for OE turn restrictions                                            |

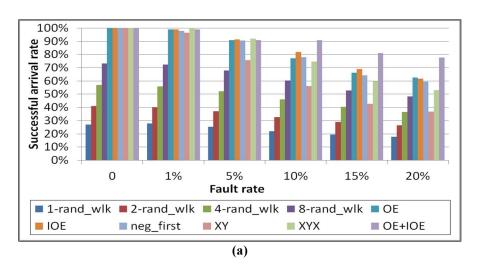

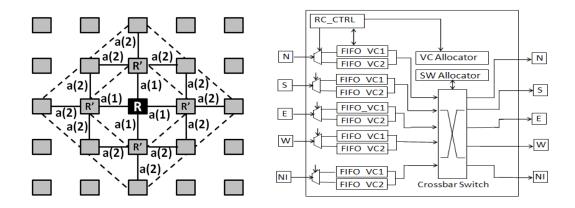

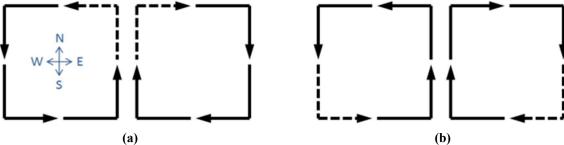

| Figure 20 (a) Neighborhood awareness (b) Router architecture                                     |

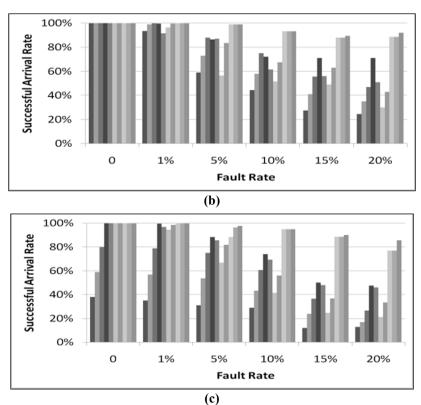

| Figure 21 Packet arrival rate for 9×9 NoC (a) Uniform random traffic, (b) Hotspot traffic, (c    |

| Transpose traffic                                                                                |

| Figure 22 Communication energy for 9x9 NoC (a) Uniform random traffic, (b) Hotspot traffic       |

| (c) Transpose traffic                                                                            |

| Figure 23 Turns allowed in the (a) North-last (b) South-last algorithms                          |

| Figure 24 SystemC pseudocode for NL turn restriction checking                                    |

| Figure 25 NL turn restriction check phase circuit diagram                                        |

| Figure 26 Path selection scenarios for NL turn scheme 6                                          |

| Figure 27 Router architecture 63                                                                 |

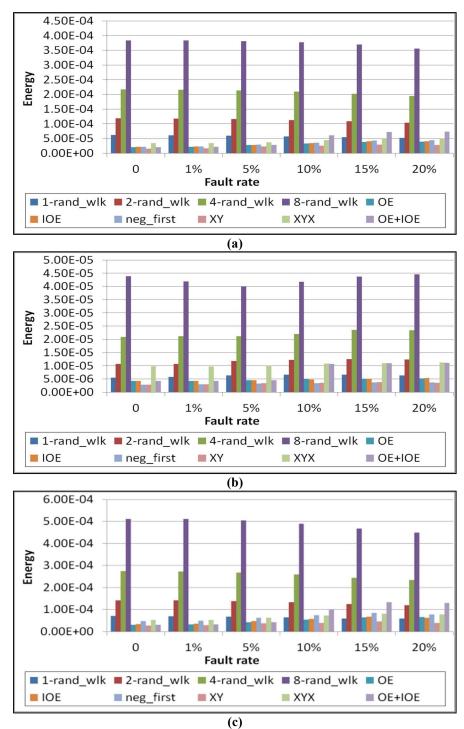

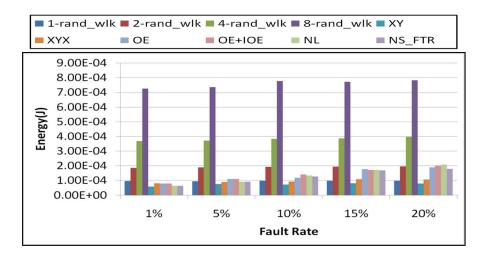

| Figure 28 Packet arrival rate for 9×9 NoC with (a) permanent faults, (b) intermittent faults, (c |

| both permanent and intermittent faults                                                           |

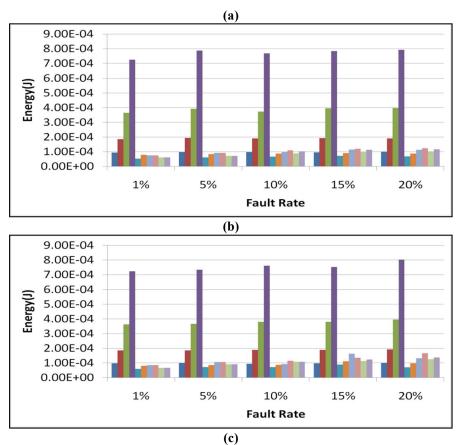

| Figure 29 Communication energy for 9×9 NoC with (a) permanent faults (b) intermittent faults     |

| (c) both permanent and intermittent faults                                                       |

| Figure 30 Average packet latency for 9×9 NoC with both permanent and intermittent faults (a      |

| 1% fault rate, (b) 20% fault rate                                                                |

| Figure 31 Forbidden turns in the 4N-First turn model                                             |

|--------------------------------------------------------------------------------------------------|

| Figure 32 Pseudocode for 4N-First turn restriction checking                                      |

| Figure 33 Node diversity and prioritized path for Case 1                                         |

| Figure 34 Node diversity and prioritized path for Case 2                                         |

| Figure 35 Router architecture 82                                                                 |

| Figure 36 4N-First routing logic circuit diagram                                                 |

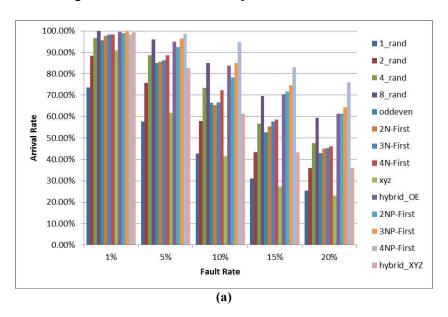

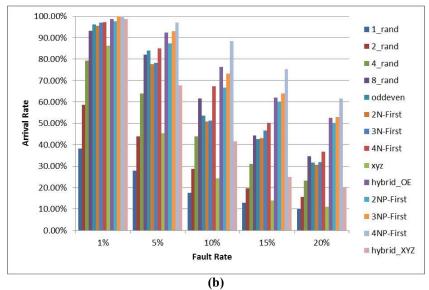

| Figure 37 Packet arrival rate for 5×5×4 NoC (a) Uniform random (b) Transpose (c) Hotspot 87      |

| Figure 38 Energy consumption for 5×5×4 NoC (a) Uniform random (b) Transpose (c) Hotspot 89       |

| Figure 39 Processor network interface block diagram                                              |

| Figure 40 Memory network interface block diagram                                                 |

| Figure 41 NVF estimation flow 99                                                                 |

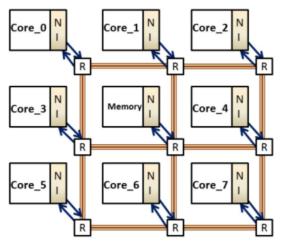

| Figure 42 CMP network topology                                                                   |

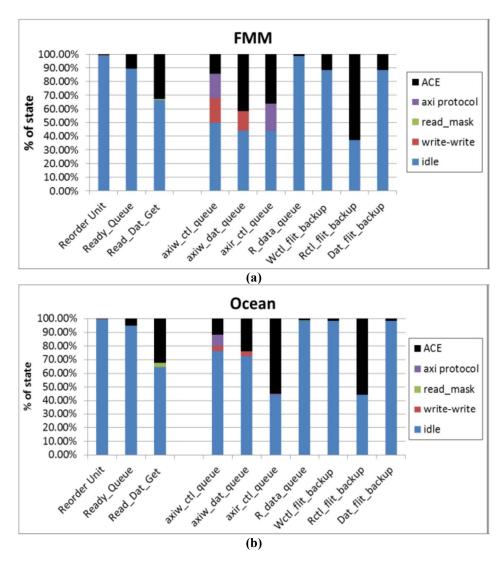

| Figure 43 Breakdown of different architectural and microarchitectural states for the NI buffer   |

| with (a) FMM (b) Ocean (c) Water-Nsquared; (NVF for each buffer is the % of cycles it contain    |

| ACE bits)                                                                                        |

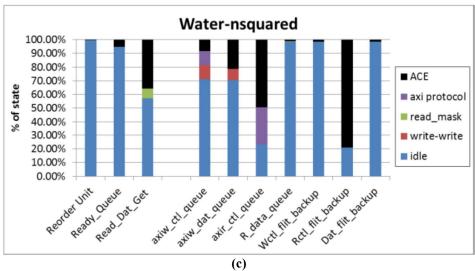

| Figure 44 Breakdown of write and read masking for subset of NI buffers, for (a) FMM (b) Ocean    |

| (c) Water-Nsquared 104                                                                           |

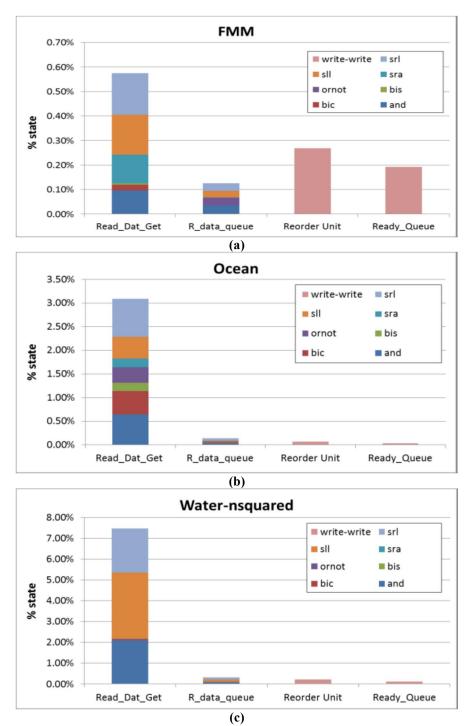

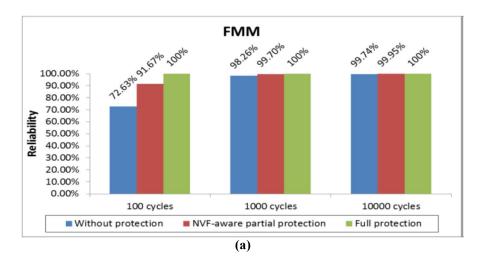

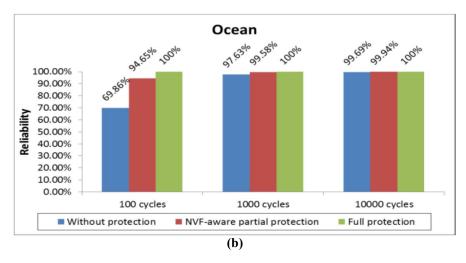

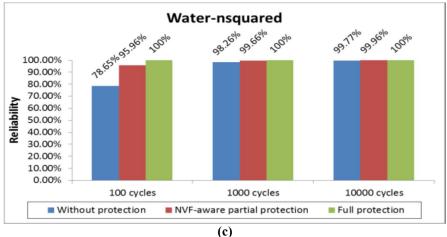

| Figure 45 Reliability vs fault rate for the three NI design approaches, across the benchmarks (a |

| FMM (b) Ocean (c) Water-Nsquared                                                                 |

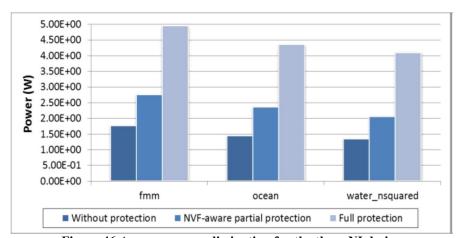

| Figure 46 Average power dissipation for the three NI design approaches across fmm, ocean, and    |

| water-nsquared benchmarks                                                                        |

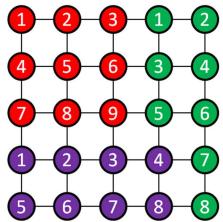

| Figure 47 Example of 5x5 mesh NoC with 3 applications mapped to three unique application         |

| islands 11                                                                                       |

| Figure 48 NoC router architecture with buffer protection                                 | 112      |

|------------------------------------------------------------------------------------------|----------|

| Figure 49 RESYN synthesis flow                                                           | 118      |

| Figure 50 Traditional crossover operation                                                | 120      |

| Figure 51 Experimental setup for RESYN synthesis flow                                    | 123      |

| Figure 52 Energy cost comparison for RESYN with unprotected and fully protected          | design   |

| alternatives                                                                             | 125      |

| Figure 53 Reliability comparison for RESYN with unprotected and fully protected          | design   |

| alternatives                                                                             | 125      |

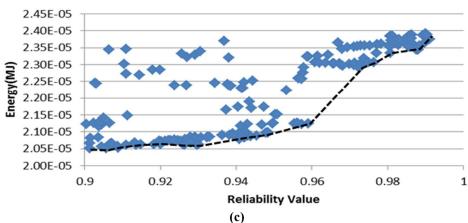

| Figure 54 Generated solution set using RESYN with Pareto front for the three application | ions (a) |

| ocean+fmm+water, (b) ocean+barnes+raytrace, (c) fft+barnes+cholesky                      | 127      |

| Figure 55 Multi-application core-to-die mapping example                                  | 130      |

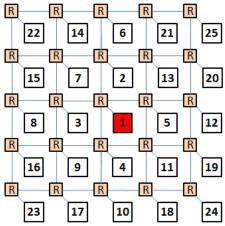

| Figure 56 Input/output NoC buffer protection control logic                               | 131      |

| Figure 57 Overview of HEFT synthesis framework                                           | 134      |

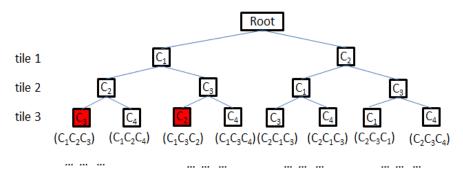

| Figure 58 Constrained search tree core mapping.                                          | 138      |

| Figure 59 Tile mapping pattern.                                                          | 139      |

| Figure 60 Block diagram of reliability prediction manager.                               | 144      |

| Figure 61 State machine for saturation counter based predictor                           | 144      |

| Figure 62 RPM parameter sensitivity analysis for solutions from the EACM mapping ap      | proach   |

|                                                                                          | 148      |

| Figure 63 Pareto front with and without protection by HEFT                               | 151      |

| Figure 64 Successful packet arrival rate comparison                                      | 154      |

| Figure 65 Normalized energy/reliability comparison                                       | 156      |

| Figure 66 Research summary                                                               | 159      |

#### **CURRICULUM VITAE**

#### **EDUCATION**

PhD. Candidate, 2014, Colorado State University, Fort Collins

Master, 2009, University of science and technology of China, China

Bachelor, 2005, Jilin University, China

#### **INTERNSHIP**

| 2014.6-2014.8   | Sv  | nonsvs  | Mountain     | view       | California |

|-----------------|-----|---------|--------------|------------|------------|

| 201 1.0 201 1.0 | U y | 110psys | IVIOUIILUIII | V 1 C VV 3 | Cullionina |

2011.5-2013.8 Broadcom corporation, Longmont, Colorado

2007.5-2009.3 Spreadtrum communication, Shanghai, China

### **PUBLICATIONS**

### **BOOK CHAPTERS:**

S. Pasricha, Y. Zou, "Hybrid Partially Adaptive Fault Tolerant Routing for 3D Networks-on-Chip", Embedded Systems: Hardware, Design, and Implementation, John Wiley & Sons, Inc., Hoboken, NJ, USA. doi: 10.1002/9781118468654.ch10, Nov 2012.

## JOURNAL PAPERS:

*J1*: Y. Zou, Y. Xiang, S. Pasricha, "Characterizing Vulnerability of Network Interfaces in Embedded Chip Multiprocessors", IEEE Embedded System Letters, 4(2), Jun 2012.

*J2:* Y. Zou, S. Pasricha, "NARCO: Neighbor Aware Turn Model Based Fault Tolerant Routing for NoCs", IEEE Embedded System Letters, Vol. 2, No. 3, Sep 2010.

*J3*: M. Oxley, S. Pasricha, A. A. Maciejewski, H. J. Siegel, J. Apodaca, D. Young, L. Briceno, J. Smith, S. Bahirat, B. Khemka, A. Ramirez and Y. Zou, "Makespan and Energy Robust Stochastic

Static Resource Allocation of Bags-of-Tasks to a Heterogeneous Computing System", accepted for publication, IEEE Transactions on Parallel and Distributed Systems, 2014.

*J4:* D. Young, J. Apodaca, L. Briceno, J. Smith, S. Pasricha, A. Maciejewski, H. Siegel, S. Bahirat, B. Khemka, A. Ramirez and Y. Zou, "Deadline and Energy Constrained Dynamic Resource Allocation in a Heterogeneous Computing Environment", Journal of Supercomputing, 2012.

#### **CONFERENCE PAPERS**

- C1: Y. Zou, S. Pasricha, "HEFT: A Hybrid System-Level Framework for Enabling Energy-Efficient Fault-Tolerance in NoC based MPSoCs", IEEE/ACM International Conference on Hardware/Software Codesign and System Synthesis (CODES-ISSS), Oct 2014.

- C2: Y. Zou, S. Pasricha, "Reliability-Aware and Energy-Efficient Synthesis of NoC based MPSoCs", IEEE International Symposium on Quality Electronic Design (ISQED), Mar. 2013.

- C3: Y. Zou, Y. Xiang, S. Pasricha, "Analysis of On-chip Interconnection Network Interface Reliability in Multicore Systems", IEEE International Conference on Computer Design (ICCD), Oct. 2011.

- C4: S. Pasricha, Y. Zou, "A Low Overhead Fault Tolerant Routing Scheme for 3D Networks-on-Chip", IEEE International Symposium on Quality Electronic Design (ISQED 2011), Santa Clara, CA, Mar 2011.

- C5: S. Pasricha, Y. Zou, "NS-FTR: A Fault Tolerant Routing Scheme for Networks on Chip with Permanent and Runtime Intermittent Faults", IEEE/ACM Asia & South Pacific Design Automation Conference (ASPDAC), Yokohama, Japan, Jan 2011.

- C6: S. Pasricha, Y. Zou, D. Connors, H. J. Siegel, "OE+IOE: A Novel Turn Model Based Fault Tolerant Routing Scheme for Networks-on-Chip", Proc. IEEE/ACM/IFIP International

Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), pp. 85-93, 2010.

C7: D. Young, J. Apodaca, L. Briceno, J. Smith, S. Pasricha, A. Maciejewski, H. Siegel, S. Bahirat, B. Khemka, A. Ramirez and Y. Zou, "Energy-Constrained Dynamic Resource Allocation in a Heterogeneous Computing Environment", Fourth International Workshop on Parallel Programming Models and Systems Software for High-End Computing (P2S2 2011), Sep 2011.

C8: J. Apodaca, D. Young, L. Briceno, J. Smith, S. Pasricha, A. Maciejewski, H. Siegel, S. Bahirat, B. Khemka, A. Ramirez and Y. Zou, "Stochastically Robust Static Resource Allocation for Energy Minimization with a Makespan Constraint in a Heterogeneous Computing Environment", ACS/IEEE International Conference on Computer Systems and Applications (AICCSA 2011), Dec 2011.

# CHAPTER 1 INTRODUCTION

This chapter will first describe the motivation of our research: why we chose NoC as the on-chip communication fabric and the need for fault-tolerant design for NoCs. Following the research motivation, a brief introduction will be given for the main research themes that we have pursued: fault-tolerant NoC routing algorithm design, 3D NoC interconnection architectures, NoC reliability modeling, and NoC system level reliability aware synthesis. Lastly, we summarize our research contributions in this thesis.

### 1.1 Motivation

# 1.1.1 Network-on-chip (NoC)

With CMOS technology aggressively scaling into the ultra-deep sub-micron (UDSM) regime and application complexity growing rapidly in recent years, processors today are being driven to integrate multiple cores on a chip. Such chip multiprocessor (CMP) architectures offer unprecedented levels of computing performance for highly parallel emerging applications in the era of digital convergence. Traditionally bus-based architectures have been used for CMP on-chip communication. Figure 1 shows a 22nm 15-core enterprise Xeon processor block diagram with a recent Intel Ivytown microarchitecture [7]. A ring bus is used for on-chip communication. Figure 2 shows the "AMBA" bus architecture which is widely used in mobile processors: A master starts the transaction by requesting access to central arbiter. An arbiter decides the priorities in case of access conflicts and allows the master to access the bus when the bus is ready. However, these bus-based communication architectures do not scale well with the increasing number of on-chip cores in terms of bandwidth, clocking frequency and power because of the contention in the single bus resource [2].

Figure 1 Block diagram and die diagram of Ivytown

Figure 2 AMBA bus-based system architecture

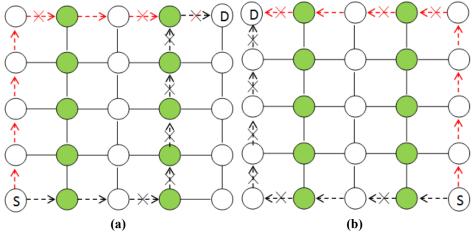

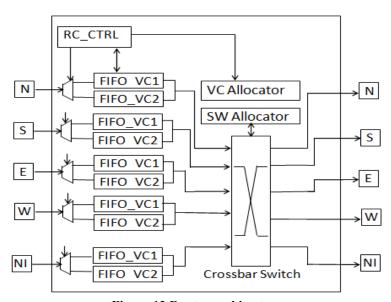

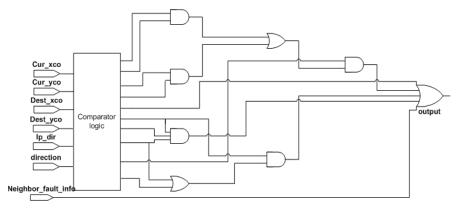

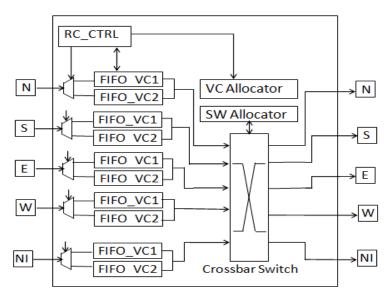

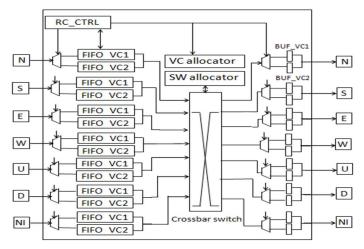

Network-on-Chip (NoC) fabrics have emerged as promising on-chip communication architecture candidates for chip multiprocessors (CMPs). NoCs have been shown to provide better scalability, predictability, and performance than bus-based communication architectures [1]. Figure 3 shows an Intel 256-core processor that has a 16×16 mesh NoC, with each of the 256 nodes having independent voltages and clocks, and a transfer throughput of 20.2 terabits per second between the nodes [8]. Routers in NoC fabrics play a key role in ensuring successful delivery of packets from the source to the destination node. Figure 4 shows a block diagram of a NoC router. When

a packet enters a router, it is first stored in the input buffers. Subsequently based on the destination information the route allocator (RA) will decide which output port the data will be sent to, virtual channel allocator (VA) will decide its virtual channel buffer, and switch allocator (SA) will reserve the necessary resources for the packet to be sent to the appropriately allocated output port buffer.

Figure 3 Die micrograph and measurement summary of Intel 256-node efficient network-on-chip

Figure 4 Virtual-channel NoC router block diagram [1]

In practice, NoC communication fabrics today still need to overcome two major challenges that are extremely relevant for emerging CMP applications. Firstly, packets switched NoCs must support low latency transfers between cores (especially for real-time applications) but are often unable to meet QoS (Quality of Service) guarantees. Using virtual circuit switching instead of packet switching allows for better QoS management, but unpredictable circuit setup delays still exist. Secondly, NoCs must enable low power data transfers. However, the large number of network interfaces, routers, links, and buffers that are part of the NoC fabric lead to a communication infrastructure that consumes a significant portion of the power from the overall CMP power budget [3][4][5]. In our research when we propose different fault-tolerant routing algorithms and reliability-aware system level synthesis solutions, minimizing communication energy and increasing NoC reliability are the two most important goals. At the same time, under the constraints of meeting the power budget and reliability goals, we provide solutions to improve the performance in terms of data delivery latency and throughput.

# 1.1.2 Fault tolerance in NoC

In the near future, a major challenge facing the designers of emerging multicore architectures is the increased likelihood of failure due to the rise in transient, permanent, and intermittent faults caused by a variety of factors that are becoming more and more prevalent with technology scaling. Transient faults (also called soft errors) occur when an event such as high-energy cosmic neutron particle strike, alpha particle strike due to trace uranium/thorium impurities in packages, capacitive and inductive crosstalk, or electromagnetic noise manifests itself. Such events cause the deposit or removal of enough charge to invert the state of a transistor, wire, or storage cell [9][10]. The inverted value may propagate to cause an error in program execution. These errors occur for a very short duration of time and can be hard to predict. Permanent faults occur due to

manufacturing defects, or after irreversible wearout damage due to electromigration in conductors, negative bias temperature instability (NBTI), dielectric breakdown, etc. [11][12]. A third class of faults, called intermittent faults, occur frequently and irregularly for several cycles, and then disappear for a period of time [13]. These faults commonly arise due to process variations combined with variation in the operating conditions (such as voltage and temperature fluctuations).

On-chip communication architectures are particularly susceptible to faults that can corrupt transmitted data or prevent it from reaching its destination [14]. Reliability concerns in UDSM nodes have in part contributed to the shift from traditional bus-based communication fabrics to network-on-chip (NoC) architectures that provide better scalability, performance, and utilization than buses [15][16]. The inherent redundancy in NoCs due to multiple paths between packet sources and sinks can greatly improve communication fault resiliency. Several multicore chip designs are emerging that make use of NoCs as interconnection fabrics [17]-[20]. To ensure reliable data transfers in these communication fabrics, utilizing fault-tolerant design strategies is essential. Traditionally, error detection coding and retransmission has been a popular means of achieving resiliency towards transient and intermittent faults [21][22]. Alternatively, forward error correction (FEC) schemes can provide better resiliency against these faults, but usually at a higher performance and energy overhead [23]. Circuit and layout optimizations such as shield insertion and wire sizing to reduce crosstalk induced transient faults have also been proposed [24][25]. To overcome permanent faults in NoCs, fault-tolerant routing schemes are also a critical requirement and the focus of several research efforts over the last few years [27]-[45]. In the presence of intermittent or permanent faults on NoC links and routers, routing schemes can ensure error free data flit delivery by using an alternate route that is free of faults.

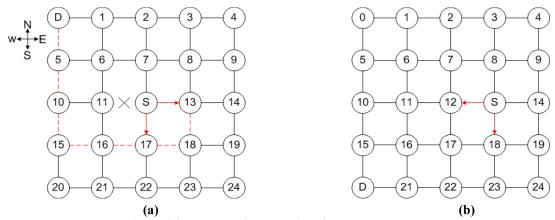

# 1.2 Fault-tolerant NoC routing

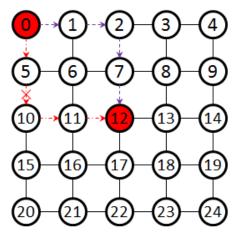

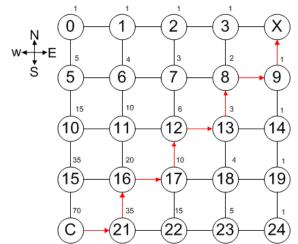

In our research, we only consider NoC with mesh topology, but all of our proposed research ideas can be applied to other NoC topologies as well. The inherent communication redundancy in NoCs due to multiple paths between packets sources and sinks can greatly improve communication fault resiliency. Figure 5 shows a 5×5 mesh NoC with each circle representing a router connected to a processing element. Each router is identified by a router id from 0 to 24. As can be seen, there are multiple paths from router 0 to router 12, so during the situation when the link between router 5 and 10 is broken, data can still be delivered from router 0 to router 12 via other routing paths.

Figure 5 Routing path diversity

Ideally packets should follow the minimal path from the source to destination node, which is why the simple XY routing scheme that routes packets first in the X direction and then in the Y direction is widely used in mesh-based NoCs. While the XY routing is popular because of its simplicity and communication efficiency, it is static in nature and does not possess any adaptivity or fault resiliency to cope with situations where there are faults inside the network. Different adaptive routing algorithms have been proposed in literature to overcome this drawback. But there can be many potential problems due to the introduction of adaptive routing.

Firstly, traffic unbalancing due to adaptive routing can lead to congestion and communication performance degradation. In our routing algorithm research, when adaptively choosing a routing path to avoid errors in a link or router, we also try to balance the traffic to minimize traffic congestion. Secondly, an inevitable issue from adaptive routing is deadlock or livelock [1]. In our research we build on the turn model routing scheme because of its deadlock and livelock free different properties and extend it to situations to cope with potential permanent/intermittent/transient faults in the on-chip network. Last but not least, complex routing algorithms can introduce excessive area and energy overhead. In all of our proposed routing schemes, we set our design goal as minimizing energy, area, and power overhead while maximizing performance in terms of latency and reliability in term of successful packet delivery rate.

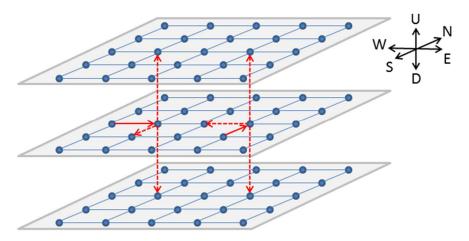

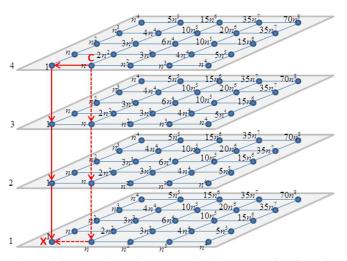

#### 1.3 3D NoC interconnection

Advances in CMOS fabrication technology in recent years have led to the emergence of chip multiprocessors (CMPs) as compact and powerful computing paradigms. However, to keep up with rising application complexity, it is widely acknowledged that solutions beyond aggressive CMOS scaling into deeper nanometer technologies will be required in the near future, to improve CMP computational capabilities [6]. 3D integrated circuit (3D-IC) technology with wafer-to-wafer bonding [51][52] has been recently proposed as a promising candidate for future CMPs. In contrast to traditional 2D-IC based chips that have a single layer of active devices (processors, memories), wafer-to-wafer bonded 3D-ICs consist of multiple stacked active layers and vertical Through Silicon Vias (TSVs) to connect the devices across the layers. Multiple active layers in 3D-ICs can enable increased integration of cores within the same area footprint as traditional 2D-ICs. In addition, long global interconnects between cores can be replaced by shorter inter-layer

TSVs, improving performance and reducing on-chip power dissipation. Recent 3D-IC test chips from IBM [51], Tezzaron [52], and Intel [3] have confirmed the benefits of 3D-IC technology. A major challenge facing the design of such highly integrated 3D-ICs in deep submicron technologies is the increased likelihood of failure due to permanent and intermittent faults caused by a variety of factors (e.g., misalignment of 3D dies, inter-layer crosstalk) that are becoming more and more prevalent. On-chip communication architectures are particularly susceptible to faults that can corrupt transmitted data or altogether prevent it from reaching its destination. Reliability concerns in sub-65nm nodes have in part contributed to the shift from traditional busbased communication fabrics to network-on-chip (NoC) architectures that provide better scalability, predictability, and performance than buses [16][53]. The inherent redundancy in NoCs due to multiple paths between packet sources and sinks can greatly improve communication error resiliency. It is expected that 3D-ICs will employ 3D NoCs, much like todays 2D-IC based CMPs are employing 2D NoCs [3][19][54]. To ensure reliable data transfers in these communication fabrics, utilizing fault-tolerant design strategies is essential. In particular, fault-tolerant routing schemes are critical to overcome permanent and intermittent faults at design time as well as runtime. In the presence of intermittent or permanent faults on NoC links and routers, routing schemes can ensure error free data flit delivery by using an alternate route that is free of faults. As a result, fault-tolerant routing schemes for 2D NoCs have been the focus of several research efforts over the last few years [13]-[25]. However, to the best of our knowledge, no prior work has yet explored fault-tolerant routing schemes for 3D NoCs. In our research, for the first time, we explore and proposel effective techniques for fault-resilient 3D NoC routing.

## 1.4 NoC reliability modeling

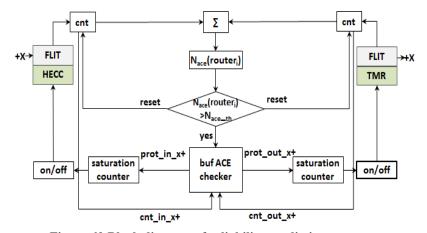

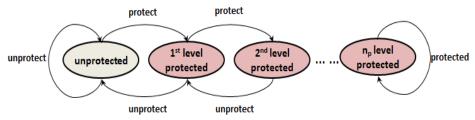

Chip designers typically set a failure rate target for each design and strive to maximize performance subject to this constraint. To validate that a design meets the failure rate target, designers perform extensive pre- and post-silicon analysis. This analysis measures the rate at which faults occur in a system as well as whether a given fault will cause a system failure. Designers then make use of one of several well-known techniques to improve reliability in the presence of soft errors, such as triple modular redundancy (TMR) and error correction/detection coding schemes. However, these techniques come with extra overhead in terms of area, power, and even performance, and therefore must be used judiciously.

Fortunately, not all faults eventually affect the final program outcome. For example, a bit flip in an empty translation lookaside buffer (TLB) entry will not cause any effect in the program execution. Based on this observation, Mukherjee et al. [55] defined a structure's Architectural Vulnerability Factor (AVF) as the probability that a transient fault in the structure finally produces a visible error in the output of a program. At any point of time, a structure's AVF can be derived by counting all the important bits that are required for Architecturally Correct Execution (ACE) in the structure, and dividing them by the total number of bits of the structure. Such ACE analysis has been used to derive an upper bound on AVF using performance simulation for intra-processor buffers [55]-[57] and cache structures [58] in recent years.

In our research, we use the idea of AVF and extend AVF from the microprocessor domain and propose a network vulnerability factor (NVF) metric to characterize the susceptibility of NoC components. Specially, we analyze the vulnerability factor of network interface and the router in NoC so that we can quantify the reliability of these components and make protection decisions. Our studies reveal that different network interface (NI) and router buffers behave quite

differently on transient faults and each buffer can have different levels of inherent fault-tolerant capabilities.

## 1.5 NoC system level reliability aware synthesis

As power and energy costs have become essential constraints during chip design, a systematic design methodology is required to balance reliability measures and their associated power/energy costs. This is a synthesis problem that impacts many phases of a CMP design flow, such as coreto-die mapping, NoC router configuration, NoC routing algorithm selection, etc.

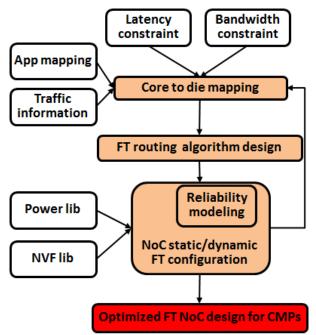

Figure 6 Reliability aware NoC synthesis framework

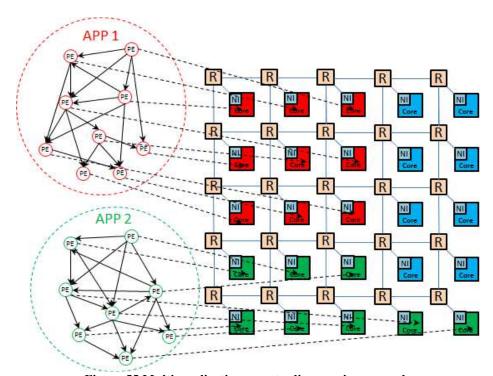

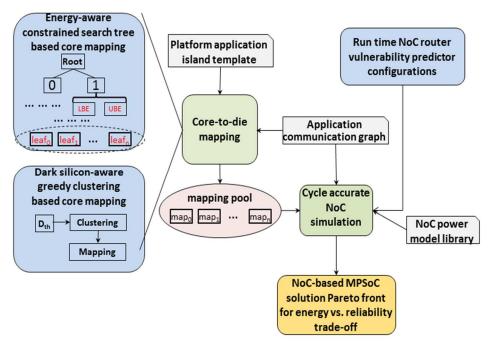

The ultimate goal of our research is to find a holistic fault-tolerant design for NoC communication fabrics in CMPs. As shown in Figure 6, in our research we want to find a mapping of cores to the 2D mesh-based die that meets application communication latency constraints and also configure (synthesize) the NoC fabric for the entire chip by customizing NoC routers at each node with appropriate protection mechanisms to meet a designer-specified reliability goal while minimizing energy consumption.

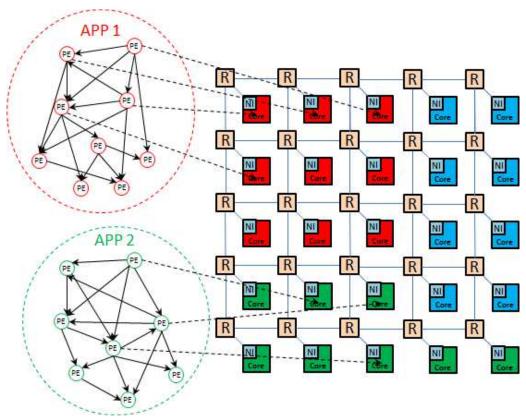

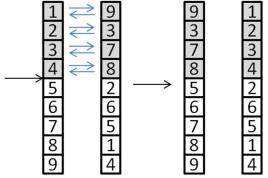

Figure 7 Core to tile mapping

Figure 7 shows an example of mapping each core in an application communication graph (ACG) to a CMP with a 2D mesh topology based NoC fabric. ACG is a directed graph, in which each vertex  $C_i \in V$  represents an IP core (processor or memory), and each directed edge  $comm_{ij} \in E$  represents communication dependencies between the source core  $C_i$  and destination core  $C_j$ . The volume of communication from  $C_i$  to  $C_j$  is  $v(comm_{ij})$  and  $v(C_i) = \sum_{j \in V} (v(comm_{ij}) + v(comm_{ji}))$ . Each edge  $comm_{ij}$  has a weight  $B(comm_{ij})$  for application-specific communication bandwidth constraints, and a weight  $L(comm_{ij})$  for latency constraints (maximum number of hops allowed between cores  $C_i$  and  $C_j$ ), We assume that the designer can pre-define application zones on the mesh-based die, as shown in Figure 7, allowing multiple applications to co-execute on the

regular CMP die. In general, communication occurs at an intra-application node level, i.e., only between nodes belonging to an application, and not between nodes of different applications. For a given NoC link width (e.g., 32 bits), we assume platform constraints related to the maximum bandwidth that the NoC links can support  $B_{link}$ , which is dependent on the CMOS technology node and chip power constraints. Thus, for all mapped cores utilizing a link, it is required that the total utilized bandwidth on that link  $T_{link\_max} \le B_{link}$ .

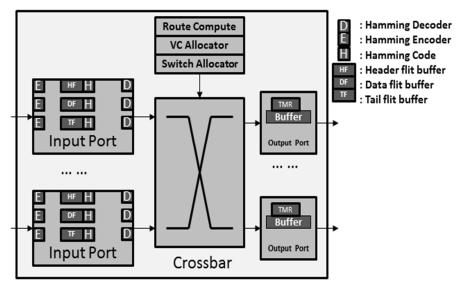

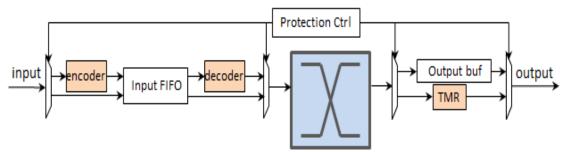

The buffers in NoC routers are most susceptible to transient single event upset (SEU) errors, and we assume that errors on the relatively small footprint inter-router links are negligible. To protect NoC router buffers against SEU errors, we can employ two widely-used protection mechanisms: Hamming Error Correction Codes (HECC) and replicating components with Triple Modular Redundancy (TMR). Both mechanisms can correct SEU errors. But unlike TMR, HECC operation entails additional latency to encode and decode data. On the other hand, TMR implementations possess a larger area and power footprint than HECC. Table 1 shows the average power, latency, and area overhead trends for using either only HECC or only TMR to protect all buffers inside a NoC router, compared to a baseline NoC router without any protection. Results are obtained using an RTL model of a five staged pipelined NoC router that was enhanced with HECC and TMR protection mechanisms, and taken through logic synthesis using Synopsis tools and layout for a 45nm TSMC library.

Table 1 HECC vs. TMR overhead comparison

|                  | HECC | TMR  | Integrated |

|------------------|------|------|------------|

| Power overhead   | 8%   | 259% | 12%        |

| Latency overhead | 150% | 10%  | 75%        |

| Area overhead    | 5%   | 200% | 7%         |

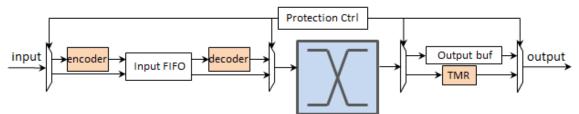

It is apparent that using only HECC or TMR has high associated penalties. To minimize these overheads, we chose to judiciously combine HECC and TMR in a NoC router, by protecting

input FIFO buffers (that can store multiple flits) in NoC routers with HECC due to its lower area and power overhead, and protecting the smaller output NoC buffers (that only store a single flit) using TMR to minimize latency overhead. This integrated HECC/TMR configuration, shown in Figure 8 and whose overheads are shown in the last column of Table 1 ("Integrated"), results in a relatively fast packet traversal with a reasonable area and power overhead.

Figure 8 Router fault-tolerant configuration

But even in such a NoC router configuration, protecting all the buffers in all NoC routers on the die can lead to excessive power dissipation and latency overhead. There is an opportunity to further reduce power and latency by intelligently determining an appropriate subset of buffers for protection against SEUs in the NoC routers. To this end, we require a selective protection methodology, to best match the time-varying behavior of an application, and optimally reduce the cost of enabling fault tolerance in NoCs. Our research proposes intelligent mechanisms to perform such optimization.

#### 1.6 Contribution

In this thesis, our contribution to the area of fault-tolerant NoC design encompasses three main topics:

• Fault-tolerant routing algorithm design which utilizes the path diversity in NoCs to achieve fault resilient transfers. The goal is to minimize the communication energy overhead and improving the packets' successful delivery rate, at the same time the proposed routing algorithms should be deadlock/livelock free.

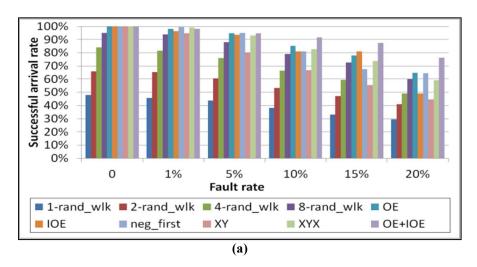

- First, we proposed a novel fault-tolerant routing scheme (OE+IOE) for 2D mesh-based NoCs that can adapt to design-time and runtime permanent link faults, as well as potential intermittent faults in NoC communication architectures. Our scheme uses replication opportunistically based on the fault rate, and combines the odd-even (OE) and inverted odd-even (IOE) turn models to achieve deadlock free packet traversal. Experimental results show that our proposed OE+IOE scheme can provide better fault-tolerant ability (i.e., higher successful packet arrival rates) than traditional fault-tolerant routing schemes such as N-random walk.

- neighbor-aware turn model based fault-tolerant routing scheme (NARCO) for NoCs in embedded systems, which combines threshold based replication, a parameterizable region based neighbor awareness in routers, and the odd-even and inverted odd-even turn models. The proposed scheme enables a better packet arrival rate than state of the art of existing fault-tolerant routing schemes, while enabling a trade-off between communication reliability and energy overhead.

- By exploring more types of routing algorithms we propose a novel fault-tolerant routing scheme (NS-FTR) for NoCs that combines the North-last and South-last turn models to create a robust hybrid NoC routing scheme. The proposed scheme is shown to have a low implementation overhead and to adapt to design time and runtime faults better than the existing turn models, stochastic random walk schemes, and dual virtual channel based routing schemes such as XYX and OE+IOE.

- We then extend the hybrid routing algorithm approach for 3D NoCs and propose a novel fault-tolerant routing scheme (4NP-First) for 3D NoCs that combines the 4N-First and 4P-

First turn models to create a robust hybrid routing scheme. The proposed scheme is shown to have a low implementation overhead and adapts to design-time and runtime faults better than existing turn models, stochastic random walk schemes, and hybrid dual virtual channel based routing schemes.

- Reliability modeling based on our network vulnerability factor metric with which we quantify NoC reliability so that we can balance the energy and reliability. For the first time, a detailed characterization of vulnerability was performed on an AXI-based network interface (NI) architecture using full system simulation with consideration of thermal throttling, to determine the probabilities that faults in NI components manifest as errors in the final program output of the CMP. The resulting characterization can aid in the design of NI architectures possessing high reliability and low power dissipation overhead, using NVF-based opportunistic protection.

- NoC system level synthesis which is a holistic problem that includes the core to tile

mapping, on-chip routing, and router fault tolerance design.

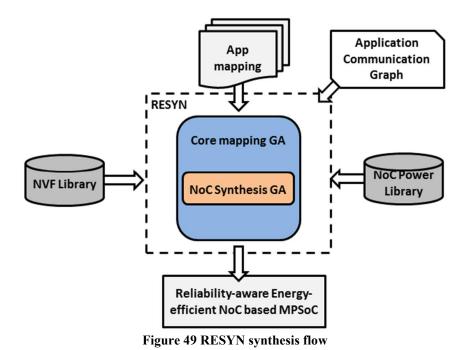

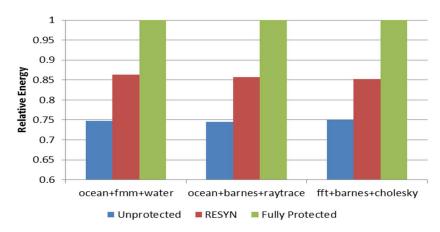

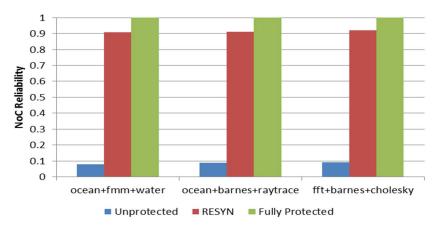

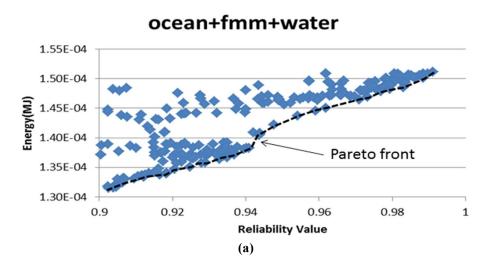

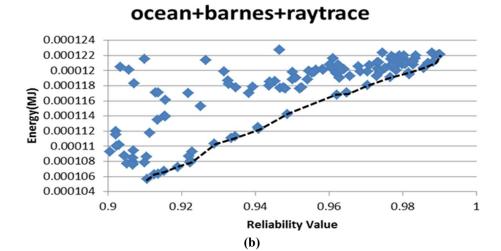

- First, we proposed a novel design-time framework (RESYN) to trade-off energy consumption and reliability in NoC-based CMPs. RESYN employs a nested genetic algorithm (NGA) approach to guide the mapping of cores on a die, and opportunistically determines the locations to insert fault tolerance mechanisms in NoC routers to minimize energy consumption while satisfying reliability constraints. Our experimental results show that RESYN can reduce communication energy costs by 14.5% on average compared to a fully protected NoC design, while still maintaining more than a 90% fault tolerance. RESYN also enables a comprehensive trade-off between reliability and energy-efficiency for more stringent reliability constraints, generating a Pareto set of solutions which may reveal

opportunities for energy savings even for high reliability configurations; e.g., for a higher 95% reliability constraint, a notable 13% energy savings can still be achieved for some applications. Given the increasing importance of reliability in the nanometer era for NoC-based CMPs, this framework provides important perspectives that can guide the reduction of energy overheads associated with reliable NoC design.

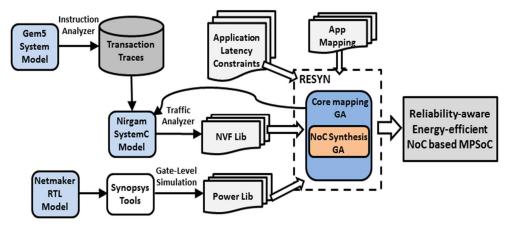

Second by considering NoC communication runtime information such as traffic congestion distribution and congestion patterns, we proposed a system-level framework called HEFT to trade-off energy consumption and fault-tolerance in the NoC fabric. Our hybrid framework tackled the challenge of enabling energy-efficient resilience in NoCs in two phases: at design time and at runtime. At design time, we implemented algorithms to guide the robust mapping of cores onto a die while satisfying application bandwidth and latency constraints. At runtime we devised a prediction technique to monitor and detect changes in fault susceptibility of NoC components, to intelligently balance energy consumption and reliability. Experimental results show that HEFT improves the energy/reliability ratio of synthesized solutions by 8-20%, while meeting application performance goals, when compared to prior work on reliable system-level NoC design. Given the increasing importance of reliability in the deep nanometer era for CMPs, our framework provides an important tool that can guide the reduction of energy overheads associated with reliable NoC design.

#### 1.7 Thesis outline

The research presented in this thesis is organized as follows. Chapter 2 surveys recent literature in the domains of NoC fault-tolerant routing algorithm design, NoC reliability modeling, and NoC reliability aware synthesis. Chapter 3 lists our proposed fault-tolerant routing algorithms with the goal of minimizing energy, area overhead and at the same time optimizing the latency

and reliability in terms of successful packet delivery rates. Chapter 4 describes our proposed reliability model based on the network vulnerability factor (NVF) metric for NoC communication subsystems. In Chapter 5, we propose two system-level frameworks, RESYN and HEFT, to trade-off energy consumption and fault-tolerance in the NoC fabric by exploring different core to tile mapping, routing algorithms and fault-tolerant NoC protection configuration strategies. RESYN explores an offline router protection strategy while HEFT contains both offline and online strategies for NoC synthesis. Chapter 6 summarizes the conclusion of this thesis and lists some directions for future work.

# CHAPTER 2 LITERATURE SURVEY

In general our research focuses on three main topics related to fault-tolerant NoC design: fault-tolerant NoC routing, NoC reliability modeling and NoC reliability aware synthesis. This chapter discusses the advantages and drawbacks of the most influential existing research work in literature in each of these three areas.

# 2.1 Fault-tolerant NoC routing

On-chip interconnect architectures are particularly susceptible to faults that can corrupt transmitted data or prevent it from reaching its destination [14]. Reliability concerns in UDSM nodes have in part contributed to the shift from traditional bus-based communication fabrics to network-on-chip (NoC) architectures that provide better scalability, performance, and utilization than buses [15][16]. The inherent redundancy in NoCs due to multiple paths between packet sources and sinks can greatly improve communication fault resiliency. To overcome permanent faults in NoCs, fault-tolerant routing schemes are a critical requirement and the focus of several research efforts over the last few years [27]-[45]. In the presence of intermittent or permanent faults on NoC links and routers, routing schemes can ensure error free data flit delivery by using an alternate route that is free of faults.

NoC routing schemes can be broadly classified as either static (also called deterministic) or dynamic (also called adaptive). While static routing schemes [1][26] use fixed paths and offer no fault resiliency, dynamic (or adaptive) routing schemes [27]-[45] can alter the path between a source and its destination over time as traffic conditions and the fault distribution changes. The design of adaptive routing schemes is mainly concerned with increasing flit arrival rate, avoiding deadlock, and trying to use a minimal hop path from the source to the destination to decrease

transmission energy. Unfortunately, these goals are often conflicting, requiring a complex tradeoff analysis that is rarely addressed in existing literature.

More specifically, fault-tolerant routing schemes can be functionally classified into three categories: (i) stochastic, (ii) fully adaptive, and (iii) partially adaptive.

Stochastic routing algorithms provide fault tolerance through data redundancy by replicating packets multiple times and sending them over different routes [27]. For instance, the probabilistic gossip flooding scheme [28] allows a router to forward a packet to any of its neighbors with some pre-determined probability. Directed flooding refines this idea by preferring hops that bring the packet closer to its addressed destination [29]. N-random walk [29] limits the number of packet copies by allowing N replications at the source only. In the rest of the network, these copies stochastically take different routes without further replication. The major challenges with these approaches are their high energy consumption, strong likelihood of deadlock and livelock, overhead of calculating, storing, and updating probability values, and poor performance even at low traffic congestion levels.

Fully adaptive routing schemes make use of routing tables in every router or network interface (NI) to reflect the runtime state of the NoC and periodically update the tables when link or router failures occur to aid in adapting the flit path. For instance, [30] proposes using source routing, with routing tables stored at NIs instead of in the routers. But the scheme is only useful for design time faults and cannot adapt to runtime faults. In [31][32], routing tables are used in every router to determine the best path to take in the presence of faults at runtime in mesh topologies. There are several issues with these approaches that prevent their widespread use. First, these schemes require that the routing schemes be updated with global fault and route information frequently, which can take hundreds to thousands of cycles at runtime during which the network

state is unstable. In addition, obtaining a global view of the system may not be practically feasible from an energy and performance point of view. Second, the cost and scalability of these schemes can make them prohibitive. As the size of the NoC grows, the table sizes also increase rapidly, increasing router (or NI) area, energy, and latency. Finally, deadlock is a strong possibility that can bring the entire system to a halt, unless high ooverhead deadlock recovery mechanisms such as escape channels or distributed timeout counters are used.

Partially adaptive routing schemes enable a limited degree of adaptivity, placing various restrictions and requirements on routing around faulty nodes, primarily to avoid deadlocks. Turn model based routing algorithms such as negative-first, north-last, and south-last [33]-[36] are examples of partially adaptive routing, where certain flit turns are forbidden to avoid deadlock. The odd-even (OE) turn model [36] classifies columns in a mesh topology as either odd or even and prevents different turns in the odd and even columns to prevent cyclic dependencies that can cause deadlocks. In [29], the XY and YX schemes are combined to achieve fault resilient transfers. In [38], routing tables are combined with a customized turn model to avoid deadlock. The work is primarily aimed at design time permanent faults. Unfortunately, the degree of adaptivity provided by these routing algorithms is highly unbalanced across the network, which in some cases results in poor performance.

A few works have proposed using convex or rectangular fault regions with turn models [39]-[45]. Routing detours around these regions can be selected so that deadlock-prone cyclic dependencies are impossible, such as by using turn models or cycle free contours. For instance, [40] builds a fault ring around faults and introduces rules to route flits around the fault region to avoid deadlock. But the scheme can only handle design time permanent faults (i.e., fault regions are built only at design time and cannot handle runtime faults) and also requires up to four VCs,

which can quickly become cost ineffective as the NoC size scales. In [41], the OE turn model was used together with fault regions. However, the work was based on assumptions that no fault exists in the two columns that are adjacent to the west and east edges of the mesh. In general, fault-tolerant routing schemes that make use of fault regions are either too conservative (disabling fully functional routers to meet region shape requirements), have restrictions on the locations of the faults that can be bypassed, or cannot adapt to runtime intermittent and permanent faults.

#### 2.2 NoC reliability modeling

A major challenge facing the designers of NoC architectures is the increased likelihood of failure due to the rise in transient faults (or soft errors). Such faults are caused by a variety of factors (e.g., high-energy cosmic neutron or alpha particle strikes, capacitive and inductive crosstalk) that are becoming more and more prevalent with the exponential growth rate of on-chip transistors, along with lower supply voltage and increasing clock frequency. Soft errors cause the deposit or removal of enough charge to invert the state of a transistor, wire, or storage cell, which can lead to catastrophic system failure [9]. Techniques to ensure fault tolerance have thus become a critical design concern in recent CMP designs. Chip designers typically set a failure rate target for each design and strive to maximize performance subject to this constraint. To validate that a design meets the failure rate target, designers perform extensive pre- and post-silicon analysis. This analysis measures the rate at which faults occur in a system as well as whether a given fault will cause a system failure. Designers then make use of one of several well-known techniques to improve reliability in the presence of soft errors, such as triple modular redundancy (TMR) and error correction/detection coding schemes. However, these

techniques come with extra overhead in terms of area, power, and even performance, and therefore must be used judiciously.

Fortunately, not all faults eventually affect the final program outcome. For example, a bit flip in an empty translation lookaside buffer (TLB) entry will not cause any effect in the program execution. Based on this observation, Mukherjee et al. [55] defined a structure's Architectural Vulnerability Factor (AVF) as the probability that a transient fault in the structure finally produces a visible error in the output of a program. At any point of time, a structure's AVF can be derived via counting all the important bits that are required for Architecturally Correct Execution (ACE) in the structure, and dividing them by the total number of bits of the structure. Such ACE analysis has been used to derive an upper bound on AVF using performance simulation for intra-processor buffers [55]-[57] and cache structures [58] in recent years.

There are two main approaches to calculate AVF values: ACE analysis and Statistical Fault Injection (SFI). The former provides a (tight, if the underlying system is appropriately modeled [63]) lower bound on the reliability level of various processor structures, and has been adopted in many research works on performance models. Fu et al. [57] quantitatively characterized vulnerability phase behavior of four processor microarchitecture structures based on a system framework proposed in [56]. Zhang et al. [64] performed a similar analysis on SMT architectures. Soundararajan et al. [65] described a simple infrastructure to estimate an upper bound of the processor reorder buffer AVF, and also proposed two mechanisms (Dispatch Throttling and Selective Redundancy) to restrict the vulnerability to any limit. Sridharan at el. decomposed AVF into two parts: a software-dependent portion and a hardware-dependent portion, known as Program Vulnerability Factor (PVF) [66] and Hardware Vulnerability Factor

(HVF) [67], respectively. Biswas et al. measured AVF for L2 cache structures [58]. None of these prior works has explored vulnerability for components of NoC communication fabrics. Several works have addressed the problem of making NoC fabrics more reliable. For instance, Kim et al. [61] explored error correction/detection and retransmission techniques to handle errors in links and router logic. More specifically for router buffers, Yu et al. [68] proposed using Hamming codes while Frantz et al. [69] proposed using TMR together with Hamming codes to address errors. Chang et al. [70] proposed using spare routers to handle NoC router failure at runtime. Pasricha et al. [59] presented a hybrid turn model based fault-tolerant routing algorithm that adapts to faults at runtime on NoC links and routers. Refan et al. [60] proposed adding spare links from each core to its neighboring router, to allow packets to bypass failed switches. None of these existing works attempt to understand the underlying vulnerability of NoC components to guide efforts that improve reliability.

In our research, for the first time, we introduce the concept of a network vulnerability factor (NVF) to quantify and model reliability and then perform a detailed NVF analysis for sub-components in a state-of-the-art AXI protocol based NI architecture, using full system simulation, to understand masking effects and determine the probabilities that faults in NI sub-components manifest as errors in the final program output in a CMP system.

# 2.3 NoC reliability aware synthesis

Tradition system level synthesis for NoC can involve many design sub-problems such as core-to-tile mapping, routing algorithm design, task mapping/scheduling, etc. The problem of synthesizing NoC communication architectures has been addressed extensively in literature. Some of the more comprehensive efforts also perform mapping of cores to a die, which can significantly improve communication power dissipation and latency, by optimizing the flow of

traffic between cores. Here we briefly present some representative examples of prior work in the area.

In [87], Ye et al. propose a model for energy consumption of NoC routers called "bit energy model" that defines the energy consumption for one bit of data transfer through a NoC router and link. Using this bit energy model, In [82], a branch and bound algorithm is proposed to map processing cores on to a mesh NoC to satisfy bandwidth constraints and minimize total energy consumption. In [83], Hu et al. proposed a multi-commodity flow based scheme to optimize NoC power consumption by customizing the topology and packet routes. In [98], Srinivasan et al. use a slicing tree algorithm to search the core mapping space and arrive at a mapping that adheres to latency constraints with the goal of minimizing energy. In [14], Chou et al. introduce a traffic contention aware core mapping algorithm using integer linear programming. In [84], Leung et al. focus on NoC implementations with voltage islands and use a genetic algorithm (GA) to find an energy-aware voltage island partitioning and assignment solution. In [79], Ascia et al. analyze and evaluate the performance of different mapping solutions in a mesh NoC topology and solve the power-performance multi-objective mapping problem with a heuristics based on GA and branch-and-bound. In [80], Murali et al. present a greedy core-to-die mapping heuristic for a regular NoC-based MPSoC die, based on communication volumes emanating from each core. Their approach also searches different routing paths to balance NoC traffic and meet bandwidth constraints, but it does not include energy cost as an optimization goal. None of the existing techniques performs core-mapping and NoC synthesis together with reliability goals, nor do they attempt to trade-off reliability with energy.

Due to reliability becoming an increasingly important goal for NoC design, some recent efforts are considering reliability as part of an overall optimization objective. In [99], Aisopos et al. use

Monte Carlo simulations to model process variations and calculate reliability values for circuits. In [29], Pirretti et al. use a successful data delivery rate metric to quantify reliability and evaluate the fault tolerance of their NoC routing algorithms. In [96], Ababei et al. define the reliability of a NoC based on the path lengths between communicating cores on the die. They use this reliability model and use the core-to-die mapping framework from [95] to balance NoC reliability and energy costs.

In our research, we propose a novel design-time framework (RESYN) and a hybrid design/run time framework (HEFT) to trade-off energy consumption and reliability in the NoC fabric at the system level for CMPs that improves upon these prior efforts.

# CHAPTER 3 FAULT-TOLERANT ROUTING ALGORITHM DESIGN

In this chapter we propose different low overhead fault-tolerant routing schemes for 2D and 3D NoC mesh topology. Our goal is to achieve better fault tolerance than existing routing algorithms in the presence of different types of faults in the NoC; at the same time we want to minimize the energy cost of routing.

# 3.1 OE+IOE fault-tolerant routing scheme

In this section, we present our novel low overhead fault-tolerant routing scheme (OE+IOE) that combines the odd-even (OE) and inverted odd-even (IOE) turn model based routing schemes to achieve better fault tolerance than existing fault-tolerant routing schemes. The target topology for the scheme is the 2D mesh, which is the most popular interconnection topology in NoCs today because of its layout efficiency, predictable electrical properties, and simple core addressing. The proposed scheme uses replication and dual virtual channels (VCs) at ports opportunistically to optimize the balance between energy overhead and flit arrival rate.

# 3.1.1 OE and inverted OE turn models

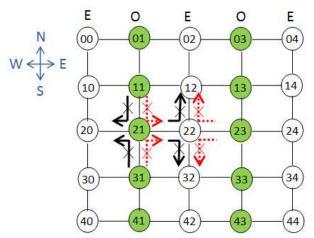

The odd-even (OE) turn model for deadlock-free routing in 2D meshes was introduced by Chiu [36]. A turn in this context refers to a 90-degree change of traveling direction for a flit. There are eight types of turns that are possible in a 2D mesh based on the traveling directions of the associated channels. To facilitate the explanation, we label the four sides of the 2D mesh as East, West, South, and North (Figure 9). Then a turn is called a NE turn if it involves a flit traveling in the North direction and attempting to turn East. Similarly, we can define the other seven types of turns, namely EN, WS, WN, SE, SW, ES, and NW turns, where E, W, S, and N indicate East, West, South, and North, respectively.

Figure 9 OE and IOE prohibited turns based on column; black arrows indicate prohibited turns in OE, while red arrows indicate prohibited turns in IOE

Deadlock in wormhole routing is caused by flits waiting on each other in a cycle. Unlike traditional turn models [1] that avoid deadlock by prohibiting certain turns, the OE turn model restricts the locations at which certain turns can occur to ensure that a circular wait does not occur. In OE turn model based routing, columns in a 2D mesh are alternately designated as odd (O) and even (E), as shown in Figure 9 for a 5×5 2D mesh. Then the following two forbidden turn rules ensure cycle- and deadlock-free routing: (i) a packet is not allowed to take an EN or ES turn at any node located in an even column; and (ii) a packet is not allowed to take a NW or SW turn at any node located in an odd column. A deadlock-free minimal path route can then be found for any source destination pair as described in [36], and we refer the reader to that paper for details. The prohibited turns for the OE turn model are depicted in black in Figure 9. No other restrictions need to be applied to ensure freedom from deadlock. The inverted odd-even (IOE) turn model can be understood by rotating the mesh by 180 degrees, while preserving the oddeven column designations and corresponding prohibited turns. Figure 9 shows the prohibited turns in the odd and even columns for the IOE turn model in red, which are required to ensure deadlock free operation.

# 3.1.2 OE+IOE routing scheme: overview

To ensure robustness against faults, redundancy is a necessary requirement, especially for environments with high fault rates and unpredictable fault distributions. As the level of redundancy is increased, system reliability improves as a general rule. However, redundancy also detrimentally impacts other design objectives such as power and performance. Therefore in practice it is important to limit redundancy to achieve a reasonable trade-off between reliability, power, and performance. Unlike directed and random probabilistic flooding algorithms that propagate multiple copies of a packet to achieve fault-tolerant routing in NoCs, the proposed OE+IOE routing algorithm sends only one redundant packet for each transmitted packet, and only if the fault rate is above a replication threshold  $\delta$ . The value of  $\delta$  is a designer-specified parameter that depends on the application characteristics, routing complexity, and powerreliability trade-off requirements. The original packet is sent using the odd-even (OE) turn model while the redundant packet is propagated using an inverted odd-even (IOE) turn model based routing scheme. This packet replication happens only at the source. Two separate VCs, one dedicated to the OE packets and the other for the IOE packets ensure deadlock freedom. If the fault rate is low (i.e., below  $\delta$ ), replication is not utilized and only the original packet is sent using the OE scheme while power/clock gating the IOE virtual channel to save power. The proposed routing algorithm prioritizes minimal paths that have higher probabilities of reaching the destination even if faults are encountered downstream. Minimal paths and the replication threshold ensure low power dissipation under a diverse set of fault rates and distributions. No restriction on the number or location of faults is assumed, but the routers must know which of their adjacent (neighbor) links/nodes are faulty, which is accomplished using minimal control signaling. The proposed routing approach can be combined with error control coding (ECC)

techniques for transient fault resiliency and optimizations such as router buffer reordering [46] and router/NI backup paths [47] to create a comprehensive fault-tolerant NoC fabric. In the following subsections, we describe the implementation of the proposed OE+IOE routing scheme.

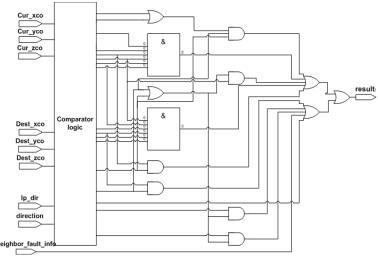

3.1.2.1 Turn restriction checks

Whenever a packet arrives at a router in the OE+IOE scheme, three scenarios are possible: (i) there is no fault in the adjacent links and the packet is routed to the output port based on the OE (or IOE) scheme that selects a minimal path to the destination, (ii) there are one or more faults on adjacent links that prevent the packet from propagating in a valid direction (i.e., an output port with a fault-free adjacent link that does not violate turn model routing rules) in which case the packet must be dropped as a back turn is not allowed, and (iii) one or more adjacent links have faults but a valid direction exists to route the packet towards, based on the OE (or IOE) rules. A packet traversing an intermediate router must choose among four output directions (N, S, W, E). However, choosing some directions may lead to a violation of a basic OE (or IOE) turn rule immediately or downstream based on the relative location of the destination. Figure 10 shows the SystemC [48] pseudocode of the turn restriction check phase for the OE turn model in our router model to aid in detecting an invalid routing direction. The reference to XY coordinates follows the convention as shown in Figure 9 where each node is labeled with its XY coordinates. Note that the pseudocode for the IOE scheme is similar with the directions inverted, and is not shown here for brevity.

First, we check whether the output port direction has a fault in its attached adjacent link (Steps 2-4), in which case this is an invalid direction. Next, we check the forbidden turn rules for the OE turn model as discussed in Section 3.1 (Steps 5-10) based on the router location (in an odd or even column), the input port of the packet, and its output port direction. If the packet is

attempting a forbidden turn, then the direction is invalid. If the direction has no adjacent faults and does not violate the basic OE routing rules, we then check if the direction will lead to a turn rule violation downstream based on the location of the destination. We start by checking for the scenario when the packet is attempting to go in the East direction (Steps 11-18). If the destination is on an even column (dest\_yco%2 = 0) and the current packet is on its left neighbor column but not in the same row as the destination, then the packet should not be routed to the East direction (Steps 12-14). This is because after it arrives at the destination column, it has to route in the North or South direction to reach the destination row, which however breaks the basic OE turn rules and will not be allowed. Alternatively, if the destination is to the West of the current node, then the East direction is also forbidden (Steps 15-17). This is because once the packet is routed in the East direction, it cannot go back in the West direction without violating the basic OE turn rules (if it arrives at an even column and wants to go West, it must go North or South which breaks the basic OE turn rules; if it arrives at an odd column then after turning North or South it must go West which also breaks the basic OE turn rules).

Next we check for the scenario where the destination is on the even column and the current packet is on its left neighbor column and attempting to go in a direction other than the East direction (Steps 19-27). In this case, when the current node is not on the same row as the destination, then the only choice is to go North or South towards that destination row. If the current node is on the same row as the destination, then it can only choose the East direction. The next check is for the scenario where the current node is on an odd column and the destination is to its West direction (Steps 28-29). In this case, the North and South directions are both forbidden. This is because if a packet goes in the North or South directions, it will ultimately need to go West, which is not possible without violating the basic OE turn rules. Next, we check

for the scenario where the current node is on the same column as the destination, but the current node is also on the West border of the mesh or on an odd column (Steps 30-36). In this case if the packet moves North or South in a direction away from the destination, it will not be able to turn West on the West border or make a subsequent West turn when in an odd column to reach the destination without violating basic OE turn rules. Finally, we check for a back turn, which is not allowed (Steps 37-39). If all these checks pass, then the given direction is valid for sending the packet (Step 40).

#### **Pseudocode:** Turn Restrictions for OE Implementation

```

1: RESULT check neighbor (UI ip dir, UI direct, ULL dest id) {

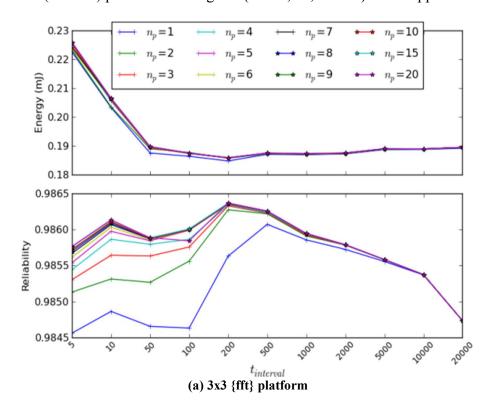

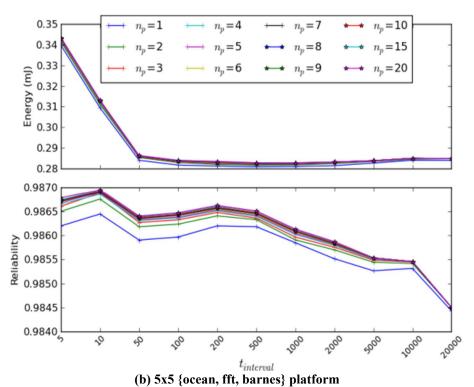

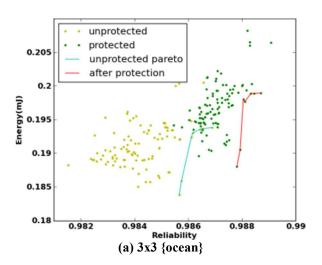

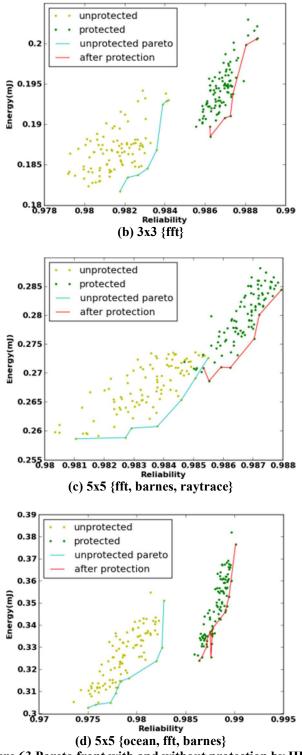

//ip dir: direction where the packet comes from