#### **DISSERTATION**

# IMPACT OF THERMAL MANAGEMENT ON VERTICAL-CAVITY SURFACE-EMITTING LASER (VCSEL) POWER AND SPEED

## Submitted by

#### Rashid Safaisini

Department of Electrical and Computer Engineering

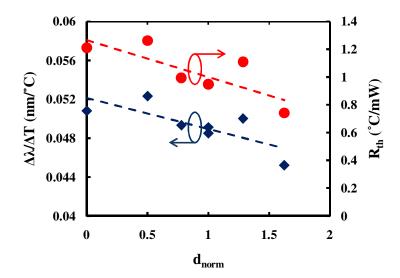

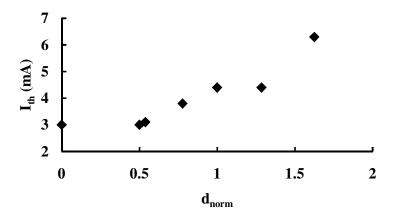

In partial fulfillment of the requirements

for the Degree of Doctor of Philosophy

Colorado State University

Fort Collins, Colorado

Spring 2011

#### **Doctoral Committee:**

Advisor: Kevin L. Lear

Mario C. Marconi Steven C. Reising James R. Sites Copyright by Rashid Safaisini 2011 All Rights Reserved

#### **ABSTRACT**

# IMPACT OF THERMAL MANAGEMENT ON VERTICAL-CAVITY SURFACE-EMITTING LASER (VCSEL) POWER AND SPEED

Increasing the modulation bandwidth and output power of vertical-cavity surfaceemitting lasers (VCSELs) are of great importance in a variety of applications such as data communication systems. The high temperature generated in the active region of VCSELs is one of the main limiting factors in achieving high power and high speed operation.

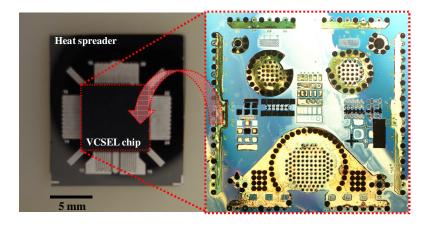

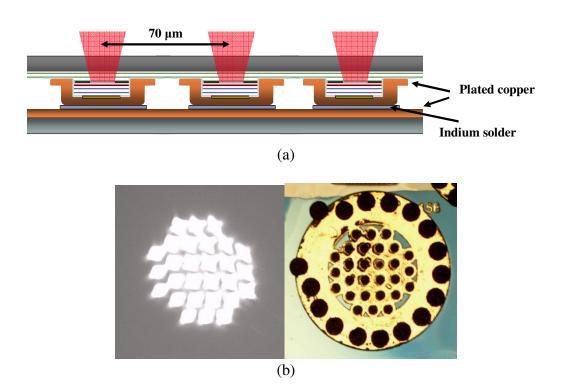

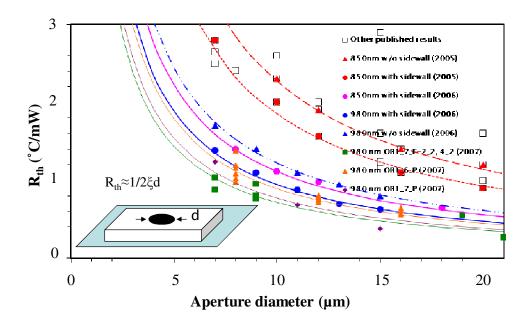

This work is focused on investigating the effects of thermal management on improving AC and DC properties of VCSELs and achieving higher thermal performance devices. Thermal heatsinking is obtained by surrounding the VCSEL mesas with high thermal conductivity materials such as copper and also using passive heatsinking by flip-chip bonding the laser dies on a GaAs heat spreader. The research includes fabricating and characterizing 980 nm bottom-emitting and 670 nm top-emitting oxide-confined VCSELs. This dissertation is divided into three main parts: high-power, high-speed 980 nm VCSEL arrays, low thermal resistance 670 nm VCSELs, and temperature dependent dynamics of 980 nm VCSELs.

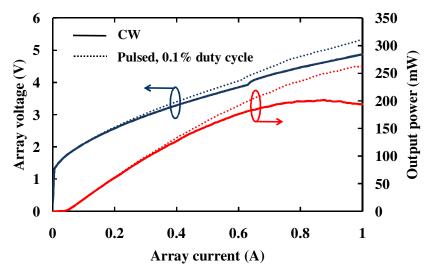

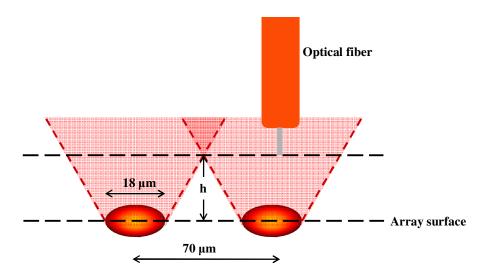

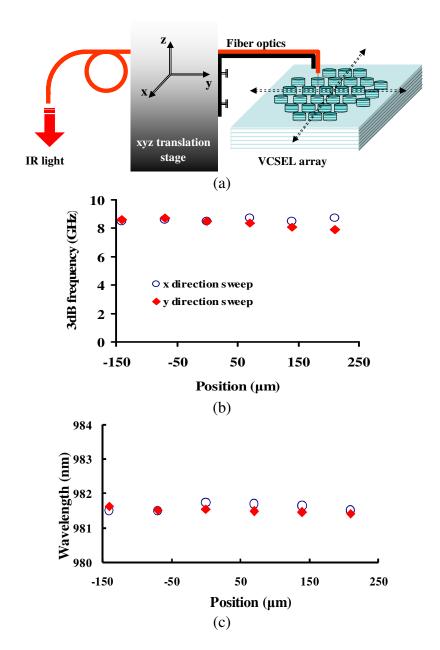

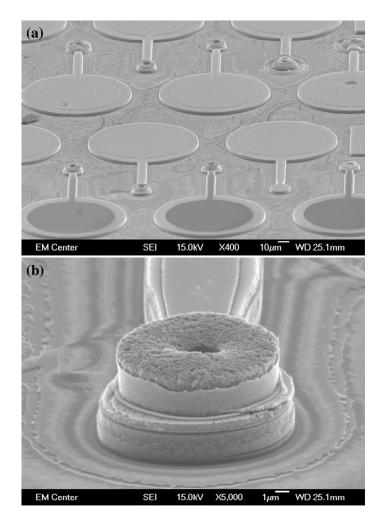

Experimental work performed on fabricating and characterizing 980 nm, bottomemitting, oxide-confined VCSEL arrays and single elements is presented first. The result of DC and AC characterization confirms the effectiveness of Cu electroplating of mesas and flip-chip bonding in reducing VCSELs' thermal resistance to obtain lower operating temperatures. Uniformity of frequency response and operating wavelength across the arrays also motivates managing thermal issues and is an indication of uniform distribution of current and heat flux on the array. This research resulted in record VCSEL arrays with frequency response of approximately 8 GHz and operating CW power of 200 mW. These 28-element, 18µm aperture diameter arrays represent the highest power reported for a VCSEL or VCSEL array with greater than 1 GHz modulation bandwidth.

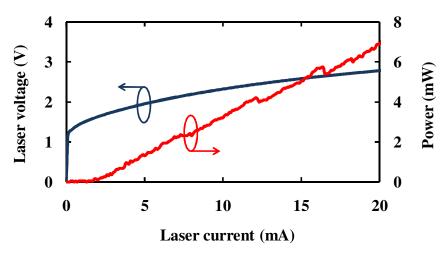

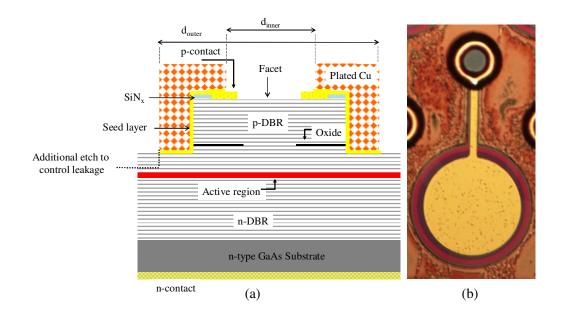

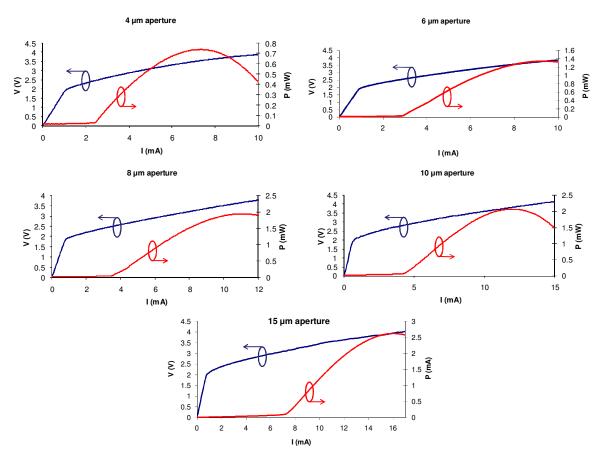

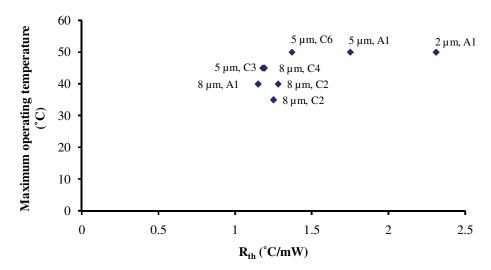

The second part of this dissertation details the fabrication steps and DC characterization of visible, 670 nm, top-emitting, oxide-confined VCSELs. Since achieving high operating temperatures is one of the main challenges in realizing improved red VCSELs, the effect of mesa heatsinking on improving their DC behavior using copper electroplating of mesas is studied. Thermal modeling of the copper plated VCSELs also facilitates better understanding and analysis of the experimental results. A photomask and process flow were designed to fabricate VCSELs with a variety of mesa diameters and inner and outer plating sizes to investigate the major direction of heat flow in the VCSELs and decrease VCSEL thermal resistance and thus increase the output power. Although copper plating significantly reduces thermal resistance, it did not substantially increase maximum operating temperature of the red devices and also put the mesas under stress that might not be desired. This study led us to analyzing the effects of stress on the VCSEL mesas which is induced by the copper films.

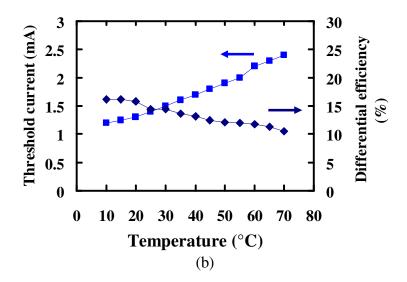

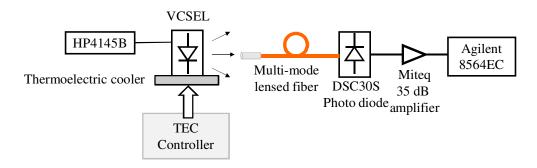

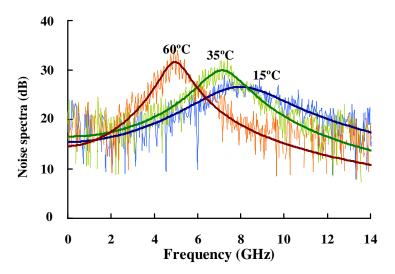

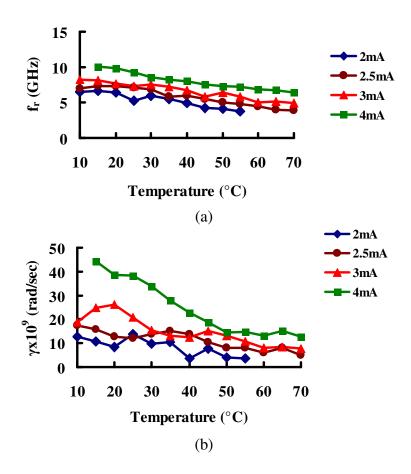

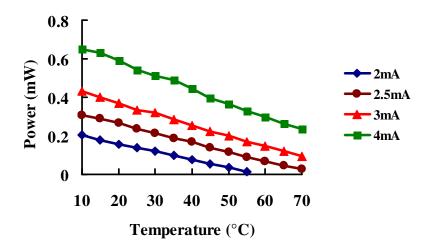

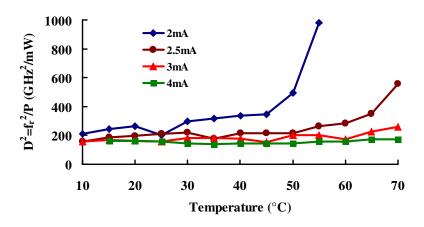

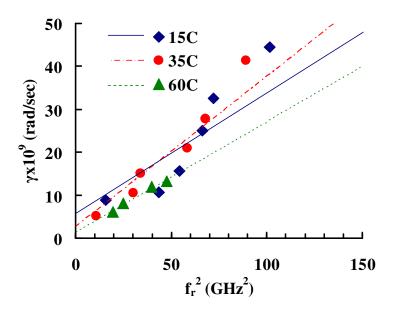

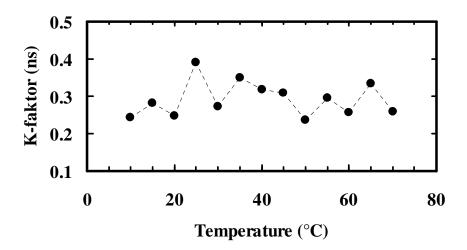

Finally, the temperature dependence of 980 nm VCSEL dynamics is investigated using noise spectra measurement. This analysis provides some useful insights in understanding how temperature alters VCSEL properties and how these properties can be

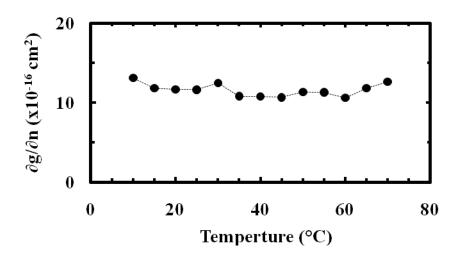

improved. A VCSEL with 7 µm aperture diameter was fabricated from the same epitaxial material and followed the same processing steps as the VCSEL arrays. Relaxation oscillation frequencies and damping factors as functions of bias current and stage temperature were extracted. These results along with the VCSEL DC measurement were used to estimate the laser differential gain as a function of temperature. The differential gain was shown to be relatively temperature independent over a temperature range of 10 °C to 70 °C with an average value of approximately 12×10<sup>-16</sup> cm<sup>2</sup>. This research led us to the conclusion that improving the output power at elevated temperatures should yield better frequency response in this case. The VCSEL output power reduction was observed to be the major cause of bandwidth reduction at elevated temperatures for the device under test. This work is the first report on the measurement of temperature dependence of VCSEL dynamics.

#### **ACKNOWLEDGMENTS**

It is a great pleasure to thank those who made this dissertation possible. I apologize in advance for not mentioning all names as it is hard to fit such a long list in a few pages.

First, I would like to thank my advisor and my first mentor at CSU, Prof. Kevin Lear. His vast knowledge in VCSELs and all areas related to optoelectronics, semiconductor devices, and lasers provided me with an endless insight into what I was doing during these years. Whenever we had a meeting or after talking about the project I was amazed by the way he thinks and approaches a problem.

I would also like to thank my committee members, Prof. Mario Marconi, Prof. Steven Reising, and Prof. James Sites who taught me how I can better think to solve a problem.

It is almost impossible to successfully finish a dissertation unless you work in a friendly group with smart colleagues. I would like to acknowledge both past and present members of our Optoelectronics Group who never hesitated to help me whenever I needed, from the first day I came to CSU. Among all group members I like to name my officemates Weina Wang and Rongjin Yan who shared the office with me for over four years and made it a pleasant place to work in. Let me also thank Joel Kindt for helping me with Comsol modeling and allowing use of his office computer whenever we needed some simulation results. David Anderson, Wesley Fuller, and Torie Hadel assisted me with proof reading my dissertation, device measurement, modeling, and cleanroom

maintenance and were always there whenever I needed a second hand. Thank you guys for your hard work!

It is really hard to work in a cleanroom without having a good mentor. John Joseph kindly taught me many different aspects of working in a cleanroom from processing to equipment maintenance. I tried really hard to learn some of his over 25 years of experience in semiconductor processing. How successful I was, I don't know! He also fabricated some of the early generations of our VCSELs.

My friends made my life in Fort Collins much easier, funnier, and more delightful. I was really lucky to have such good friends who were with me whenever I needed them—Mehdi Ahmadi, Masih Akhbari, Barmak Azizimoghaddam, Masoud Negahbanazar, and Ramin Zahedi. Thank you guys one more time.

I doubt it if I could go this far without encouragement, love, and support of my family, in particular, my father and my mother. They always believe in me and stay with me in every moment of my life. I would also like to thank my sister Shaya, my brother Vahid, and my younger sister Fatemeh for all the help, patience, and happiness they brought me. Thank you very much for everything.

Last but not least, I would like to thank my fiancé, Golnaz, for waiting for me and understanding me during these years when I was far away from home. Thank you for being with me in every moment of this journey, when I was happy of getting good results and when I was sad for not getting good results or angry of malfunctioning of a piece of equipment in the lab! Thank you so much for making my life more colorful.

# TABLE OF CONTENTS

| СНАРТ | TER 1 INTRODUCTION                                                        | 1    |

|-------|---------------------------------------------------------------------------|------|

| 1.1.  | Introduction                                                              | 1    |

| 1.2.  | VCSELs at different wavelengths                                           | 3    |

| 1.3.  | Research objectives and outline                                           | 4    |

| Refer | rences                                                                    | 6    |

| СНАРТ | TER 2 VCSEL STRUCTURE AND OPERATING PRINCIPLES                            | 8    |

| 2.1.  | Introduction                                                              | 8    |

| 2.2.  | Vertical-cavity surface-emitting lasers (VCSELs) vs. edge emitting lasers | sers |

| (EEL  | _s)                                                                       | 11   |

| 2.3.  | Introduction to distributed Bragg reflectors (DBRs)                       | 13   |

| 2.4.  | VCSEL active region                                                       | 17   |

| 2.5.  | Current and optical confinement in VCSELs                                 | 22   |

| 2.6.  | VCSELs: dc and ac response                                                | 23   |

| 2.6   | 6.1. VCSELs under dc condition                                            | 24   |

| 2.6   | 6.2. VCSELs modulation response                                           | 27   |

| 2.6   | 6.3. Relative intensity noise (RIN)                                       | 32   |

| 2.7.  | Thermal properties of VCSELs                                              | 34   |

| 2.7   | 7.1. Temperature effects on VCSEL operation                               | 34   |

| 2.7.2. Material thermal conductivity and VCSEL thermal resistance | 37    |

|-------------------------------------------------------------------|-------|

| References                                                        | 40    |

| CHAPTER 3 VCSELS: THEIR BIRTH TO RECENT DEVELOPMENTS              | 43    |

| 3.1. Historical overview of surface emitting lasers (SELs)        | 43    |

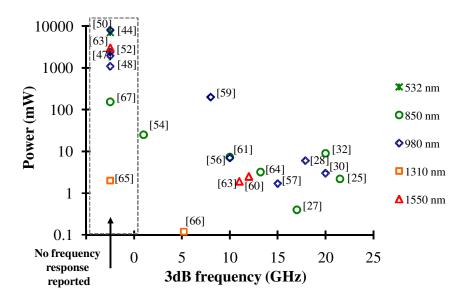

| 3.2. High modulation bandwidth VCSELs                             | 46    |

| 3.3. High power single VCSELs and arrays                          | 51    |

| References                                                        | 54    |

| CHAPTER 4 980 NM HIGH-SPEED, HIGH-POWER OXIDE-CONFINED V          | 'CSEL |

| ARRAYS AND SINGLE ELEMENTS                                        | 65    |

| 4.1. Introduction                                                 | 65    |

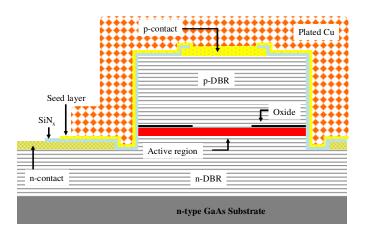

| 4.2. VCSEL design and fabrication                                 | 66    |

| 4.2.1. Structure                                                  | 66    |

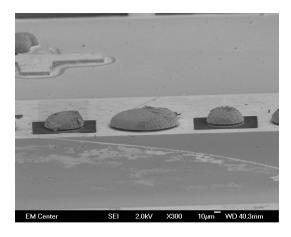

| 4.2.2. Fabrication                                                | 67    |

| 4.3. Array characterization                                       | 72    |

| 4.3.1. DC characterization                                        | 72    |

| 4.3.2. AC characterization                                        | 75    |

| 4.3.3. Pulsed characterization                                    | 79    |

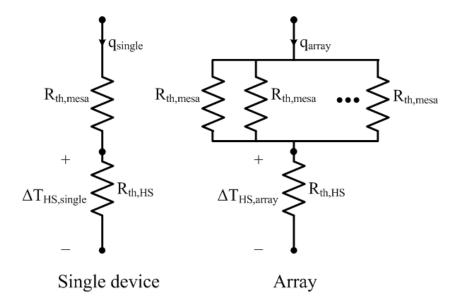

| 4.3.4. Thermal resistance analysis                                | 81    |

| 4.3.5. Uniformity analysis                                        | 83    |

| 4.4. Conclusions                                                  | 86    |

| References                                                        | 87    |

| CHAPTER 5 THERMAL MANAGEMENT OF RED VCSELS                        | 89    |

| 5.1 Total backing                                                 | 0.5   |

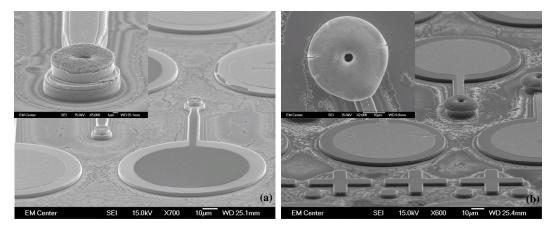

| 5.2. VC   | SEL design and fabrication                     | 90  |

|-----------|------------------------------------------------|-----|

| 5.2.1.    | Structure                                      | 90  |

| 5.2.2.    | Fabrication                                    | 90  |

| 5.3. VC   | SELs characterization before Cu electroplating | 95  |

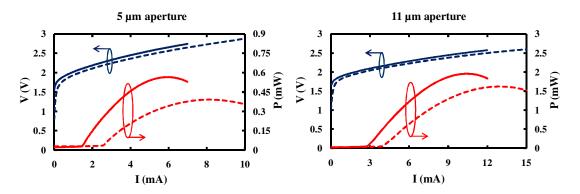

| 5.3.1.    | LIV Characterization                           | 95  |

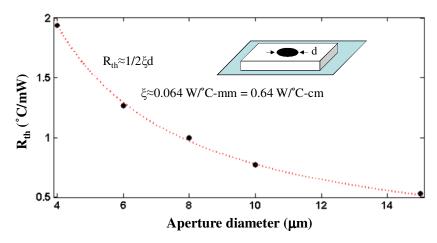

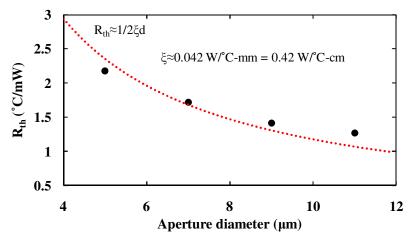

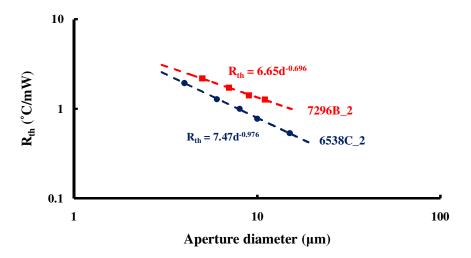

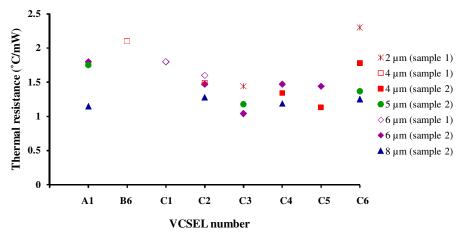

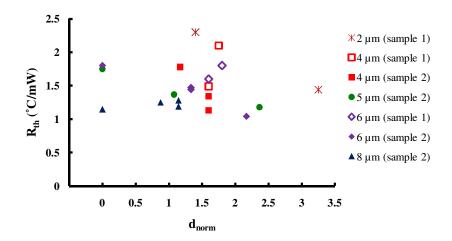

| 5.3.2.    | Thermal resistance measurement                 | 98  |

| 5.4. VC   | SELs characterization after Cu electroplating  | 102 |

| 5.4.1.    | LIV characterization                           | 105 |

| 5.4.2.    | Thermal resistance measurement                 | 109 |

| 5.5. Effe | ects of stress in Cu plated VCSELs             | 112 |

| 5.6. VC   | SEL thermal modeling                           | 121 |

| 5.6.1.    | Device structure                               | 122 |

| 5.6.2.    | Material parameters                            | 124 |

| 5.6.3.    | Simulation results                             | 125 |

| 5.7. Cor  | nclusions                                      | 133 |

| Reference | s                                              | 134 |

| CHAPTER 6 | 5 VCSEL DYNAMICS AND SINGLE MODE OPERATION     | 138 |

| 6.1. Intr | oduction                                       | 138 |

| 6.2. Ter  | mperature dependence of VCSEL dynamics         | 139 |

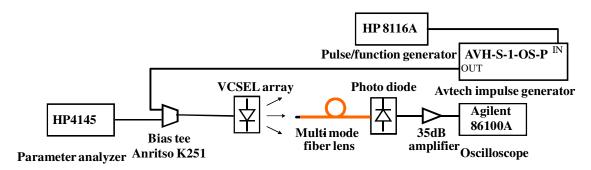

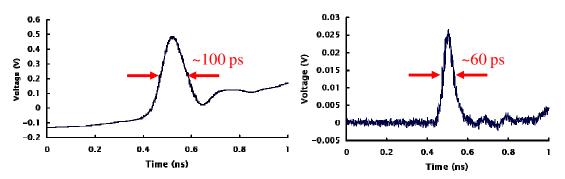

| 6.2.1.    | Experiment                                     | 139 |

| 6.2.2.    | Analysis                                       | 143 |

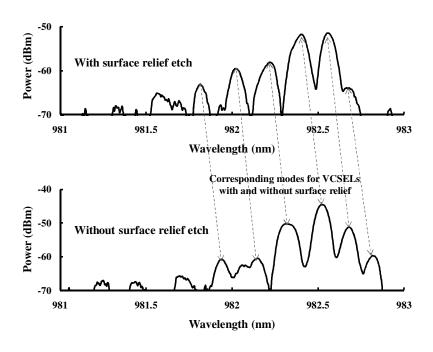

| 6.3. Sin  | gle mode operation of VCSELs                   | 148 |

| 631       | Surface relief principles                      | 149 |

| 6.3.2. Experiment                                                         |

|---------------------------------------------------------------------------|

| 6.4. Conclusions 159                                                      |

| References                                                                |

| CHAPTER 7 CONCLUSIONS AND FUTURE WORK163                                  |

| 7.1. Summary of achievements                                              |

| 7.1.1. 980 nm oxide-confined bottom-emitting VCSELs                       |

| 7.1.2. 670 nm oxide-confined top-emitting VCSELs                          |

| 7.2. Future Work                                                          |

| 7.2.1. Reducing the Cu stess on the mesa for better device performance169 |

| 7.2.2. Effect of single mode operation on VCSELs frequency response and   |

| dynamics                                                                  |

| 7.2.3. VCSEL simulation                                                   |

| APPENDIX A EPITAXIAL DESIGN FOR 980-NM BOTTOM-EMITTING VCSELS             |

| 172                                                                       |

| APPENDIX B PROCESS FLOW FOR BOTTOM- AND TOP-EMITTING VCSELS 175           |

| APPENDIX C SAVE/RECALL STATE FILES FOR CASCADE MICROTECH HIGH             |

| SPEED GSG PROBE185                                                        |

| APPENDIX D COMBINATIONS OF FEATURE SIZES ON RED VCSEL MASK                |

| "VCSEL_TE_RS"186                                                          |

# Chapter 1

## INTRODUCTION

#### 1.1. Introduction

Semiconductor lasers are the most important light source for optical communication because of their high efficiency, small size, simple structure, and more importantly, compatibility with electronic chips. According to the direction of the laser beam coming out of the laser and its propagation direction with respect to the grown epitaxial layers, there are two main categories of semiconductor lasers. These two are the vertical-cavity surface-emitting laser (VCSEL) that is the main focus of this dissertation and the edge-emitting laser (EEL). The structure of both types of lasers will be discussed in the next chapter.

After their invention in the 1980s, VCSELs became very popular in both research and from a technological point of view. Since 1996 when the first commercial VCSEL was presented by Honeywell, they have become dominant light sources and replaced EELs for a wide range of applications such as short-range fiber optics communication.

VCSELs can offer a number of fascinating properties such as [1], [2]:

- Very low threshold current, I<sub>th</sub>, due to small cavity volume (<0.1 mA [3])

- Single longitudinal mode operation

- High speed direct modulation (>20 GHz [4]) due to a very large relaxation oscillation frequency

- Low power consumption and high power-conversion efficiency (>50% [5])

- Relatively insensitive wavelength and thresholds to temperature changes

- Narrow circular beam and easy coupling to optical fiber

- Good reliability

- Realization of monolithic large-scale two-dimentional (2D) VCSEL arrays

- Easy bonding and on chip testing before sample cleaving; lowering manufacturing cost

- Integration with micro electromechanical systems for wavelength tuning

Such unique features of VCSELs make them popular and a potential light source for a variety of applications. These applications include short-range optical communication like Gigabit Ethernet, fiber channels, computer links, optical interconnects, high speed local area networks (LANs), position sensing, automotive applications and consumer electronics such as projection displays and laser mice [1], [6].

Table 1.1 VCSEL market by application in US\$ million (reproduced from [7])

|                    | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 |

|--------------------|------|------|------|------|------|------|

| Automotive         | 18   | 23   | 27   | 30   | 33   | 38   |

| Computer           | 65   | 79   | 94   | 109  | 114  | 133  |

| Consumer           | 63   | 77   | 93   | 103  | 112  | 131  |

| Industrial         | 30   | 37   | 44   | 49   | 53   | 62   |

| Military/Aerospace | 20   | 24   | 29   | 32   | 35   | 41   |

| Telecoms           | 25   | 31   | 37   | 41   | 45   | 52   |

| Other              | 9    | 11   | 13   | 15   | 16   | 19   |

| Total              | 231  | 282  | 337  | 375  | 407  | 477  |

In Table 1.1 contribution of each VCSEL application in the global market in 2003-2008 is presented in US\$ million [7]. It can be seen from the table that computer related applications such as optical networks and consumer electronics such as optical mice, scanners, and sensors are two of the largest applications of VCSELs in the global market.

### 1.2. VCSELs at different wavelengths

The first attempts in realizing VCSELs were based on devices operating at 850 nm and 1310 nm based on GaAlAs/GaAs and GaInAsP/InP active regions, respectively [1]. VCSELs operating at 850 nm were the first commercialized multitransverse-mode VCSELs. However, the invention of oxide isolation in VCSELs opened new doors towards the single transverse-mode VCSELs which facilitate using them in sensing, printing, and optical memory applications [8]. 850 nm VCSELs were the first available VCSEL in the market and very soon became the standard wavelength for the optical communication. The highest modulation speed for commercialized 850 nm VCSELs was revealed by Panasonic in 2005 and was capable of data rates of up to 12.5 Gb/s [7].

In near infrared, in addition to 850 nm VCSELs, 780 nm and 980 nm are of great importance. 780 nm VCSELs which, like 850 nm, are already commercialized are suitable for applications in laser printing industry which has developed toner dye that is preferentially absorptive to 780 nm [8]. Commercialized VCSELs ranging from 750-870 nm are fabricated based on AlGaAs/GaAs quantum wells. Using InGaAs/GaAs QWs, one can achieve longer near infrared wavelengths such as 980 nm. This wavelength has an advantage of being transparent to the GaAs substrate that makes the VCSEL packaging easier.

Long-wavelength VCSELs (LW-VCSELs) at 1310 nm and 1550 nm have also become important for applications in high-bandwidth optical networks [9] and in communication systems based on optical fiber such as long-haul transmission lines [10]. One very interesting feature of LW-VCSELs is that they are eye safe at wavelengths >1400 nm and so they can be used in free space optical communication in which eye safety should be highly considered.

VCSELs in visible wavelengths (660-680 nm) are also finding their applications in plastic optical fiber (POF) communication, medical, and data reading/capture [11]. Applications in consumer electronics such as laser mice and barcode scanners can also be served by visible VCSELs. Red VCSELs are grown on GaAs substrate using InGaP/InGaAlP active material. Because of their relatively small band offset and consequently poor carrier confinement, it is difficult to achieve high temperature lasing using this material [8]. As a result, techniques to bring the active region temperature down are helpful for realizing better performance red VCSELs.

### 1.3. Research objectives and outline

In this research, 980 nm and 670 nm VCSELs have been fabricated and their different aspects characterized. Thermal resistance reduction and high speed modulation frequency with high power operation of VCSELs were investigated.

Chapter 2 discusses the background and operating principles of VCSELs including basic concept of DBRs as high reflectivity mirrors and QWs as active regions. This chapter also reviews governing equations for semiconductor laser frequency response.

In Chapter 3 the previously published work on VCSELs from their birth has been reviewed and important steps in development of VCSEL fabrication and characterization have been addressed.

Chapter 4 presents the fabrication steps of bottom-emitting flip-chip bonded VCSELs and then describes the details of fabrication and characterization of 980 nm high-speed, high-power VCSEL arrays. These arrays have the highest ever reported optical power for greater than 1 GHz modulation speed at the time of research.

Chapter 5 details the fabrication steps of top-emitting VCSELs and also discusses the attempts for thermal resistance reduction and output power enhancement of 670 nm visible VCSELs with better thermal management of active region by copper electroplating of the mesas. In addition, stress on VCSEL mesas induced by plated copper is explained. Thermal and stress modeling of copper plated red VCSELs using COMSOL multiphysics is also given in this chapter.

In Chapter 6 temperature dependence of dynamics of 980 nm VCSELs are investigated using noise spectra measurement. In this chapter after estimating the relaxation oscillation frequency and damping factor, the differential gain of the device under test as well as some other laser parameters are extracted. This work is also the first report on temperature dependence of 980 nm oxide confined VCSEL dynamics.

Finally, Chapter 7 concludes the work done in previous chapters and gives suggestions for the possible future work.

#### References

- [1] H. Li and K. Iga, Eds., *Vertical-Cavity Surface-Emitting Laser Devices*, Springer-Verlag, Berlin, 2003.

- [2] Fumio Koyama, "Recent Advances of VCSEL Photonics," *Journal of Lightwave Technology*, vol. 24, no. 12, December 2006.

- [3] See, for example, D. L. Huffaker, J. Shin, and D. G. Deppe, "Low threshold half-wave vertical cavity lasers," *Electronics Letters*, vol. 30, no. 23, pp. 1946–1947, Nov. 1994.

- [4] See, for example, K. L. Lear et al., "Small and large signal modulation of 850 nm oxide-confined vertical cavity surface emitting lasers," *Advances in Vertical Cavity Surface Emitting Lasers in series OSA Trends in Optics and Photonics*, vol. 15, pp. 69–74, 1997.

- [5] See, for example, K. L. Lear, K. D. Choquette, R. P. Schneider, Jr., S. P. Kilcoyne, and K. M. Geib, "Selectively oxidized vertical cavity surface emitting lasers with 50% power conversion efficiency," *Electronics Letters*, vol. 31, no. 3, pp. 208–209, Nov. 1994.

- [6] K. L. Lear and A. N. Al-Omari, "Progress and issues for high speed vertical cavity surface emitting lasers," *Proc. SPIE*, ser. Vertical Cavity Surface Emitting Lasers XI, vol. 6484, pp. 64840J-1–64840J-12, 2007.

- [7] Roy Szweda, "VCSEL applications diversify as technology matures," *III-Vs review*, vol. 19, no. 1, pp. 34-38, Feb. 2006.

- [8] Jim Tatum, "Vertical-cavity lasers: Packaging flexibility propels VCSELs beyond telecommunications," *Laser Focus World*, vol.36, no. 4, Apr. 2000.

- [9] Eli Kapon and Alexei Sirbu, "Long-wavelength VCSELs: Power-efficient answer," *Nature Photonics*, vol. 3, pp. 27-29, Jan. 2009.

- [10] P. L. Gourley, K. L. Lear, and R. P. Schneider Jr., "A different mirror...," *IEEE Spectrum*, vol. 31, no. 8, Aug. 1994.

- [11] Roy Szweda, "VCSELs resurgent," III-Vs review, vol. 17, no. 8, pp. 2-5, Nov. 2004.

# Chapter 2

## VCSEL STRUCTURE AND OPERATING PRINCIPLES

#### 2.1. Introduction

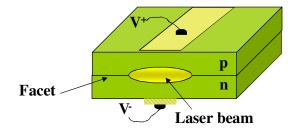

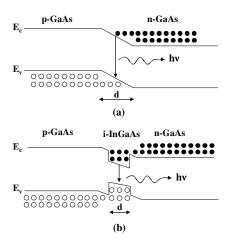

Semiconductor lasers are the most important light source for optical communication because of their high efficiency, small size, simple structure, and more importantly, compatibility with electronic chips. In a very simple point of view, a semiconductor laser is a forward biased p-n junction in a resonant cavity which can be formed by cleaving the facets of the structure as shown in Figure 2.1. In this case, the junction of p and n regions is the active region in which electrons in conduction band recombines with holes in valence band and spontaneous emission occurs. Because of their p-n junction based structure, semiconductor lasers are also known as diode lasers.

Figure 2.1 A basic p-n junction laser.

The spontaneously emitted single photon with energy equal to semiconductor bandgap energy,  $E_g$ , can generate another identical photon by stimulating the

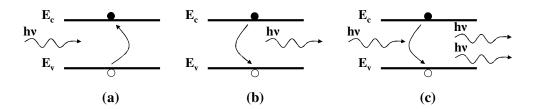

recombination of an electron-hole pair. This photon multiplication is the key mechanism of lasing. The second photon exhibits the same wavelength and phase as the incident photon; therefore, this process doubles the amplitude of the resultant optical wave. Subsequent repetition of this process can generate very strong light fields. However, the reverse process which is absorption of photons by generation of new electron-hole pairs should also be taken into account. Absorption, spontaneous emission, and stimulated emission processes are schematically shown in Figure 2.2.

Figure 2.2 Photon-carrier interaction processes in semiconductors, (a) absorption, (b) spontaneous emission, and (c) stimulated emission.

The solution for the stimulated emission dominating absorption is carrier inversion, i.e. piling up more electrons in the conduction band than the valence band. Continuous carrier injection leads to continuous stimulated photon generation only if enough photons exist in the device to stimulate other photons. Now, an optical resonator is needed to create optical feedback and photon confinement [1].

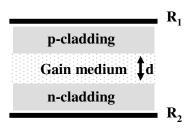

Assume a laser structure with a gain medium surrounded by n- and p-type cladding layers all in a cavity with mirror reflectivities of  $R_1$  and  $R_2$  at two ends as in Figure 2.3. The whole structure in the cavity can be simply considered as a pin diode.

Figure 2.3 General configuration of a semiconductor laser.

In order to have a laser, total gain per unit length should overcome the total losses per unit length in the cavity. If we define G as the net power gain after a single trip in the cavity and g as the gain per unit length, these two can be related to each other by  $G=exp((g-\alpha_i)d)$  where d is the length of the gain medium and laser and  $\alpha_i$  is the internal loss of the cavity. A requirement for lasing is having a large enough gain in order that round trip gain exceeds 1 or in other words gain per unit length exceeds total losses per unit length,  $\alpha$ . In this case  $R_1R_2(G)^2 \ge 1$  and

$$R_1 R_2 e^{2(g - \alpha_i)L} \ge 1 \tag{2.1}$$

$$g \ge \alpha_i + \frac{1}{2L} \ln \frac{1}{R_1 R_2} = \alpha \tag{2.2}$$

Before talking about threshold situation for lasing I would like to introduce a confinement factor,  $\Gamma$ , and substitute g with  $\Gamma g$  in order to consider only the effective interaction between gain medium and photon field. Confinement factor is simply a ratio of active region volume occupied by gain,  $V_g$ , over the cavity volume occupied by photons,  $V_p$ ,  $\Gamma = V_g/V_p$  [2]. The threshold condition is considered as

$$\Gamma g_{th} = \alpha_i + \frac{1}{2L} ln \frac{1}{R_1 R_2}$$

(2.3)

$$\alpha_m = \frac{1}{2L} \ln \frac{1}{R_1 R_2} \tag{2.4}$$

$$\alpha = \alpha_m + \alpha_i \tag{2.5}$$

Where  $\alpha_m$  is the mirror loss from both mirrors.

# 2.2. Vertical-cavity surface-emitting lasers (VCSELs) vs. edge emitting lasers (EELs)

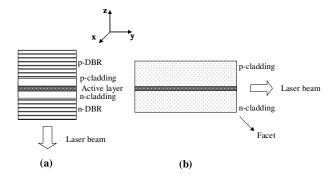

In a vertical-cavity surface-emitting laser (VCSEL), as illustrated in Figure 2.4(a), epitaxial layers are grown in x-y planes at different z positions, and light propagates along the normal to the epitaxial growth layers, i.e. in the z direction. Therefore, the length of the optical gain which effectively amplifies the optical field equals the active layer thickness which is in the order of ten nanometers to a few micrometers [3]. According to (2.3), with such a short cavity length, high mirror reflectivities are needed to achieve low threshold in VCSELs. Distributed Bragg reflectors (DBRs) formed by alternatively stacking layers of materials with different refractive indices can offer very high reflectivities above 99.9%. These types of reflectors will be studied in detail in Section 2.3.

Figure 2.4 (a) VCSEL, (b) EEL.

In edge emitting lasers (EELs), as in Figure 2.4(b) laser beam propagates parallel to epitaxial layers along the y direction. In this case, the whole length of the gain medium along the propagation direction, which can be on the order of hundreds of micrometers, contributes to amplification. As a result, even with cleaved laser facets (~30% reflectivity of GaAs/Air interface) low threshold operation is achievable.

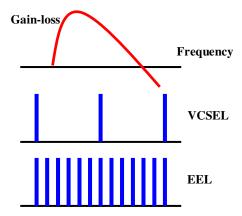

A shorter cavity length also leads to more widely spaced resonance modes in the cavity and so fewer cavity modes lie in between the low magnitude tails of the gain-loss curve of the gain material. This fact causes better single longitudinal mode operation in VCSELs compared to EELs as sketched in Figure 2.5.

Figure 2.5 Gain-loss curve along with cavity resonance modes in VCSELs and EELs.

In next two following sections, I explain the working principles of DBRs and active regions which are two building blocks of VCSELs.

# 2.3. Introduction to distributed Bragg reflectors (DBRs)

Distributed Bragg reflectors (DBRs) are widely used as top and bottom mirrors in VCSELs because of their high reflectivity. Unlike hard mirrors in a Fabry-Perot cavity,

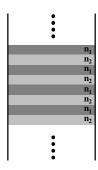

reflection points in DBRs are distributed all over the structure resulting in a mirror with varying reflection and phase change at different wavelengths [4], [5]. As in Fig 2.6, theses reflectors are formed by stacking alternating layers of semiconductor materials such as GaAs/AlGaAs or dielectric layers such as Si/SiO<sub>2</sub> with high and low refractive indices. If we choose a correct thickness for each layer, we can get beam reflection at each interface leading to a very large reflectivity with a constructive interference.

Figure 2.6 Stacking of layers with different refractive indices in a DBR.

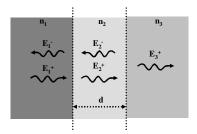

Assume a normally incident light on an interface between two layers with refractive indices  $n_1$  and  $n_2$  and infinite thicknesses as shown in Figure 2.7. Incident electric field with amplitude  $E_1^+$  hits the interface from the layer with refractive index  $n_1$ . Some portion of the beam with an electric field amplitude  $E_1^-$  reflects back to the  $n_1$  medium. The transmitted beam which has the electric field amplitude of  $E_2^+$  travels through the  $n_2$  medium and as an assumption there is no incident beam from the  $n_2$  region toward  $n_1$ , i.e.  $E_2^-=0$ . In this case with defining reflection coefficient,  $r=E_1^-/E_1^+$  and transmission coefficient,  $t=E_2^+/E_1^+$ , the electric field in two regions can be related with a matrix called a transfer matrix,  $T_r$ .

$$\begin{bmatrix} E_I^+ \\ E_I^- \end{bmatrix} = \begin{bmatrix} 1/t & (r/t)^* \\ r/t & (1/t)^* \end{bmatrix} \begin{bmatrix} E_2^+ \\ E_2^- \end{bmatrix} = T_r \begin{bmatrix} E_2^+ \\ E_2^- \end{bmatrix}$$

(2.6)

Figure 2.7 Electric fields at two sides of an interface.

From Fresnel's equation,  $r=(n_1-n_2)/(n_1+n_2)$ , and defining reflectivity,  $R=rr^*=|r|^2$ , and transmission,  $T=tt^*=|t|^2$  of the interface and also neglecting absorption, by conservation of energy, we must have R+T=1. So

$$\left(\frac{n_1 - n_2}{n_1 + n_2}\right)^2 + t^2 = 1 \Rightarrow t = \frac{2\sqrt{n_1 n_2}}{n_1 + n_2}$$

(2.7)

Now let's consider another problem with 3 different media with refractive indices  $n_1$ ,  $n_2$ , and  $n_3$ . Assume the  $n_2$  medium with length d is placed between  $n_1$  and  $n_3$  regions which extend to infinity as drawn in Figure 2.8. Phase factors  $e^{ik_2d}$  and  $e^{-ik_2d}$  should be considered in this problem for the region 2 with thickness d and wave number  $k_2=2\pi n_2/\lambda_0$ , in order to count for the wave traveling through the region with a finite thickness.

Figure 2.8 Electric fields for a two interface system.

In this case for the transfer matrix we have

$$\begin{bmatrix} E_{1}^{+} \\ E_{1}^{-} \end{bmatrix} = \begin{bmatrix} 1/t_{1,2} & \binom{r_{1,2}}{t_{1,2}} \\ \frac{1}{t_{1,2}} & \binom{r_{1,2}}{t_{1,2}} \\ \frac{1}{t_{1,2}} & \binom{r_{1,2}}{t_{1,2}} \end{bmatrix}^{*} \begin{bmatrix} e^{-ik_{2}d} & 0 \\ 0 & e^{ik_{2}d} \end{bmatrix} \begin{bmatrix} 1/t_{2,3} & \binom{r_{2,3}}{t_{2,3}} \\ \frac{r_{2,3}}{t_{2,3}} & \binom{1/t_{2,3}}{t_{2,3}} \end{bmatrix}^{*} \begin{bmatrix} E_{3}^{+} \\ E_{3}^{-} \end{bmatrix}$$

$$= T_{r} \begin{bmatrix} E_{3}^{+} \\ E_{3}^{-} \end{bmatrix}$$

$$= T_{r} \begin{bmatrix} e^{-ik_{2}d} & 0 \\ 0 & e^{ik_{2}d} \end{bmatrix} \begin{bmatrix} n_{2} + n_{3} & n_{2} - n_{3} \\ 2\sqrt{n_{2}n_{3}} & 2\sqrt{n_{2}n_{3}} \\ n_{2} - n_{3} & 2\sqrt{n_{2}n_{3}} \end{bmatrix}$$

$$= \frac{1}{2\sqrt{n_{1}n_{2}}} \begin{bmatrix} n_{1} + n_{2} & n_{1} - n_{2} \\ n_{1} - n_{2} & n_{1} + n_{2} \end{bmatrix} \begin{bmatrix} e^{-ik_{2}d} & 0 \\ 0 & e^{ik_{2}d} \end{bmatrix} \begin{bmatrix} n_{2} + n_{3} & n_{2} - n_{3} \\ n_{2} - n_{3} & 2\sqrt{n_{2}n_{3}} \end{bmatrix}$$

$$= \frac{1}{2\sqrt{n_{1}n_{2}}} \begin{bmatrix} n_{1} + n_{2} & n_{1} - n_{2} \\ n_{1} - n_{2} & n_{1} + n_{2} \end{bmatrix} \begin{bmatrix} e^{-ik_{2}d} & 0 \\ 0 & e^{ik_{2}d} \end{bmatrix} \begin{bmatrix} 1/t_{2} & n_{2} + n_{3} & n_{2} - n_{3} \\ n_{2} - n_{3} & n_{2} + n_{3} \end{bmatrix}$$

$$= (2.9)$$

It is easy to understand from (2.9) that if  $k_2d=m\pi$  (m integer) or  $d=m\lambda/2$ , the region 2 acts as a latent layer and passes the beam without any net phase change and we get the minimum reflection from the structure, while if  $k_2d=m\pi/2$  (m odd) or  $d=m\lambda/4$ , we have the maximum reflection and all the beam reflects back to the region 1. Similar argument for the thickness of layers is valid in DBRs. In DBRs, maximum reflectivity is achievable for a larger number of  $\lambda/4$  thick layers.

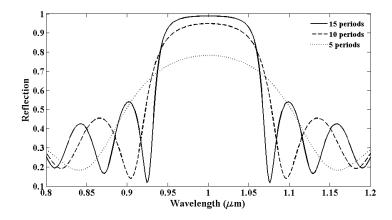

In Figure 2.9, the reflection spectrum of a DBR with  $\lambda_0/4n_{1,2}$  thick layers of GaAs/Al<sub>0.86</sub>Ga<sub>0.14</sub>As (71.4 nm/83.3 nm) with corresponding refractive indices of 3.5/3 is calculated for different mirror periods. This DBR has been designed in a way to have the maximum reflection at  $\lambda_0$ =1 µm wavelength. For the highest reflectivity, this DBR is terminated by the higher index layer (GaAs) at both ends. It is obvious from the resultant

plot that the reflection increases with increasing the number of layers as expected. The DBR also behaves as a band pass filter which just reflects several 100s of nms above and below the center wavelength.

Figure 2.9 Reflection spectrum of a DBR with varying mirror periods.

A simplified expression might also be used to calculate the reflectivity at the Bragg frequency with no loss or gain [2]. With the number of mirror pairs, m, and reflectivity of each interface, r, the reflectivity of DBR at the Bragg frequency can be written as

$$r_{DBR} = \tanh \left[ m \ln \left( \frac{1+r}{1-r} \right) \right] \tag{2.10}$$

In addition to optical properties of DBRs which were already discussed in this section, their electrical properties are also crucial in VCSEL operation; because, since electrical current needs to at least flow through a portion of top and bottom DBRs in VCSELs to reach electrical contacts. Although semiconductor DBRs are not perfect electrical conductors, they can be modified to improve their electrical behavior with a compromise between optical and electrical properties. When current flows through a

DBR, it meets potential barriers due to unequal bandgap energy of layers that can increase scattering and electrical resistance [4]. Compositional grading of DBR layers can smooth out the bandgap structure and reduces the carrier scattering [6]. Mirror doping can also be modulated in order to decrease series electrical resistance in DBRs [6].

# 2.4. VCSEL active region

The active region, where recombining carriers contribute to useful gain and photon emission, is another key element in semiconductor lasers. It is obvious that the active region in laser should be able to act as a gain region in which stimulated emission overcomes absorption for lasing.

The first semiconductor lasers were made up of homostructure devices in which only one type of semiconductor was used to fabricate lasers. These lasers showed high threshold currents even at low temperatures where the gain is higher and carrier density necessary for reaching transparency is lower than at room temperature. Besides, they couldn't operate in continuous wave (CW) [7].

The method that is now generally used to improve laser performance is utilizing heterostructure devices instead of homostructures. Let's see why heterostructures can help. We can solve (2.3) for threshold gain,  $g_{th}$ ,

$$g_{th} = \frac{I}{\Gamma} \left( \alpha_i + \frac{1}{2L} \ln \frac{I}{R_I R_2} \right) \tag{2.11}$$

For a bulk gain medium, and under very restrictive conditions, gain as a function of carrier density, N, can be approximated by [2], [7]

$$g \approx a(N - N_{tr}) \tag{2.12}$$

where a is the differential gain,  $\partial g/\partial N$ , and  $N_{tr}$  is a transparency carrier density where the gain is zero. Keep in mind that (2.12) is a limited range approximation for gain and a logarithmic function fits the gain better over a wider range of carrier densities.

Carrier density can also be written as a function of injected current density, J, [2]

$$N = \frac{\tau \eta_i}{qd} J \tag{2.13}$$

where  $\tau$  is the carrier lifetime, q is the electron charge, d is the active region thickness, and  $\eta_i$  is the internal quantum efficiency which is the ratio of carriers generated in the active region over the injected current into the laser. Now we can combine (2.11)-(2.13) to find a simple equation for threshold current density,  $J_{th}$ .

$$J_{th} = \frac{qd}{\tau \eta_i} \left[ N_{tr} + \frac{1}{a\Gamma} \left( \alpha_i + \frac{1}{2L} ln \frac{1}{R_1 R_2} \right) \right]$$

(2.14)

Now let's go back to our argument about using heterostructure to improve laser performance. As seen from (2.14), threshold current density is one of the parameters proportional to the active region thickness. If we can somehow decrease the active region thickness, the threshold current density would decrease as well. In the case of homostructure lasers, active region thickness is the distance traveled by a conduction electron from n-type to p-type region before recombining with a hole and can be ~1 μm for a typical GaAs homostructure (Figure 2.10(a)). Therefore, in this case there is no control on decreasing the active layer thickness. A better way to reduce the active layer thickness is using a layer with smaller bandgap energy than n- and p-type cladding layers as an active region. Carriers are confined and then recombine in the smaller bandgap region while surrounding higher bandgap materials act as barriers to block carrier flow. The resultant structure is called a heterostructure. As in Figure 2.10(b), for example, a

heterostructure can be realized by inserting a layer of InGaAs to a GaAs homostructure introduced in Figure 2.10(a). In this case, the active region thickness is basically the thickness of the low bandgap layer which can be well controlled during the growth and can be kept even smaller than 100 nm. Nowadays, these well-controlled thin layers of semiconductors can easily be grown by molecular beam epitaxy (MBE) or metal-organic chemical vapor deposition (MOCVD) systems with very precise in situ thickness monitoring. Significantly increased excess carriers in the structure in Figure 2.10(b) will also shorten the radiative recombination lifetime and lead to a more efficient radiative recombination [8].

Heterostructures might be categorized as single heterostructures and double heterostructures depending on using one or two blocking layers. Double heterostructures provide an optical waveguide for the laser field, resulting in a higher optical confinement factor. Wider bandgap materials as cladding (blocking) layers also reduce the optical losses because blocking layers are transparent to the laser field generated in the smaller bandgap active region. The active region is usually undoped to achieve high radiation efficiency, while doping the active region causes recombination of injected carriers in the active region which decreases the carrier lifetime and increases the laser modulation frequency.

Figure 2.10 Band structure of (a) a homostructure, and (b) a heterostructure (Reproduced from [8]).

If we shrink the thickness of the lower bandgap region down to less than 100 nm, we form a quantum well (QW) structure which is frequently used in semiconductor lasers such as VCSELs. QW structures offer advantages such as more gain per injected carriers than conventional active regions. They also deliver gain with less change in refractive index than bulk lasers, resulting in lower chirp [9]. As described earlier, confinement factor is proportional to the active region volume occupied by gain,  $V_g$  ( $\Gamma = V_g/V_p$ ). That means decreasing the active region thickness reduces  $\Gamma$  and according to (2.14) increases the threshold current density of the laser. Therefore, in order to obtain larger  $\Gamma$ , we can add several QWs to the active region and make a multiple quantum well structure (MQW). Replacing a single QW (SQW) with a MQW active region enhances  $\Gamma$  in the optical confinement region. However increasing the number of QWs in the active region lowers the carrier injection efficiency due to the lack of uniform carrier distribution over each well because of energy barriers of adjacent QWs [3]. The number of QWs in lasers

is always a parameter that needs to be carefully chosen in the laser design in order to balance the VCSEL behavior.

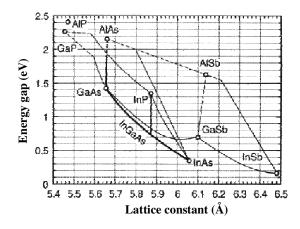

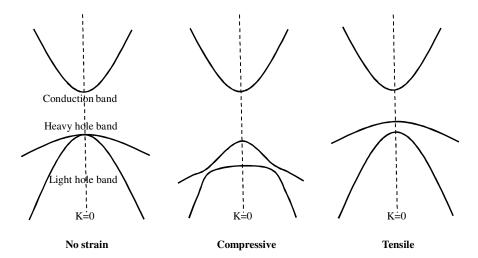

If QWs are grown in a way that both barrier and well materials have equal lattice constant, a, the QW is called unstrained. Otherwise, if barrier and well materials are lattice mismatched, the QW is under strain and called a strained QW. Too much lattice constant mismatch between barrier and well layers is not appropriate since that might cause undesirable defects in the structure. However, in some cases it is useful to grow strained QWs with a small lattice mismatch ( $\Delta a/a \sim 1\%$ ). In a strained QW with the barrier material much thicker than the well material, the well material will be under compressive (tensile) strain if the barrier material has smaller (larger) lattice constant than the well layer. As an example in Figure 2.11, Al<sub>x</sub>Ga<sub>1-x</sub>As/GaAs system makes an unstrained QW, while GaAs/In<sub>x</sub>Ga<sub>1-x</sub>As QW (small x) is a strained one with the well material (InGaAs) under compressive strain.

Figure 2.11 Energy gap vs. lattice constant for some III-V semiconductors (reproduced from [2]).

Strained QWs are interesting in some semiconductor laser applications because of offering some useful properties such as [10]: 1) a wider range of material combinations and thus bandgaps are available, and 2) they allow a certain amount of band structure and hence gain engineering with modifying effective masses. These properties made strained QWs very popular in VCSEL research and technology.

#### 2.5. Current and optical confinement in VCSELs

In order to reach very efficient VCSELs, we need to confine both current and optical field in lateral dimension in a way to have maximum interaction with the active region. Optical field can be confined by either gain-guided or index-guided structures. In a gain-guided laser, the lateral extent of the laser field is controlled by the lateral size of the active region interacting with the field, while for an index-guided laser it is determined by the lateral size of the high refractive index region in a waveguide type configuration. Figure 2.12 shows two important techniques widely used in VCSELs, which are proton-implants for current confinement and oxide for both current and optical confinement. In proton implant which can be considered as a type of gain guided structure (Figure 2.12(a)), an insulating layer is formed by proton (H<sup>+</sup>) bombardment of the structure to limit the current spreading toward the surrounding area. This method was initially very popular for fabricating commercial VCSELs. The oxide-confined structure (Figure 2.12(b)) is another popular configuration of electrical and optical confinement in VCSELs. In oxide confined VCSELs, an Al-containing layer such as AlGaAs is placed in the structure during the growth of DBR mirrors and active layer. Wet oxidation of this layer at elevated temperature forms a mechanically stable phase of Al<sub>2</sub>O<sub>3</sub> which has a low

refractive index [11]. By etching laser mesas to access the AlGaAs layer from the side or bottom of the mesa, we can oxidize the oxide layer up to a certain length which should not exceed the mesa radius. In this case, the center of the mesa, which is unoxidized, has higher refractive index than the oxidized parts and acts as a index-guiding structure. One common method of oxidation is using a flow of water vapor in vicinity of the sample at elevated temperatures. The rate of oxidation can be well-controlled by changing the Al content, oxidation layer thickness, and water vapor and sample temperature [11]. Very high modulation frequency [12] and high efficiency VCSELs [13] have been made from this method.

Figure 2.12 VCSEL confinement by (a) proton implantation and (b) selective oxidation.

#### 2.6. VCSELs: dc and ac response

In this section the rate equations for carrier density in the active region and photon density of an optical mode are employed as a starting point to study semiconductor lasers under dc and ac conditions. Analyzing these two conditions enables us to understand laser dynamics which is a key point of designing lasers with desired operating parameters. The discussion in this section will be applicable to both EELs and VCSELs.

The rate equations under steady-state give us the full understanding of laser behavior under dc bias. For ac analysis, the rate equations can be solved and linearized in the presence of a perturbation, like a modulated input current to yield the small-signal modulation response of a laser. In addition to dc and modulation response, relative intensity noise (RIN) measurement of lasers can help us to find laser dynamics under dc bias such as the experimental data presented in Chapter 6. The use of this technique rather than current modulation response reduces nonlinear large signal effects, simplifies electrical probing requirements, and eliminates convolution with electrical effects due to parasitic circuit elements and impedance matching.

I first start with a steady-state solution in section 2.6.1 and then discuss modulation response and RIN measurement of semiconductor lasers in 2.6.2 and 2.6.3 respectively.

#### 2.6.1. VCSELs under dc condition

Let's start from rate equations for carrier decay, dN/dt, and photon decay, dS/dt. dN/dt can be written as subtracting carrier recombination rate from carrier generation rate. The same logic can be used to write the rate equation for dS/dt. These equations can be written as [2]

$$\frac{dN}{dt} = \frac{\eta_i I}{qV_g} - \frac{N}{\tau} - v_g gS \tag{2.15}$$

$$\frac{dS}{dt} = \Gamma v_g gS + \Gamma \beta_{sp} R_{sp} - \frac{S}{\tau_p}$$

(2.16)

where I is the injected current,  $v_g$  is the photon group velocity, S is photon density,  $\beta_{sp}$  is the spontaneous emission factor,  $R_{sp}$  is the spontaneous recombination rate and  $\tau_p$  is the photon lifetime.

It is important to know that the steady-state gain for a laser operating above threshold should always equal the threshold gain because if the gain is higher than  $g_{th}$ , optical field amplitude continues to increase and obviously this cannot happen in the steady-state. The same argument is valid for steady-state carrier density above threshold because as mentioned earlier, N is monotonically related to g. So in a laser cavity both g and N clamp at steady-state as [2]

$$g(I > I_{th}) = g_{th}$$

(2.17)

$$N(I > I_{th}) = N_{th}$$

(2.18)

Now we have all we need to find the output power of a laser. Laser output power,  $P_{out}$ , can be written as

$P_{out}$ =(Energy of each photon)×(Number of photons in the optical mode)×(Photon escape rate from mirrors)

or

$$P_{out} = h v.SV_p.v_g \alpha_m \tag{2.19}$$

where h is Planck's constant and v is the frequency of each photon. Now let's consider the steady-state situation (dN/dt=0) almost at threshold  $(N=N_{th})$  and  $I=I_{th}$ . In this case (2.15) reduces to

$$\frac{\eta_i I_{th}}{q V_o} = \frac{N_{th}}{\tau} \tag{2.20}$$

Also note that for a laser right below threshold, the net stimulated recombination is negligible, i.e  $R_{st}=v_ggS\approx0$ .

If again we consider the steady-state but at  $I>I_{th}$  and use (2.17), (2.18), and (2.20), (2.15) can be written as

$$\frac{\eta_i}{qV_{\varrho}}(I - I_{th}) = V_g g_{th} S \Rightarrow S = \frac{\eta_i}{qV_{\varrho} V_{\varrho} g_{th}} (I - I_{th})$$

(2.21)

Substituting S from (2.21) into the output power expression (2.18) with  $V_p = V_g / \Gamma$ , one can write output power for  $I > I_{th}$  in the form of

$$P_{out} = h v. \frac{\eta_i}{q V_g v_g g_{th}} (I - I_{th}) \frac{V_g}{\Gamma} v_g \alpha_m$$

$$\Rightarrow P_{out} = \frac{h v \eta_i \alpha_m}{q \Gamma g_{th}} (I - I_{th})$$

(2.22)

or using (2.3) and (2.4) for  $\Gamma g_{th}$

$$P_{out} = \frac{hv}{q} \frac{\eta_i \alpha_m}{\alpha_i + \alpha_m} (I - I_{th})$$

(2.23)

Now with defining a differential quantum efficiency,  $\eta_d$

$$\eta_d = \eta_i \frac{\alpha_m}{\alpha_i + \alpha_m} \tag{2.24}$$

we can simplify (2.23) to be

$$P_{out} = \eta_d \frac{hv}{q} (I - I_{th})$$

(2.25)

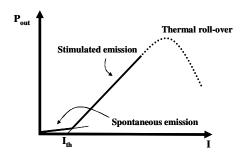

As mentioned before, these equations give  $P_{out}$  for  $I > I_{th}$ ; so, we still need to find  $P_{out}$  at  $I < I_{th}$  where spontaneous emission is the dominant process. It means that we can piece together a below-threshold LED curve with (2.25) to reach a  $P_{out}$  vs. I characteristic for a

semiconductor laser. Output power in an LED is a linear function of input current and can be formulated as [2]

$$P_{out, LED} = \eta_{ex} \frac{hv}{q} I \tag{2.26}$$

where  $\eta_{ex}$  is the external LED quantum efficiency which is the number of photons coupled to the receiving aperture per electron flowing into the LED [2]. Both parts of the laser characteristic are linear functions of current with different slopes. Figure 2.13 shows a typical  $P_{out}$  vs. I characteristic in solid line. In VCSELs due to the generated heat in the small active region,  $P_{out}$  cannot increase monotonically with I and a thermal roll-over causes the power to decrease at large amount of currents which differs from VCSEL to VCSEL. This phenomenon is presented in Figure 2.13 with a dotted curve. Methods of cooling down the active region temperature will be presented in later chapters.

Figure 2.13 Output power vs. current characteristic of a VCSEL.

## 2.6.2. VCSELs modulation response

After solving rate equations under steady-state condition, let's derive small-signal intensity modulation of lasers which is a very important concept in optical communications. Consider an above-threshold dc operation of a diode laser,  $I_0$ , superimposed with a small sinusoidal ac current with amplitude  $I_1$ . In this case carrier and

photon density can also be considered to have the same form as current under an assumption of linearity. So,

$$I = I_0 + I_1 e^{j\omega t}$$

$$N = N_0 + N_1 e^{j\omega t}$$

$$S = S_0 + S_1 e^{j\omega t}$$

(2.27)

Now with substituting (2.27) into the rate equations ((2.15) and (2.16)) and let dc terms cancel out from both sides of the equation in steady-state, we find small signal rate equations

$$j\omega N_{1} = \frac{\eta_{i}I_{1}}{qV_{g}} - \frac{N_{1}}{\tau} - \frac{S_{1}}{\Gamma\tau_{p}} - v_{g}aN_{1}S_{0}$$

(2.28)

$$j\omega S_I = I v_g a N_I S_0 \tag{2.29}$$

In getting to these equations we used  $g_{th}=a(N_0-N_{tr})$  and also photon decay rate  $I/\tau_p=\Gamma g_{th}v_g$ . In order to find frequency response of a diode laser we can define its modulation transfer function as a ratio of ac optical power over input current, i.e.  $P_{ac}(\omega)/I_I(\omega)$  where  $P_{ac}$  is proportional to  $S_I$  as illustrated in (2.19) for a general case. Using (2.28) and (2.29) we can find  $S_I$  to be

$$S_{1} = \frac{(\eta_{i} I_{1} / q V_{g}) \Gamma v_{g} a S_{0}}{R(\omega)}$$

(2.30)

where frequency dependent denominator  $R(\omega)$  is

$$R(\omega) = -\omega^2 + j\omega(\frac{1}{\tau} + v_g aS_0) + \frac{v_g aS_0}{\tau_p}$$

(2.31)

To have the maximum photon density for maximum power,  $|R(\omega)|$  should have its minimum value which occurs at  $\omega = \omega_r$  when  $(\partial/\partial\omega)|R(\omega)|^2 = 0$ .

$$\omega_r^2 = \frac{v_g a S_0}{\tau_p} - \frac{1}{2} (\frac{1}{\tau} + v_g a S_0)^2$$

(2.32)

where the last term is usually negligible compared to the first term and

$$\omega_r^2 \approx \frac{v_g a S_0}{\tau_p} \tag{2.33}$$

This natural resonance frequency,  $\omega_r$ , is referred to as the relaxation oscillation frequency and plays an important role in understanding the high frequency behavior and dynamics of diode lasers. Now we can write the modulation transfer function of a diode laser as a function of  $\omega_r$  and other known parameters.

$$\frac{P_{ac}(\omega)}{I_I(\omega)} = \frac{\eta_d(hv/q)\omega_r^2}{-\omega^2 + \omega_r^2 + j\omega(\frac{1}{\tau} + \tau_p\omega_r^2)}$$

(2.34)

The first thing from (2.34) is that the laser transfer function is much like a second-order low-pass filter response with a resonance frequency and damping factor. When the damping is small, the electrical 3 dB frequency, in which electrical power reaches to half of its dc value, is given by  $\omega_{3dB} = \omega_r \sqrt{1 + \sqrt{2}} \approx 1.55\omega_r$ . In this case optical power reaches to  $\sqrt{1/2}$  of its dc value. Using (2.19) and (2.33) we can express  $\omega_{3dB}$  as a function of output power with small damping.

$$\omega_{3dB} = 1.55 \sqrt{\frac{\eta_i}{\eta_d} \frac{\Gamma a \nu_g}{h v V_g}} \sqrt{P_{out}}$$

(2.35)

It might also be convenient to write (2.34) as a function of input current using (2.25) and again under small damping condition. We have

$$\omega_{3dB} = 1.55 \sqrt{\frac{\eta_i \Gamma a \nu_g}{q V_g}} \sqrt{I - I_{th}}$$

(2.36)

The small-signal modulation response discussed up to this point was under some conditions to simplify the problem. More accurate analysis might be performed with considering nonlinear gain saturation as well as carrier transport effects [2]. Without going through the details of this case, let's first define gain compression factor,  $\varepsilon$ , and a transport factor,  $\chi$ . A more accurate gain equation can be written for  $g \ge 0$  as [2]

$$g(N,S) = \frac{g_0}{I + \varepsilon S} ln(\frac{N}{N_{tr}})$$

(2.37)

where  $g_0$  is a gain coefficient. From (2.36) the differential gain is

$$a = \frac{\partial g}{\partial N} = \frac{g_0}{N(1 + \varepsilon S)} \equiv \frac{a_0}{1 + \varepsilon S}$$

(2.38)

We can also define

$$a_p = -\frac{\partial g}{\partial S} = \frac{\varepsilon g}{1 + \varepsilon S} \tag{2.39}$$

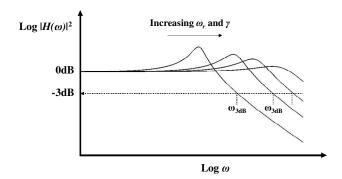

Now let's go back to a normalized general form of a diode laser modulation transfer function,  $H(\omega)$  with relaxation resonance frequency,  $\omega_r$  and damping factor,  $\gamma$ .

$$H(\omega) = \frac{\omega_r^2}{\omega_r^2 - \omega^2 + j\omega\gamma}$$

(2.40)

In Figure 2.14, magnitude squared of the transfer function,  $H(\omega)$  is plotted with increasing relaxation oscillation frequency and damping factor as a function of  $\omega$ . The 3 dB angular frequency is also shown for each curve. Both relaxation oscillation frequency and damping factor increase with increasing the laser bias current.

Figure 2.14 Modulation transfer function for varying values of relaxation oscillation frequency and damping.

Skipping all details, the damping factor when accounting for both gain suppression and transport effects can be expressed as

$$\gamma = K f_r^2 + \gamma_0 \tag{2.41}$$

where

$$K = 4\pi^{2}\tau_{p}(1 + \frac{\Gamma a_{p}}{a/\chi}) \quad \text{and} \quad \gamma_{0} = \frac{1}{\tau_{\Delta N}\chi} + \frac{\Gamma \beta_{sp}R_{sp}}{S}$$

(2.42)

and  $\tau_{\Delta N}$  is the differential carrier lifetime that is typically smaller than  $\tau$  by a factor of 2-3 [2].

From (2.40) and (2.41) with neglecting  $\gamma_0$ , one can find that the maximum possible 3 dB frequency occurs when  $2\omega_r^2 = \gamma^2 = K^2 f_r^4$ . Therefore,

$$f_{3dB,max} = \frac{2\pi\sqrt{2}}{K} \tag{2.43}$$

Notice that  $\omega_r$  approximated by (2.33) is still valid in this case.

In practice, parameters  $\omega_r$  and  $\gamma$  can be extracted from fitting the measured frequency response data to the theoretical  $|H(\omega)|^2$  equation. These two parameters can be

easily altered by changing some laser dynamics introduced earlier in this section. Dynamics can also be affected by changing the external laser parameters such as bias current and temperature. This argument leads us to determining the damping coefficient at threshold,  $\gamma_0$  and the damping parameter, K from fitting (2.41) with the  $\gamma$  vs.  $f_r$  data extracted from frequency response measurement at different laser bias current or temperature to (2.41).

### 2.6.3. Relative intensity noise (RIN)

In the previous section we considered frequency response due to the current modulation. In steady-state it is assumed that carrier and photon densities are constant. However, in reality random carrier and photon recombination and generation produce instantaneous time variations in the carrier and photon densities even with applied dc current [2]. Fluctuations in photon density give rise to the variations in the magnitude of the output power that provides a noise floor and variations in carrier density lead to fluctuations in the output wavelength, which causes the spectrum of the lasing mode to broaden. The intensity noise in optical power contains information on laser relaxation oscillation frequency and damping factor that can be measured while just dc biasing the laser.

RIN is the ratio of the mean-square optical intensity noise,  $\langle \delta P(t)^2 \rangle$  to the square of the average optical power,  $P_0$ .

$$RIN \equiv \frac{\langle \delta P(t)^2 \rangle}{P_0^2}$$

(2.44)

With further simplifications, the RIN spectral density can also be written as [2]

$$\frac{RIN}{\Delta f} = \frac{2hv}{P_0} \left[ \frac{a_1 + a_2\omega^2}{\omega_r^4} \left| H(\omega) \right|^2 + 1 \right]$$

(2.45)

where  $\Delta f$  is the filter bandwidth of the measurement apparatus and  $a_1$  and  $a_2$  are frequency coefficients [2]. It is usually more convenient to express RIN in [dB/Hz] as in (2.45). This equation can be further simplified by introducing new frequency coefficients A and B and using (2.40) for  $H(\omega)$ .

$$\frac{RIN}{\Delta f} = \frac{A + B\omega^2}{(\omega_r^2 - \omega^2)^2 + \omega^2 \gamma^2}$$

(2.46)

RIN measurement offers another method for extracting parameters  $\omega_r$  and  $\gamma$  from fitting (2.46) to the RIN data. RIN can be measured under dc current bias using a spectrum analyzer (SA) system, while for modulation response measurement a modulated current must be added to the laser dc bias current and then the output response must be measured. A vector network analyzer (VNA) is a system that offers both ports for applying and measuring ac signal and measuring the output changes. It is obvious that a photodetector is needed to convert optical signal from the laser to the electrical signal used in both SA and VNA. Calibration requirement in VNAs before measurement and dealing with ac signals make this type of measurement more complicated than SA systems that operate without any involved ac signal and any need for calibration. Also, there are electrical parasitics such as packaging that influence VNA measurement, but not RIN measurement.

## 2.7. Thermal properties of VCSELs

Temperature sensitivity of VCSELs is related to their structure and thermal conductivity of the constituent materials. For an instance, shallower quantum wells (QWs) in red VCSELs cause a weaker carrier confinement and thus greater over-barrier leakage than larger bandgap contrast QW VCSELs. Lower thermal conductivity of materials used in red VCSEL's QWs and DBR mirrors is another drawback to achieving high thermal performance red VCSELs. Therefore, understanding which VCSEL parameters can be altered by elevated temperatures and how temperature affects those parameters are of great importance in designing high temperature performance VCSELs.

### 2.7.1. Temperature effects on VCSEL operation

VCSELs parameters such as lasing wavelength, threshold current, output power, and modulation bandwidth can be affected by device operating temperature. The remainder of this section focuses on the effects of temperature on the above mentioned parameters.

Temperature dependence of longitudinal mode of a VCSEL with longitudinal mode wavelength of  $\lambda_M$  and cavity refractive index of  $n_R$  can be expressed as [14]

$$\frac{d\lambda_{M}}{dT} = \frac{\lambda_{M}}{n_{G}} \left[ \left( \frac{\partial n_{R}}{\partial T} \right) \right]_{\lambda} + n_{R} \alpha_{T}$$

(2.47)

where  $\alpha_T$  is the linear coefficient of thermal expansion and  $n_G$  is the group index given by

$$n_G = n_R - \lambda_M \left( \frac{\partial n_R}{\partial T} \right) \Big|_T \tag{2.48}$$

For an instance, in a GaAs resonance cavity with lasing wavelength of 850 nm,  $\alpha_T$  of  $6.4\times10^{-6}$ /°C [15],  $n_R$  of 3.63 [16],  $n_G$  of 4.3, and  $(\partial n_R/\partial T)|_{\lambda}$ =4×10<sup>-4</sup> K<sup>-1</sup> [14], the rate of longitudinal mode wavelength change with temperature may be estimated from Equation (2.47) to be 0.84 Å/°C. Rate of refractive index change with temperature is about an order of magnitude greater than product of refractive index and coefficient of thermal expansion; therefore, temperature dependence of longitudinal mode is mainly determined by the temperature dependence of refractive index.

Another important parameter in VCSELs that is a function of temperature is threshold current which is determined by the balance between optical gain and losses. Two important effects of increasing temperature in III-V semiconductors are energy gap shrinkage and broadening the carrier density distribution within each band and shifting its peak further into the band. Although these two factors have opposing effects, the energy gap shrinkage is dominant and thus at elevated temperatures, the gain peak shifts to the longer wavelengths and it is also lowered at a given carrier concentration. A typical value for the shift of gain spectrum with temperature in VCSELs is 3.3 Å/°C reported by R. S. Geels et al. for InGaAs MQWs [17]. If optical losses remain unchanged, because of higher current density required to maintain the same gain level, threshold current would increase with temperature. Moreover, since higher density of carriers needed to retain the required gain level, optical losses increase with temperature resulting in increased free carrier absorption in the active region [14]. An Arrhenius-type relation given below is commonly employed to express the temperature dependence of threshold current in semiconductor lasers.

$$I_{th}(T) = I_{th}(300K)e^{(T-300K)/T_0}$$

(2.49)

Characteristic temperature,  $T_0$  is a parameter describing temperature sensitivity of the threshold current and T is the operating temperature in Kelvin. Higher  $T_0$  is favorable for having a device with constant  $I_{th}$  over a certain range of temperature. Although this relation is widely used for EELs, it is not very applicable to VCSELs. When the spacing between longitudinal modes in the resonance cavity is small, the lasing wavelength is determined by the peak of the gain spectrum and thus the operating wavelength follows the gain peak shift with temperature. In contrast, in lasers with a large longitudinal mode spacing, such as VCSELs, the lasing wavelength follows the longitudinal mode shift with temperature. Since the rates of gain peak and cavity mode shift with temperature are different (several times), detuning of cavity mode wavelength with respect to the gain peak varies at different temperatures. This is another factor that results in the temperature dependence of threshold current in VCSELs. VCSELs operate at minimum threshold current at temperatures where the cavity mode and gain peak are relatively aligned. Any nonzero gain-mode offset results in a larger threshold current. Therefore, engineering the gain-mode offset at room temperature is very critical in achieving VCSELs with desired characteristics. For example, designing a VCSEL with a negative gain mode offset at room temperature (i.e. gain peak being blue shifted with respect to the cavity mode wavelength) is favorable for high temperature operation, while a small positive gainmode offset is important for reaching higher bandwidths in VCSELs.

According to Equation (2.18), laser output power is proportional to the number of photons in the cavity, energy of each photon, and escape rate from the mirrors. Laser power varies with temperature mainly due to the reduced number of photons in the cavity

at elevated temperatures. Reduction in internal quantum efficiency is the main effect responsible for the photon density decrease in the active region at high temperatures.

Modulation frequency is another temperature dependent parameter in VCSELs. The 3 dB angular frequency given in Equation (2.35) is related to the output power that varies with temperature as explained above. The frequency might also be temperature dependent through differential gain. Other parameters in the equation are either expected to be relatively constant with temperature or appear as the ratios, e.g.,  $\eta_i/\eta_d$ , that are relatively constant.

### 2.7.2. Material thermal conductivity and laser thermal resistance

Different types of carriers contributing to the thermal conductivity, K, in semiconductors are phonons, photons, electron-hole pairs, and separate electrons and holes [18]. Phonons are the major carriers responsible for heat conduction in relatively pure semiconductors at low temperatures (<600K). Adding a large number of foreign atoms in a semiconductor increases the phonon scattering rate and thus decreases thermal conductivity due to the anharmonicity caused by mass difference between the host lattice and added atom [18]. This concept is more or less what happens in a ternary compound semiconductor. In the  $A_xB_{1-x}C$  compound semiconductor, random distribution of A and B atoms in sublattice sites causes the thermal conductivity to deviate from the linear relation with the mole fraction of one compound x. In this case thermal resistivity, W=1/K, of the ternary material can be written as

$$W(x) = xW_{AC} + (1-x)W_{BC} + x(1-x)C_{A-B}$$

(2.50)

where  $W_{AC}$  and  $W_{BC}$  correspond the thermal resistivity of AC and BC binary compounds and  $C_{A-B}$  is a factor arising from the anharmonicity in the ternary material and can be expressed as [19]

$$C_{A-B} = \left[ \frac{\sqrt{2\pi}}{3} \frac{e\hbar^4 N_{dl}}{(kT)^{1/2} (m_h)^{5/2} (\Delta U_h)^2} \right]$$

(2.51)

where  $N_{dl}$  is the density of alloy sites,  $m_h$  is the hole effective mass, and  $\Delta U_h$  is the alloy scattering potential. Thermal resistivities of some common binary and ternary compound semiconductors together with some useful bowing parameters,  $C_{A-B}$  are given in Table 1 [19].

Table 2.1 Thermal resistivity and bowing parameter for some common compound semiconductors [15], [19].

| Material          | W                         | $C_{A-B}$      |

|-------------------|---------------------------|----------------|

|                   | (cm K/W)                  | (cm K/W)       |

| AlAs              | 1.10                      |                |

| AlP               | 1.1                       |                |

| GaAs              | 2.22                      |                |

| GaP               | 1.3                       |                |

| InAs              | 3.7                       |                |

| InP               | 1.47                      |                |

| $Al_xIn_{1-x}P$   | $1.47+14.63x-15x^{2 (a)}$ | $C_{Al-In}=15$ |

| $Al_xGa_{1-x}As$  | $2.27+28.83x-30x^2$       | $C_{Al-Ga}=32$ |

| $Ga_{x}In_{1-x}P$ | $1.47+71.83x-72x^{2 (a)}$ | $C_{Ga-In}=72$ |

| $In_xGa_{1-x}As$  | $2.27+73.43x-72x^{2 (a)}$ |                |

<sup>(</sup>a) Estimated from Equation (2.50)

For many well-known ternary semiconductor compounds the maximum thermal resistivity occurs at mole fractions around x=0.5 [19].

In the  $A_xB_{1-x}C_yD_{1-y}$  quaternary semiconductor alloy, in addition to considering A-B and C-D disorder due to random distribution of A and B atoms in the cationic and C and D atoms in the anionic sublattices, disordering the cationic and anionic sublattices

also need to be taken into account [20]. These additional alloy scattering terms in quaternary compounds make them to generally have greater thermal resistance than ternary and binary compound semiconductors.

Thermal resistance,  $R_{th}$  (in °C/W), which is a useful parameter for describing VCSEL heating is defined by the ratio of active region temperature raise,  $\Delta T$  and dissipated thermal power,  $\Delta P_{heat}$ , and is given by [21], [22]

$$R_{th} = \frac{\Delta T}{\Delta P_{heat}} \tag{2.52}$$

where  $P_{heat}$ =IV- $P_{opt}$  and I, V, and  $P_{opt}$  are CW current, voltage, and output optical power, respectively.

In experiment, (2.52) can be expanded and  $R_{th}$  can be found as  $R_{th} = (\Delta \lambda / \Delta P_{heat})/(\Delta \lambda / \Delta T)$  which requires two sets of measurements i.e., wavelength shift with dissipated power and wavelength shift with temperature.  $\Delta \lambda / \Delta T$  can be measured by biasing the VCSEL at a fixed current, while changing the stage temperature and monitoring the laser operating wavelength at each temperature. The VCSEL was in the air during the measurement and it is assumed that  $\Delta T_{stage} = \Delta T_{device}$ . The slope of the linear fit to the  $\lambda$  vs. T data gives  $\Delta \lambda / \Delta T$  that can be measured once for a grown epitaxial wafer and used for all VCSELs made on that same material. To find the  $\Delta \lambda / \Delta P_{heat}$  different bias currents are applied to the VCSEL under test and electrical voltage, optical power, and wavelength for each case are measured. The slope of resultant  $\lambda$  vs.  $P_{heat}$  for each VCSEL gives the  $\Delta \lambda / \Delta P_{heat}$  for that specific laser and dividing that number by  $\Delta \lambda / \Delta T$  gives the thermal resistance of the VCSEL.

### References

- [1] Joachim Piprek, Semiconductor Optoelectronic Devices: Introduction to Physics and Simulation, Academic Press, 2003.

- [2] L. A. Coldren and S. W. Corzine, *Diode Lasers and Photonic Integrated Circuits*, Wiley, New York, 1995.

- [3] Takahiro Numai, Fundamentals of Semiconductor Lasers, Springer-Verlag, New York, 2004.

- [4] W. G. Breiland, A. A. Allerman, J. F. Klem, and K. E. Waldrip, "Distributed Bragg reflectors for vertical-cavity surface-emitting lasers," *MRS Bulletin*, July 2002.

- [5] H. Li and K. Iga, Eds., *Vertical-Cavity Surface-Emitting Laser Devices*, Springer-Verlag, Berlin, 2003.

- [6] K. L. Lear and R. P. Schneider, "Uniparabolic mirror grading for vertical cavity surface emitting lasers," *Applied Physics Letters*, vol. 68, pp. 605–607, 1996.

- [7] W. W. Chow and S. W. Koch, Semiconductor-Laser Fundamentals: Physics of the Gain Materials, Springer-Verlag, Berlin, 1999.

- [8] S. M. Sze and Kwok K. Ng, Physics of Semiconductor Devices, 3rd Ed., Wiley, New Jersey, 2007.

- [9] Peter S. Zory, Jr., Ed., Quantum Well Lasers, Academic Press, San Diego, 1993.

- [10] Weng W. Chow, Stephan W. Koch, and Murray Sargent III, Semiconductor-Laser Physics, Springer-Verlag, Berlin, 1994.

- [11] Kent D. Choquette et al., "Advances in selective wet oxidation of AlGaAs alloys," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 3, no. 3, June 1997.

- [12] K.L. Lear et al., "Small and large signal modulation of 850 nm oxide-confined vertical cavity surface emitting lasers," *Advances in Vertical Cavity Surface Emitting Lasers in series OSA Trends in Optics and Photonics*, vol. 15, pp. 69–74, 1997.

- [13] K. L. Lear, K. D. Choquette, R. P. Schneider, S. P. Kilcoyne, and K. M. Geib, "Selectively oxidized vertical cavity surface emitting lasers with 50% power conversion efficiency," *Electronics Letters*, vol. 31, pp. 208–209, 1995.

- [14] Emil Wolf, Ed., *Progress in optics XXXVIII*, Ch. III, Elsevier Science B. V., Amsterdam, 1998.

- [15] Sadao Adachi, "GaAs, AlAs, and Al<sub>x</sub>Ga<sub>1-x</sub>As: Material parameters for use in research and device applications," *Journal of Applied Physics*, vol. 58, no. 3, pp. R1–R29, August 1985.

- [16] www.luxpop.com.

- [17] R. S. Geels, B. J. Thibeault, S. W. Corzine, J. W. Scott, and L. A. Coldren, "Design and characterization of In<sub>0.2</sub>Ga<sub>0.8</sub>As MQW vertical-cavity surface-emitting lasers," *IEEE Journal of Quantum Electronics*, vol. 29, no. 12, pp. 2977–2987, December 1993.

- [18] P. D. Maycock, "Thermal conductivity of silicon, germanium, III–V compounds and III–V alloys," *Solid-State Electronics*, vol. 10, no. 3, pp. 161–168, March 1967.

- [19] Sadao Adachi, "Lattice thermal conductivity of group-IV and III-V semiconductor alloys," *Journal of Applied Physics*, vol. 102, pp. 063502-1–063502-7, 2007.

- [20] W. Nakwaski, "Thermal conductivity of binary, ternary, and quaternary III-V compounds," *Journal of Applied Physics*, vol. 64, no. 1, pp. 159–166, July 1988.

- [21] Joanne S. Manning, "Thermal impedance of diode lasers: Comparison of experimental methods and a theoretical model," *Journal of Applied Physics*, vol. 52, no. 5, pp. 855–862, May 1981.

- [22] R. Pu, C. W. Wilmsen, K. M. Geib, and K. D. Choquette, "Thermal resistance of VCSEL's bonded to integrated circuits," *IEEE Photonics Technology Letters*, vol. 11, no. 12, pp. 1554–1556, Dec., 1999.

# Chapter 3

## **VCSELS: THEIR BIRTH TO RECENT DEVELOPMENTS**

## 3.1. Historical overview of surface emitting lasers (SELs)

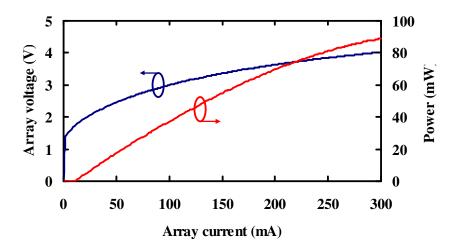

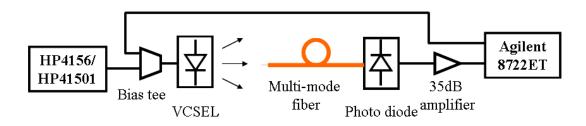

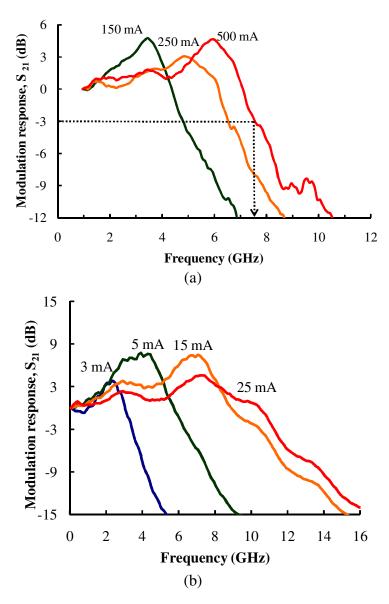

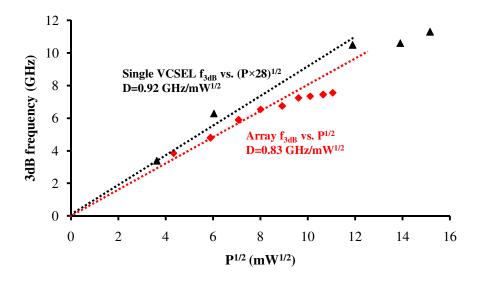

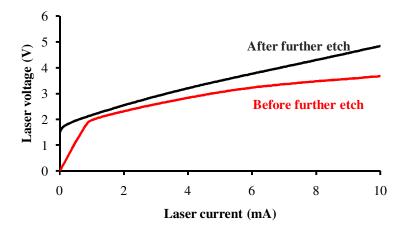

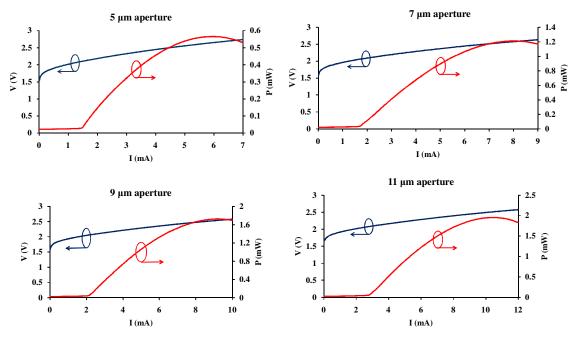

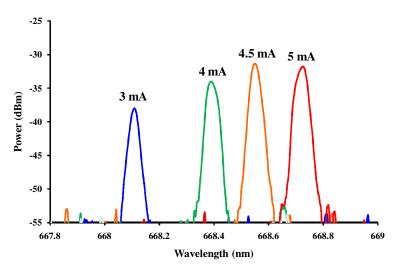

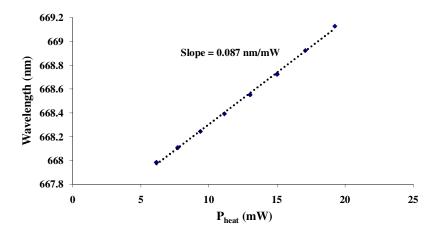

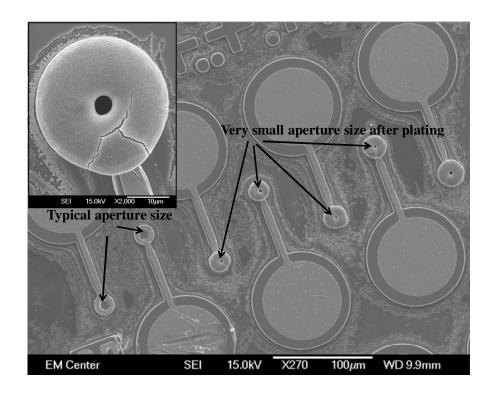

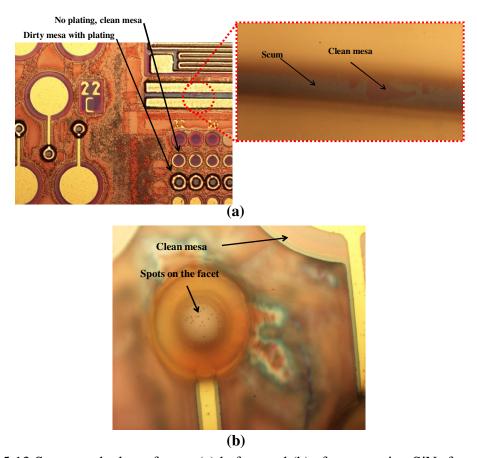

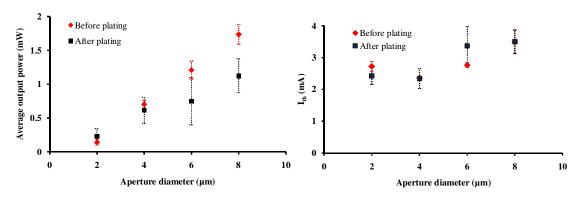

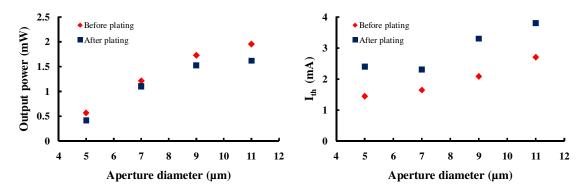

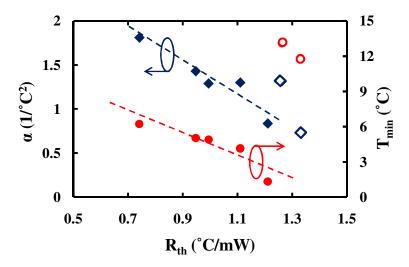

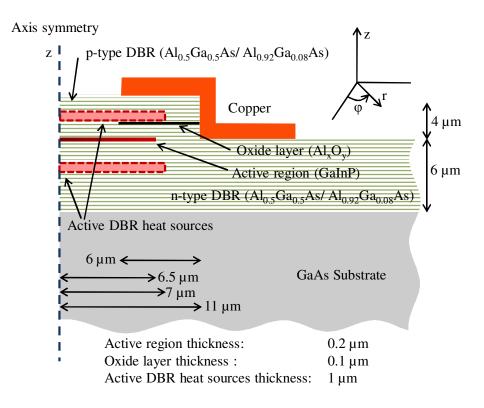

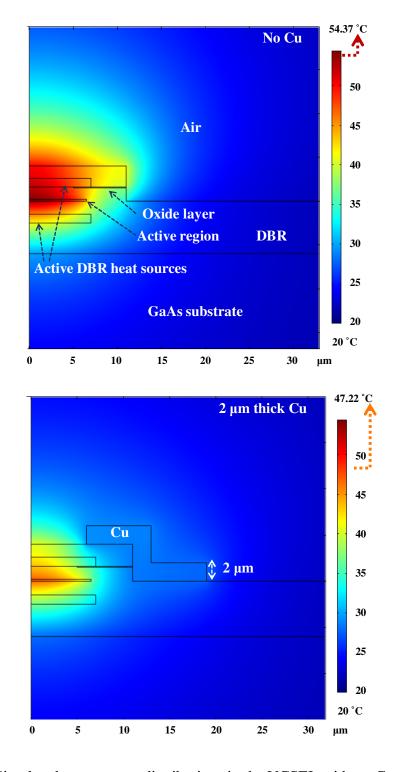

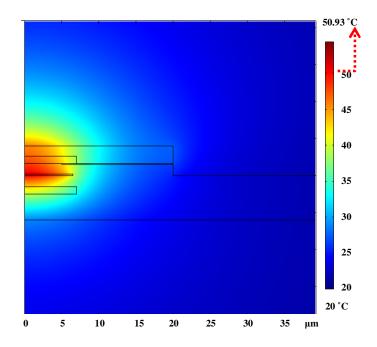

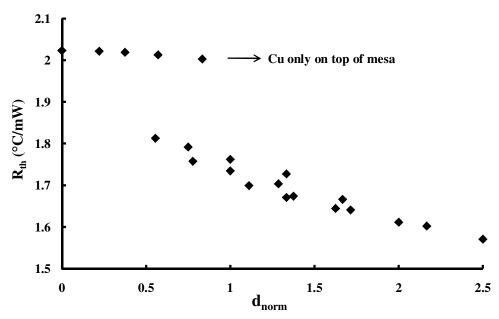

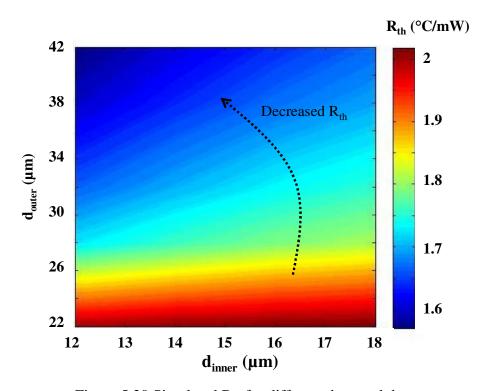

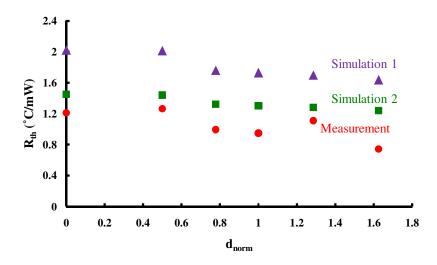

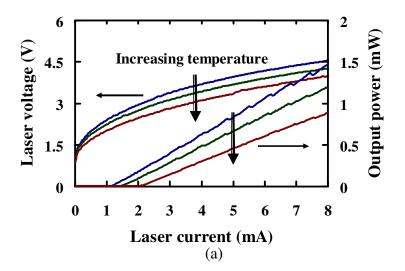

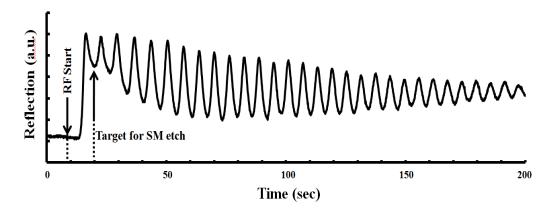

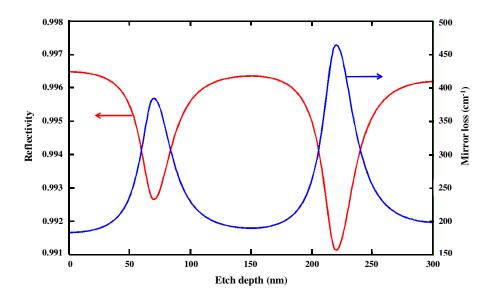

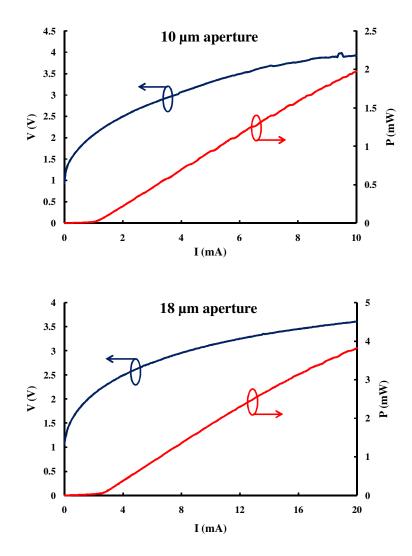

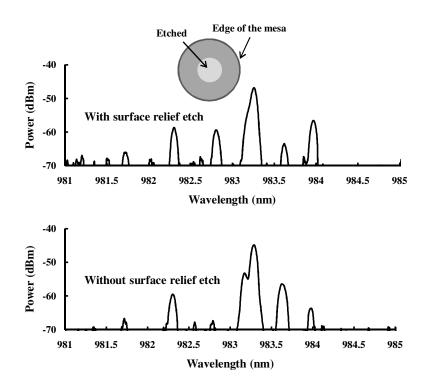

Surface emitting lasers (SELs) were first invented in 1977 by Kenichi Iga of Tokyo Institute of technology [1]. He proposed the initial idea in 1978 at a conference while the first lasing operation of a SEL was reported by him and his colleagues in 1979 based on a GaInAsP/InP double-heterostructure (DH) [2]. The structure contained a stack of an ntype InP layer, an undoped GaInAsP active layer, and a p-type InP layer that were grown on a n-type InP substrate by the liquid phase epitaxy (LPE) technique. They employed metal coated top and bottom surfaces to form a resonant cavity. The laser driven by current pulses at 77 K showed a threshold current density of 11 kA/cm<sup>2</sup> (~0.9 A) and operating wavelength of 1.18 μm. Z. L. Liau and J. N. Walpole developed a room temperature continuous wave (CW) low threshold current, I<sub>th</sub>=12 mA and high differential quantum efficiency, η<sub>d</sub>=47% surface-emitting GaInAsP/InP laser in Lincoln Laboratory, MIT, in 1985, while they mounted the laser on a copper substrate as a heatsink [3]. The next step in realizing a low threshold current SEL happened in 1987 in which the first demonstration of a microcavity GaAlAs/GaAs SEL operating at 880 nm was reported with  $\eta_d=9\%$ ,  $I_{th}=4.5$  and 6 mA at 77 K for CW and pulsed operation, respectively [4].