## **DISSERTATION**

# DESIGN AND SYNTHESIS OF HYBRID NANOPHOTONIC-ELECTRIC NETWORK-ON-CHIP ARCHITECTURES

## Submitted by

## Shirish Bahirat

Department of Electrical and Computer Engineering

In partial fulfillment of the requirements

For the Degree of Doctor of Philosophy

Colorado State University

Fort Collins, Colorado

Spring 2014

## **Doctoral Committee:**

Advisor: Sudeep Pasricha

Wim Bohm T. W. Chen H.J. Siegel Copyright by Shirish Bahirat 2014

All Rights Reserved

#### **ABSTRACT**

# DESIGN AND SYNTHESIS OF HYBRID NANOPHOTONIC-ELECTRIC NETWORK-ON-CHIP ARCHITECTURES

With increasing application complexity and improvements in CMOS process technology, chip multiprocessors (CMPs) with tens to hundreds of cores on a chip are today becoming a reality. Networks on Chip (NoCs) have emerged as a scalable communication fabric that can support high bandwidth communications in such massively parallel multi-core systems. However, traditional electrical NoC implementations today face significant challenges due to high data transfer latencies, low throughput, and high power dissipation. Silicon nanophotonics on a chip has recently been proposed to overcome limitations of electrical wires. However, designing and optimizing hybrid electro-photonic NoCs requires complex trade-offs and overcoming many design challenges such as thermal tuning, power, and crossing loss overheads.

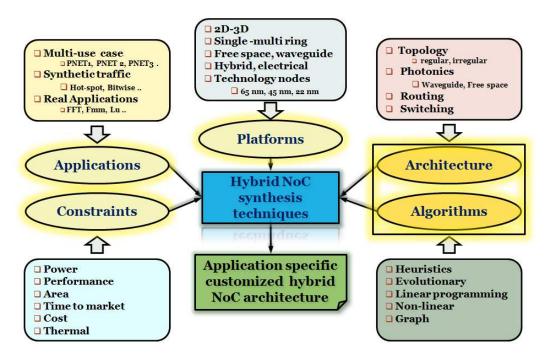

In this thesis, these challenges are addressed by proposing novel hybrid electro-photonic NoC architectures and novel synthesis hybrid NoC frameworks for emerging CMPs. The proposed hybrid electro-photonic NoC architectures are designed for waveguide-based and free-space-based silicon nanophotonics implementations. These architectures are optimized for low-cost, low-power, and low-area overhead, support dynamic reconfiguration to adapt the changing runtime traffic requirements, and have been adapted for both 2D and 3D CMPs. The proposed synthesis frameworks utilize various optimization algorithms such as evolutionary techniques, linear programming, and custom heuristics to perform rapid design space exploration of hybrid electro-photonic (2D and 3D) NoC architectures and trade-off performance and power

objectives. Experimental results indicate a strong motivation to consider the proposed architectures for future CMPs, with several orders of magnitude reduction in power consumption and improvements in network throughput and access latencies, compared to traditional electrical 2D and 3D NoC architectures. Compared to other previously proposed hybrid electro-photonic NoC architectures, the proposed architectures are also shown to have lower photonic area overhead, power consumption, and energy-delay product, while maintaining competitive throughput and latency. Unlike any prior work to date, our synthesis frameworks allow further tuning and customization of our proposed architectures to meet designer-specific goals. Together, the architectural and synthesis framework contributions bring the promise of silicon nanophotonics in future massively parallel CMPs closer to reality.

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to extend my sincere gratitude to my advisor Dr. Sudeep Pasricha who continuously inspired me and provided vast guidance towards the completion of this research. About six years ago, when I decided to work on my PhD, I visited many professors and universities in Denver area to communicate my interests and how it can line up with the upcoming technological challenges in the next 10 years. I still remember the first meeting I had with Dr. Sudeep Pasricha that was scheduled for about 30 min, however I kept discussing the research possibilities for about 40~45 minutes, after that I never looked back as I was fortunate enough to join his research team. The course and research work I did under the guidance of Dr. Sudeep Pasricha truly helped me to develop expertise from silicon-to-system. His words of wisdom enabled me to learn cutting edge technologies by understanding and addressing many of the challenges faced by industry as well as the research community. By providing focus on critical and valuable research problems and practical solutions, he helped me to get visibility for my research within well-known conferences, journals and institutions. Dr. Sudeep Pasricha is dynamic, enthusiastic, energetic and full of many ideas, which truly makes him one of the greatest advisers and Professors I have known and worked with. The regular brainstorming sessions with Dr. Sudeep Pasricha provided me great insight on many technological areas. I am truly grateful for his excellent guidance and support over the past six years. Without his guidance and help, this research work was definitely not possible. I recall our brainstorming sessions for every research paper or publication that I worked on, and always felt that I was full of ideas to try solving the next set of challenges every time walking out of his office. I performed many "what-if' analysis cases" to obtain the best possible solutions. Dr. Sudeep Pasricha always kept

raising the bar and always pushed me to do better in every aspect of research. I was also fortunate to attend a number of conferences and present my work in front many researchers and the engineering community. The exciting feedback and awards received during these conferences speaks for itself about the high standard that Dr. Sudeep Pasricha adheres to in all aspects of research that includes every major and minor aspect of research. If I look back, not only have I gained technical knowledge but his guidance has also helped to improve my presentation, communication, and writing skills.

I would like to take this opportunity to thank the respected members of my PhD committee, Dr. Wim Bohm, Dr. T. W. Chen and Dr. H.J. Siegel for their insightful feedback and encouragement for my research. The feedback they provided me helped to enhance and broaden my research. I am also thankful to the many students in Dr. Pasricha's MECS lab for their support and help during my PhD: Ishan Thakkar, Yi Xiang, Yong Zou, C Sai Vineel Reddy, Tejasi Pimpalkhute, Nishit Kapadia, Mark Oxley, Dalton Young and Srinivas Desai. Also this list cannot be complete without mentioning Aditi Kulkarni, Jonathan Apodaca and Jay Smith with whom I worked during my course work and publications and received valuable feedback on many aspects about my work. Weekly team meetings managed by Dr. Sudeep Pasricha helped to institutionalize the knowledge through the presentations and discussions with all team members.

Last but not least, I would like to thank my family for their support to continue my research. My wife Pooja, son Ameya and daughter Neha encouraged and supported me to continue my studies and inspired me to keep going while managing multiple priorities with my family, studies, and job. This achievement was not possible without their immense support.

# **DEDICATION**

To my parents, beautiful wife Pooja, amazing son Ameya and wonderful daughter Neha, all of my friends and family

and

to the memory of my grandfather Dr. B. P. Bahirat and father-in-law V.M Kulkarni

# TABLE OF CONTENTS

| AB  | STR   | ACT                                                    | ii    |

|-----|-------|--------------------------------------------------------|-------|

| AC  | CKNC  | OWLEDGEMENTS                                           | iv    |

| DE  | DICA  | ATION                                                  | vi    |

| LIS | ST OF | TABLES                                                 | xii   |

| LIS | ST OF | F FIGURES                                              | xiii  |

| LIS | ST OF | F KEYWORDS                                             | xix   |

| 1   | INT   | TRODUCTION                                             | 1     |

|     | 1.1   | MOTIVATION                                             | 1     |

| -   | 1.2   | TECHNOLOGY TRENDS                                      | 3     |

| -   | 1.3   | NETWORKS-ON-CHIP (NOC)                                 | 6     |

| -   | 1.4   | HYBRID NANOPHOTONIC NOC BASED ON WAVEGUIDES            | 9     |

| -   | 1.5   | ON-CHIP WAVEGUIDE PHOTONIC COMMUNICATION BUILDING BLOC | KS 11 |

| -   | 1.6   | ON CHIP FREE SPACE COMMUNICATION BUILDING BLOCKS       | 13    |

| -   | 1.7   | 3D NOC INTERCONNECTS                                   | 15    |

| -   | 1.8   | HYBRID NANOPHOTONIC-ELECTRIC NOC SYNTHESIS             | 17    |

| -   | 1.9   | CONTRIBUTIONS                                          | 19    |

| -   | 1.10  | OUTLINE                                                | 21    |

| 2   | LIT   | TERATURE SURVEY                                        | 23    |

| 2   | 2.1   | 2D AND 3D ELECTRICAL NOC ARCHITECTURES                 | 23    |

| 2   | 2.2   | PHOTONIC NOC ARCHITECTURES                             | 25    |

| 2   | 2.3   | NOC SYNTHESIS                                          | 30    |

| 3   |       | TTEOR: HYBRID PHOTONIC RING-MESH NOC FOR MULTICORE     |       |

|     |       | ΓECTURES                                               |       |

|     | 3.1   | SYSTEM LEVEL ARCHITECTURE                              |       |

|     | 3.2   | PHOTONIC REGIONS OF INFLUENCE (PRI)                    |       |

|     | 3.3   | ROUTING AND FLOW CONTROL                               |       |

| 3   | 3.4   | DEADLOCK RECOVERY                                      | -     |

| 1   | 3 5   | COMMUNICATION SERIALIZATION                            | 42    |

|   | 3.6 | EX  | PERIMENTAL RESULTS                                | 44  |

|---|-----|-----|---------------------------------------------------|-----|

|   | 3.7 | SIN | MULATION SETUP                                    | 44  |

|   | 3.7 | .1  | PERFORMANCE AND POWER ESTIMATION MODELS           | 47  |

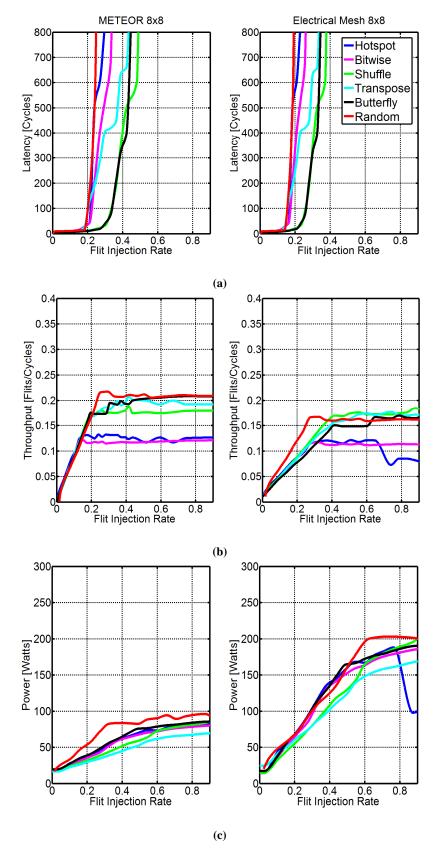

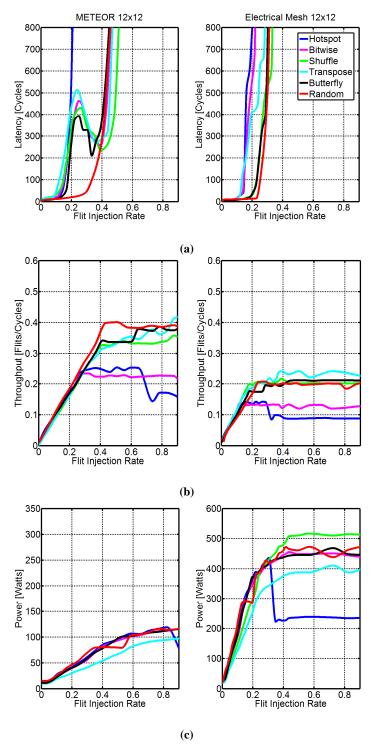

|   | 3.7 | .2  | COMPARISON WITH ELECTRICAL MESH NOC               | 51  |

|   | 3.7 | .3  | IMPACT OF VARYING PRI SIZE                        | 52  |

|   | 3.7 | .4  | IMPACT OF CHANGING NUMBER OF PHOTONIC UPLINKS     | 54  |

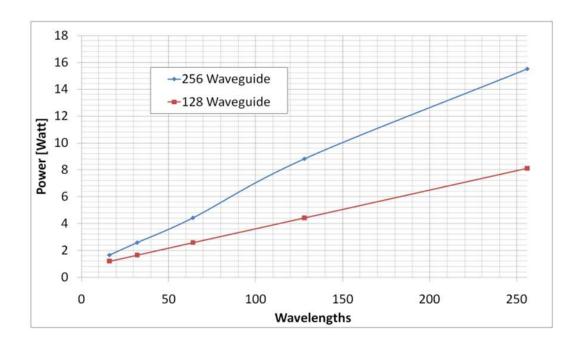

|   | 3.7 | .5  | IMPACT OF VARYING NUMBER OF WAVELENGTHS           | 57  |

|   | 3.7 | .6  | IMPACT OF PHOTONIC SERIALIZATION                  | 58  |

|   | 3.7 | .7  | COMPARISON WITH OTHER PHOTONIC NOCS               | 64  |

|   | 3.8 | RE  | SULT SUMMARY                                      | 69  |

| 4 | HY  | BRI | D PHOTONIC NOC FOR MULTIPLE USE-CASE APPLICATIONS | 70  |

|   | 4.1 | MU  | ILTIPLE USE-CASE APPLICATIONS                     | 70  |

|   | 4.2 | ON  | CHIP PHOTONIC ARCHITECTURE OVERVIEW               | 75  |

|   | 4.3 | UC  | -PHOTON OVERVIEW                                  | 78  |

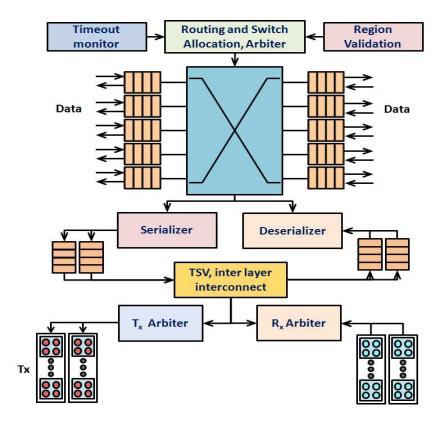

|   | 4.3 | .1  | BACKGROUND                                        |     |

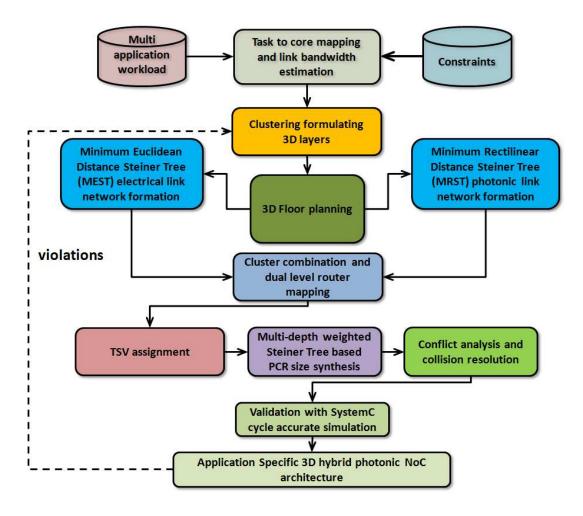

|   | 4.3 | .2  | TOPOLOGY                                          | 80  |

|   | 4.3 | .3  | ROUTING AND FLOW CONTROL                          | 81  |

|   | 4.3 | .4  | DYNAMIC CONFIGURATION                             | 84  |

|   | 4.4 | EX  | PERIMENTS                                         |     |

|   | 4.4 | .1  | EXPERIMENTAL SETUP                                | 87  |

|   | 4.4 | .2  | RESULTS                                           | 89  |

|   | 4.5 | RE  | SULT SUMMARY                                      | 94  |

| 5 | OP  | AL: | A MULTI-LAYER HYBRID PHOTONIC NOC FOR 3D ICS      | 96  |

|   | 5.1 | MC  | TIVATION FOR MULTIPLE PHOTONIC LAYERS IN 3D ICS   | 96  |

|   | 5.2 |     | AL SYSTEM LEVEL ARCHITECTURE                      |     |

|   | 5.3 | 3D  | PHOTONIC REGION OF INFLUENCE (3D-PRI)             | 101 |

|   | 5.4 | RO  | UTER ARCHITECTURE                                 | 101 |

|   | 5.5 |     | UTING AND FLOW CONTROL                            |     |

|   | 5.6 |     | ADLOCK AVOIDANCE                                  |     |

|   | 5.7 | RU  | NTIME OPTIMIZATIONS                               | 106 |

|   | 57  | 1   | DVS/DFS                                           | 106 |

|         |     | 5.7 | .2  | DYNAMIC WDM                                                                         | 106 |

|---------|-----|-----|-----|-------------------------------------------------------------------------------------|-----|

|         |     | 5.7 | .3  | 3D-PRI RECONFIGURATION                                                              | 107 |

|         | 5.8 | 8   | EXI | PERIMENTS                                                                           | 107 |

|         |     | 5.8 | .1  | EXPERIMENTAL SETUP                                                                  | 107 |

|         | 5.9 | 9   | RES | SULTS                                                                               | 108 |

|         |     | 5.9 | .1  | COMPARISONS WITH 2D AND 3D ELECTRICAL MESH NOC                                      | 108 |

|         |     | 5.9 | .2  | IMPACT OF VARYING NUMBER OF UPLINKS                                                 | 110 |

|         |     | 5.9 | .3  | IMPACT OF ENABLING RUNTIME ADAPTATIONS                                              | 111 |

|         |     | 5.9 | .4  | COMPARISON WITH EXISTING HYBRID PHOTONIC NOCS                                       | 113 |

|         | 5.1 | 10  | R   | ESULT SUMMARY                                                                       | 115 |

| 6<br>N. |     |     |     | IESIS FRAMEWORK FOR APPLICATION-SPECIFIC HYBRID FONIC-ELECTRIC NOCS WITH WAVEGUIDES | 116 |

|         | 6.1 | 1   | МО  | TIVATION FOR HYBRID NOC SYNTHESIS                                                   | 116 |

|         | 6.2 | 2   | HY  | BRID PHOTONIC NOC ARCHITECTURE OPTIMIZATION PARAMETERS                              | 118 |

|         |     | 6.2 | .1  | PRI-AWARE ROUTING                                                                   | 119 |

|         |     | 6.2 | .2  | PHOTONIC RING CONFIGURATION                                                         | 119 |

|         |     | 6.2 | .3  | FLOW CONTROL                                                                        | 120 |

|         |     | 6.2 | .4  | SERIALIZATION                                                                       | 121 |

|         | 6.3 | 3   | PRO | DBLEM FORMULATION                                                                   | 122 |

|         | 6.4 | 4   | SYN | NTHESIS FRAMEWORK OVERVIEW                                                          | 123 |

|         |     | 6.4 | .1  | CORE TO TILE MAPPING                                                                | 124 |

|         |     | 6.4 | .2  | NOC SYNTHESIS                                                                       | 125 |

|         | 6.5 | 5   | CYO | CLE ACCURATE SIMULATION AND VALIDATION                                              | 139 |

|         | 6.6 | 5   | EXI | PERIMENTS                                                                           | 140 |

|         |     | 6.6 | .1  | EXPERIMENTAL SETUP                                                                  | 140 |

|         |     | 6.6 | .2  | RESULTS                                                                             | 142 |

|         | 6.7 | 7   | RES | SULT SUMMARY                                                                        | 153 |

| 7<br>SI |     |     |     | DESIGN AND SYNTHESIS OF HYBRID FREE SPACE APPLICATION-OC ARCHITECTURES              | 154 |

|         | 7.1 | 1   | HY  | BRID PHOTONIC FREE SPACE NOC ARCHITECTURE OVERVIEW                                  | 154 |

|         | 7   | ,   | CVN | NTHESIS PROBLEM FORMULATION                                                         | 158 |

|    | 7.2   | 2.1         | APPLICATION WORKLOAD CONSTRAINTS                            | 158 |

|----|-------|-------------|-------------------------------------------------------------|-----|

|    | 7.2   | 2.2         | SOC PLATFORM CONSTRAINTS                                    | 158 |

|    | 7.2   | 2.3         | PROBLEM OBJECTIVE                                           | 159 |

|    | 7.2   | 2.4         | CONFIGURATION PARAMETERS                                    | 159 |

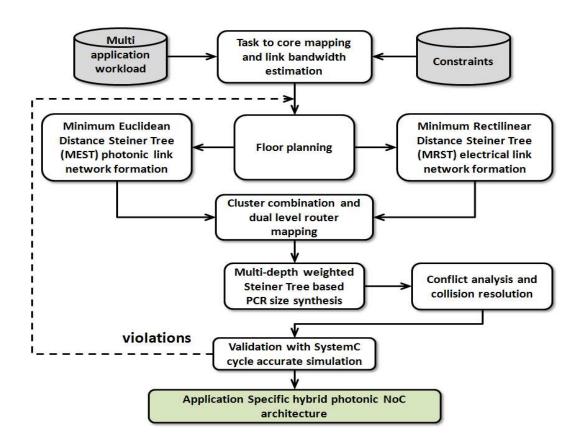

|    | 7.3   | HE          | LIX SYNTHESIS FRAMEWORK OVERVIEW                            | 159 |

|    | 7.3   | <i>3.1</i>  | TASK TO CORE MAPPING                                        | 161 |

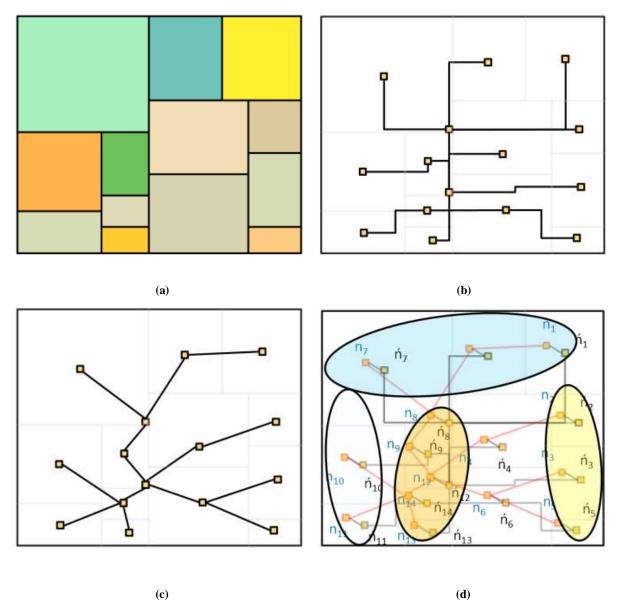

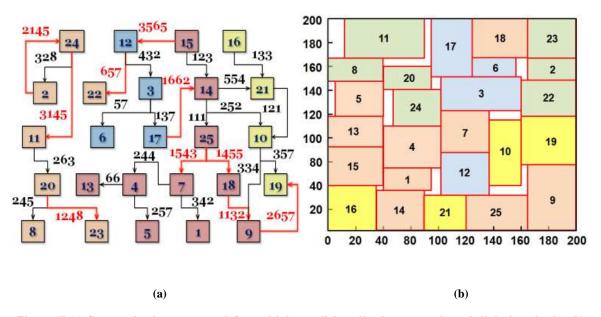

|    | 7.3   | 3.2         | FLOORPLANNING                                               | 162 |

|    | 7.3   | 3.3         | MEST AND MRST BASED NETWORK FORMATION                       | 163 |

|    | 7.3   | 3.4         | CLUSTERING AND DUAL LEVEL ROUTER MAPPING                    | 164 |

|    | 7.3   | 3.5         | PCR SIZE SYNTHESIS                                          | 165 |

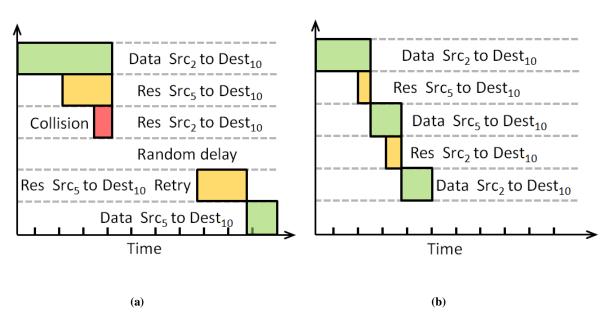

|    | 7.3   | 3.6         | CONFLICT ANALYSIS AND RESOLUTION                            | 166 |

|    | 7.4   | EX          | PERIMENTS                                                   | 167 |

|    | 7.4   | <b>l</b> .1 | EXPERIMENTAL SETUP                                          | 167 |

|    | 7.4   | 1.2         | EXPERIMENTAL RESULTS                                        | 172 |

|    | 7.5   | RE          | SULT SUMMARY                                                | 178 |

| 3  |       |             | LIX: DESIGN AND SYNTHESIS OF HYBRID FREE SPACE APPLICATION- |     |

| SI | PECIF |             | D NOC ARCHITECTURES                                         |     |

|    | 8.1   |             | OTIVATION FOR 3D INTEGRATION                                |     |

|    | 8.2   |             | CKGROUND: FSNPI ARCHITECTURE                                |     |

|    | 8.3   | PR          | OBLEM FORMULATION                                           |     |

|    | 8.3   | 3.1         | APPLICATION WORKLOAD CONSTRAINTS                            |     |

|    | 8.3   | 3.2         | SOC PLATFORM CONSTRAINTS                                    | 186 |

|    | 8.3   | 3.3         | PROBLEM OBJECTIVE                                           | 187 |

|    | 8.3   | 3.4         | CONFIGURATION PARAMETERS                                    | 187 |

|    | 8.4   | 3D-         | -HELIX SYNTHESIS FRAMEWORK OVERVIEW                         | 187 |

|    | 8.4   | 1.1         | TASK TO CORE MAPPING                                        | 188 |

|    | 8.4   | 1.2         | CLUSTER FORMULATION FOR 3D LAYERS                           | 189 |

|    | 8.4   | 1.3         | FLOORPLANNING                                               | 190 |

|    | 8.4   | 1.4         | MEST AND MRST BASED NETWORK FORMATION                       | 191 |

|    | 8.4   | 1.5         | CLUSTERING AND DUAL LEVEL ROUTER MAPPING                    | 192 |

|    | 8 4   | l 6         | TSV ASSIGNMENT                                              | 193 |

|   | 8.4.7  | PCR SIZE SYNTHESIS                 |     |

|---|--------|------------------------------------|-----|

|   | 8.4.8  | CONFLICT ANALYSIS AND RESOLUTION   | 194 |

|   | 8.5 EX | XPERIMENTS                         | 196 |

|   | 8.5.1  | APPLICATIONS                       | 196 |

|   | 8.5.2  | EXPERIMENTAL SETUP                 | 197 |

|   | 8.5.3  | EXPERIMENTAL RESULTS               | 203 |

|   | 8.5.4  | SUMMARY OF RESULTS                 | 205 |

| ) | CONC   | CLUSION AND FUTURE WORK DIRECTIONS | 207 |

|   | 9.1 R  | ESEARCH SUMMARY                    | 207 |

|   | 9.2 FU | UTURE RESEARCH                     | 211 |

# LIST OF TABLES

| Table 1 Serialization link bandwidth                                                     | 43  |

|------------------------------------------------------------------------------------------|-----|

| Table 2 Delay and power of photonic components                                           | 47  |

| Table 3 Micro ring resonator requirement                                                 | 65  |

| Table 4 Multi use-case application characteristics                                       | 87  |

| Table 5 Delay of PHOTON components at 32nm                                               | 88  |

| Table 6 Synthesis parameters                                                             | 122 |

| Table 7 PSO synthesis results                                                            | 147 |

| Table 8 ACO synthesis results                                                            | 147 |

| Table 9 SA synthesis results                                                             | 148 |

| Table 10 GA synthesis results                                                            | 148 |

| Table 11 MiBench Applications for Application Categories                                 | 167 |

| Table 12 Communication Synthesis GA Parameter Ranges                                     | 168 |

| Table 13 Comparison of Synthesis Parameters                                              | 175 |

| Table 14 MiBench [172] applications for application categories and number of processors. | 194 |

| Table 15 Communication Synthesis GA Parameter Ranges                                     | 196 |

# LIST OF FIGURES

| Figure 1 Modern processors (a) Intel 6 Core I7 950 3.06GHz, 2012 (b) Tilera Tile-Gx72 system-on-chip, 2013                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2 Node size Vs power density data from Intel <sup>®</sup> [2]                                                                                                                                                                                                                                                                                                       |

| Figure 3 (a) Gate logic delay is decreasing, wire delay is increasing, and gate to wire performance gap is increasing with technology scaling [4] (b) optimal wire length and distance travelled in a single clock cycle is decreasing [2]                                                                                                                                 |

| Figure 4 Networks-On-Chip (NoC), C: processor core, M: memory banks D: digital signal processors F: floating point processors P: global power management module                                                                                                                                                                                                            |

| Figure 5 Electrical NoC router                                                                                                                                                                                                                                                                                                                                             |

| Figure 6 3D IC implementation of a hybrid photonic NoC with cores (bottom layer) and photonic waveguide (top layer) [22]                                                                                                                                                                                                                                                   |

| Figure 7 Global/long distance communication, nano-photonic power stays constant/low while electrical communication power increases as a function of distance travelled                                                                                                                                                                                                     |

| Figure 8 On-chip waveguide photonic transmission components                                                                                                                                                                                                                                                                                                                |

| Figure 9 Building blocks of free-space on-chip photonic interconnects                                                                                                                                                                                                                                                                                                      |

| Figure 10 Conceptual view of CMOS integrated free-space on-chip optical link [28]                                                                                                                                                                                                                                                                                          |

| Figure 11 Conceptual view of 3D CMOS IC with logic and FSNPI layers [35]                                                                                                                                                                                                                                                                                                   |

| Figure 12 Modern CMP design flow                                                                                                                                                                                                                                                                                                                                           |

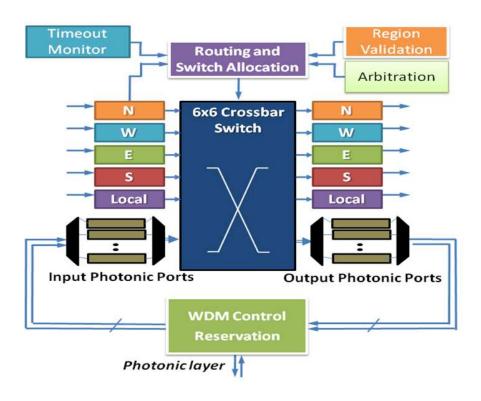

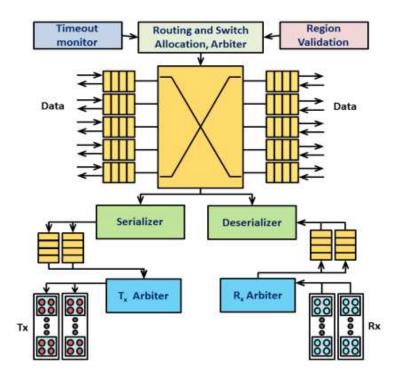

| Figure 13 Gateway interface electrical router architecture                                                                                                                                                                                                                                                                                                                 |

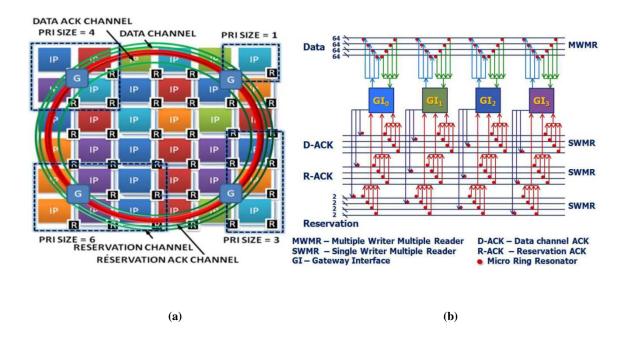

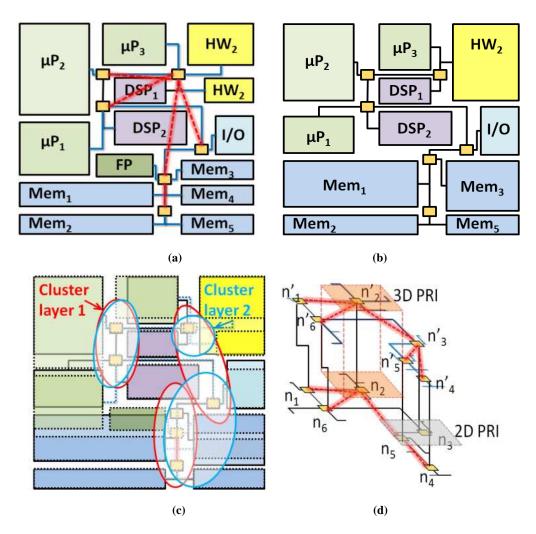

| Figure 14 (a) Photonic regions of influence (PRI) (b) SWMR reservation channels and MWMR data channels                                                                                                                                                                                                                                                                     |

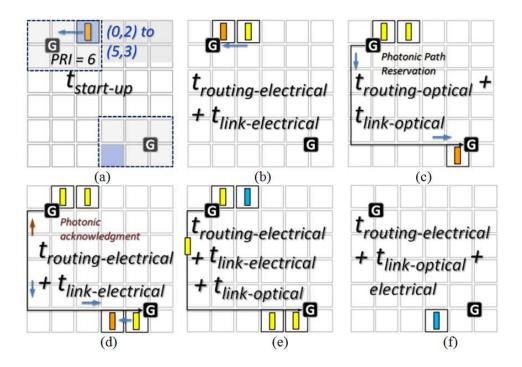

| Figure 15 Flit life cycle during inter-PRI wormhole routing path (a) processor initiates communication (b) header flit (orange) is routed to nearest gateway (c) communication of header through photonic path (d) header flit completes path reservation and reaches destination (e) data flit (yellow) transmission continues (f) path is dismantled by tail flit (blue) |

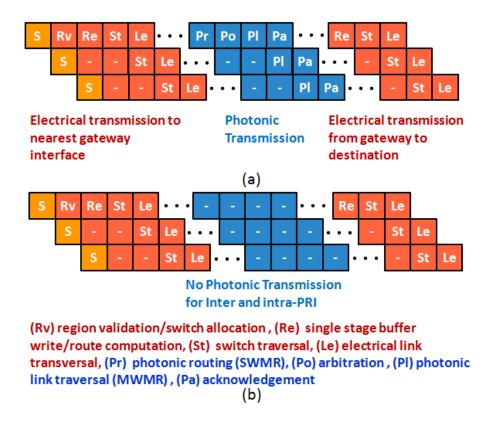

| Figure 16 Head, body and tail flit routing pipeline for (a) inter PRI transfer (b) intra-PRI and non-PRI transfer, dots represent multiple data flit transfers             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

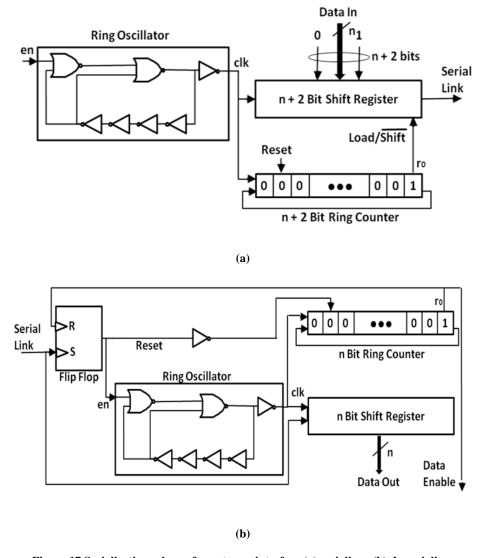

| Figure 17 Serialization scheme for gateway interface (a) serializer, (b) de-serializer 41                                                                                  |

| Figure 18 SPLASH-2 implementation traffic maps for 8x8 CMP                                                                                                                 |

| Figure 19 METEOR laser power for different degrees of WDM                                                                                                                  |

| Figure 20 <i>METEOR</i> vs. electrical mesh NoC for an 8x8 NoC (a) average latency, (b) throughput, (c) power                                                              |

| Figure 21 <i>METEOR</i> vs. electrical mesh NoC for a 12x12 NoC (a) average latency, (b) throughput, (c) power                                                             |

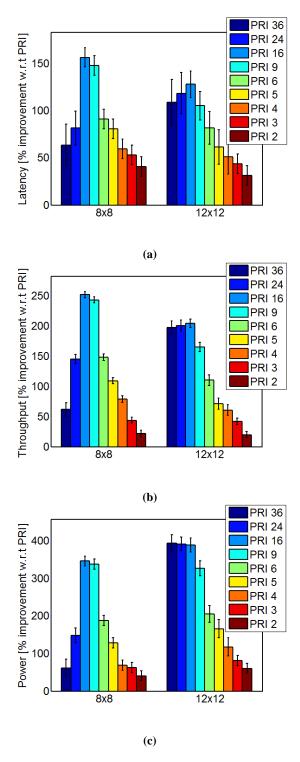

| Figure 22 Relative impact of varying photonic region of influence (PRI) size in <i>METEOR</i> on (a) average latency, (b) throughput (c) power                             |

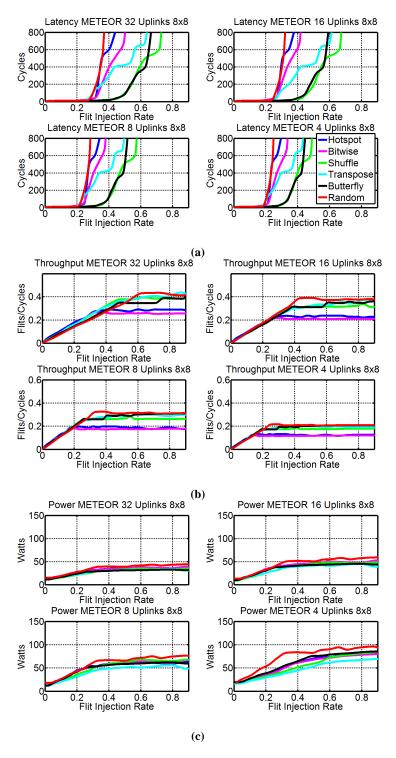

| Figure 23 Impact of varying number of uplinks in <i>METEOR</i> for 8x8 NoC (a) average latency, (b) throughput (c) power consumption                                       |

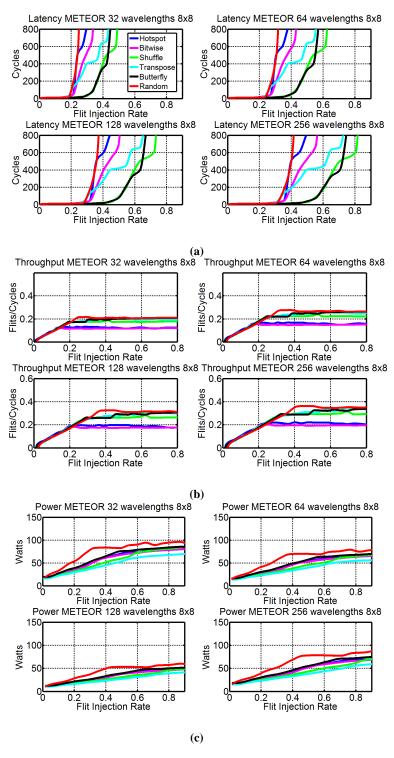

| Figure 24 Impact of varying number of wavelengths in <i>METEOR</i> for 8x8 NoC (a) average latency, (b) throughput (c) power consumption                                   |

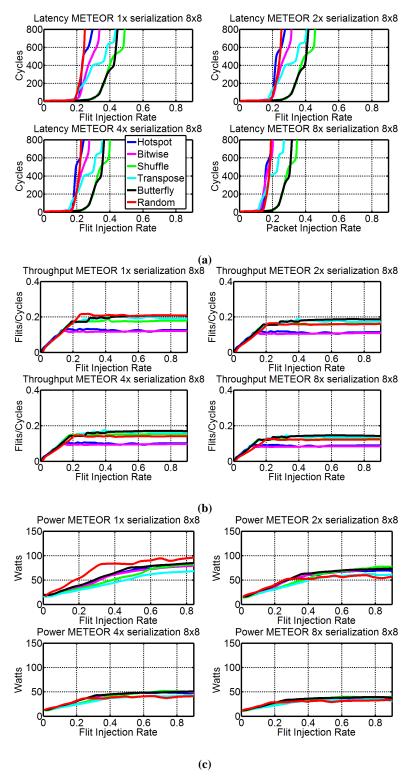

| Figure 25 Impact of varying serialization degree in <i>METEOR</i> for 8x8 NoC (a) average latency, (b) throughput (c) power consumption59                                  |

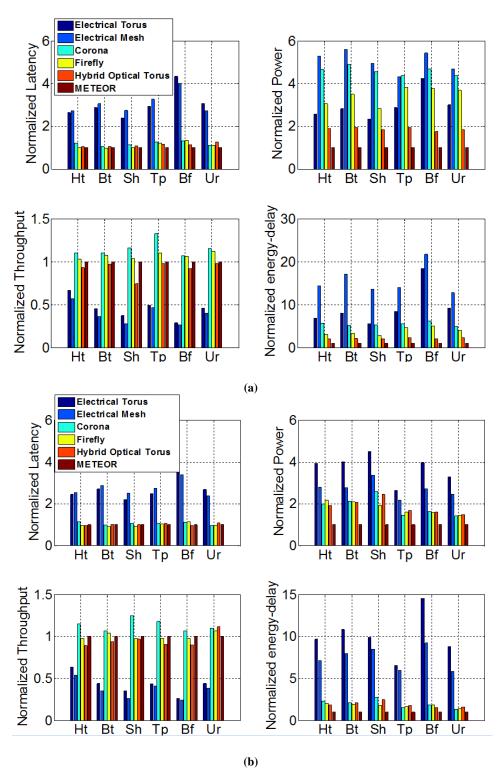

| Figure 26 Normalized latency, throughput, power, and energy-delay product comparison for synthetic benchmarks with (a) 128-bit waveguides and (b) 256-bit waveguides       |

| Figure 27 Normalized latency, throughput, power, and energy-delay product comparison for <i>SPLASH-2</i> benchmarks with (a) 128-bit waveguides and (b) 256-bit waveguides |

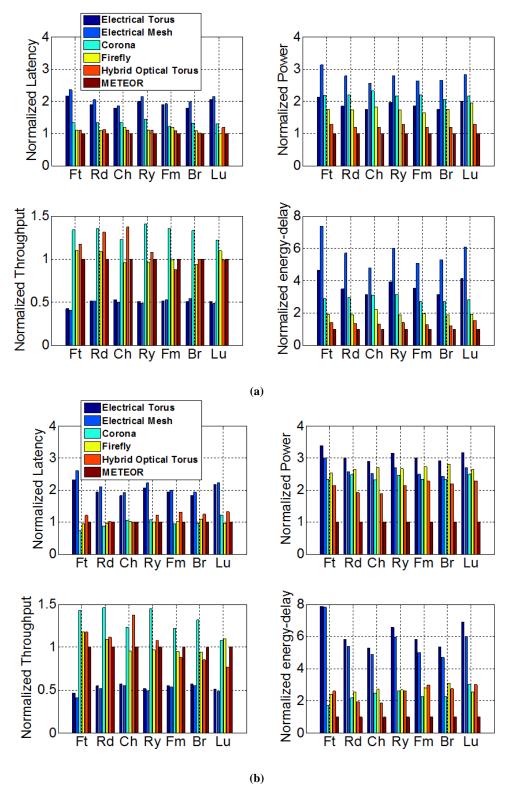

| Figure 28 Normalized latency, throughput, power, and energy-delay product comparison for <i>NAS</i> benchmarks (a) 128-bit waveguides and (b) 256-bit waveguides           |

| Figure 29 Normalized latency, throughput, power, and energy-delay product comparison for <i>PARSEC</i> benchmarks (a) 128-bit waveguides and (b) 256-bit waveguides        |

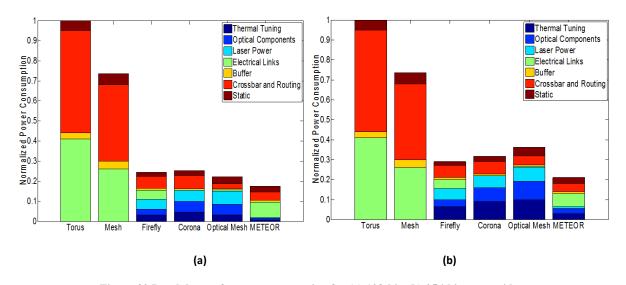

| Figure 30 Breakdown of power consumption for (a) 128-bit, (b) 256-bit waveguides 66                                                                                        |

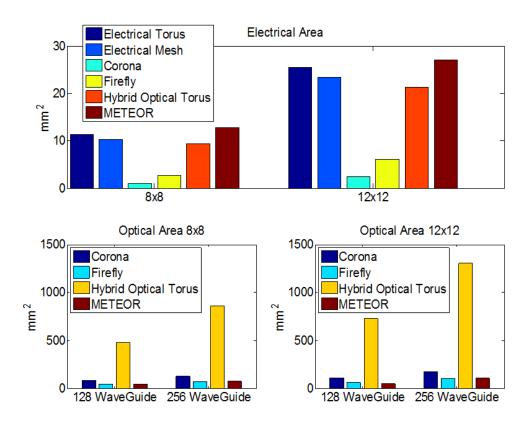

| Figure 31 Photonic layer and electrical layer area overhead comparison for various NoC architectures                                                                       |

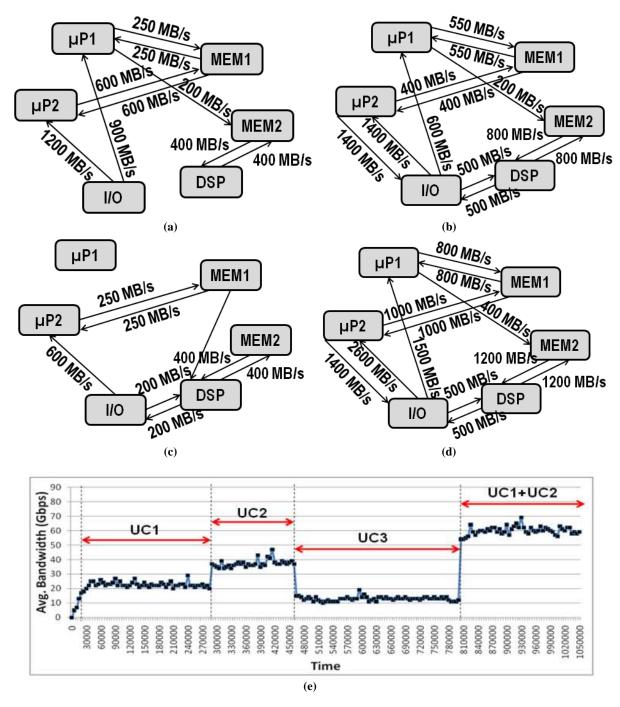

| Figure 32 Multiple use case application with use cases (a) UC1, (b) UC2, (c) UC3, (d) UC1+UC2, (e) workloads                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 33 Building blocks of on-chip photonic interconnects                                                                                                                                                                                                                                                 |

| Figure 34 Microring resonator coupling for multi ring waveguides                                                                                                                                                                                                                                            |

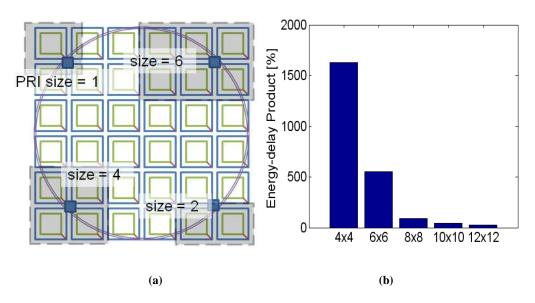

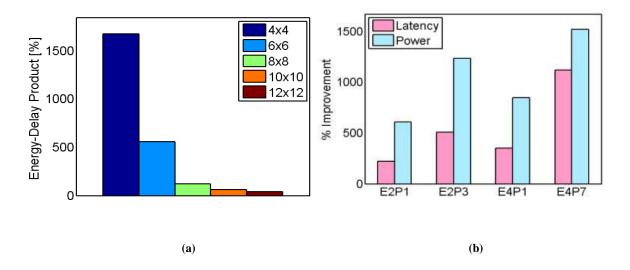

| Figure 35 (a) 6x6 hybrid NoC with photonic ring and various sizes of photonic regions of influence (PRI), (b) % improvement in energy-delay product for hybrid NoC with photonic ring compared to conventional 2D mesh NoC, with scaling CMP complexity                                                     |

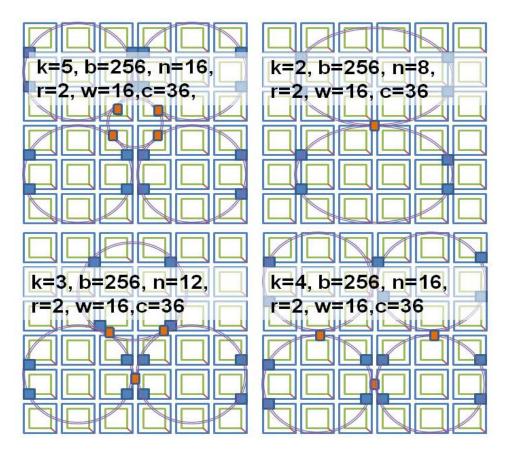

| Figure 36 Four configurations of the proposed hybrid photonic NoC architecture for a 6x6 CMP                                                                                                                                                                                                                |

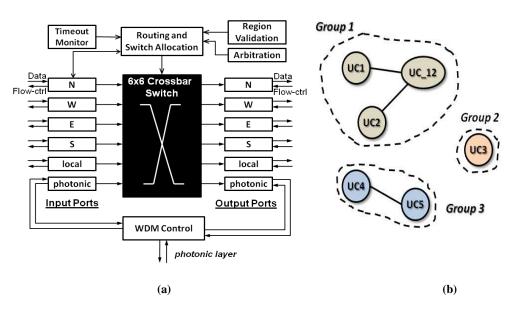

| Figure 37 (a) Gateway interface electrical router architecture, (b) use-case critical transition graph (CTG)                                                                                                                                                                                                |

| Figure 38 % Improvement for non-reconfigurable <i>UC-PHOTON</i> vs. 2D electrical mesh NoC, (a) power, (b) energy-delay product                                                                                                                                                                             |

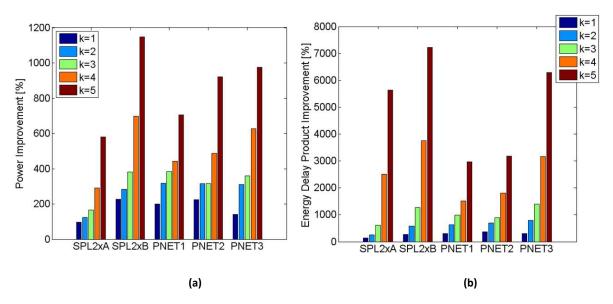

| Figure 39 % Improvement for runtime reconfigurable <i>UC-PHOTON</i> vs. approaches from [120] and [119], (a) avg. power w.r.t. [120], (b) avg. power w.r.t. [119], (c) performance w.r.t. [120], (d) performance w.r.t. [119], (e) energy-delay product w.r.t. [120], (f) energy-delay product w.r.t. [119] |

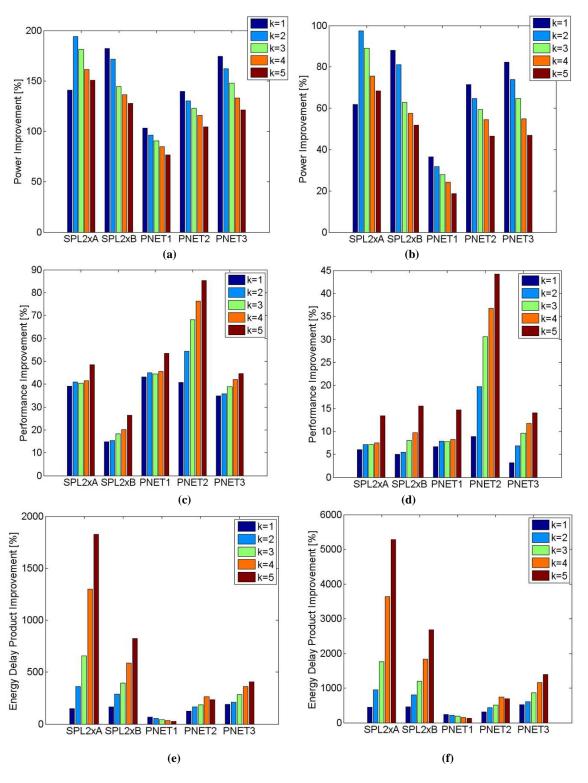

| Figure 40 Percentage improvement in (a) energy-delay product for hybrid photonic ring NoC vs. 2D electrical mesh NoC, with scaling core count, (b) average latency and power for E2P1, E2P3, E4P1, E4P7 vs. E1P1                                                                                            |

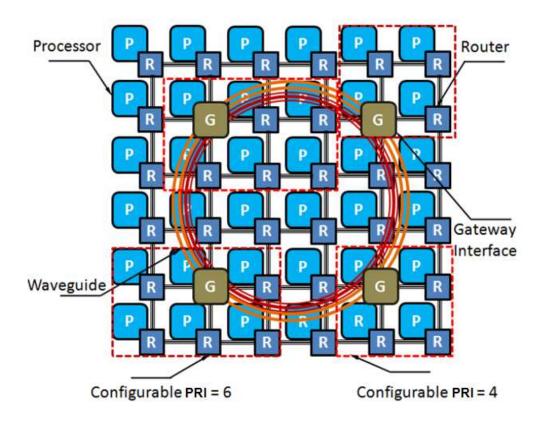

| Figure 41 E2P3 <i>OPAL</i> configuration                                                                                                                                                                                                                                                                    |

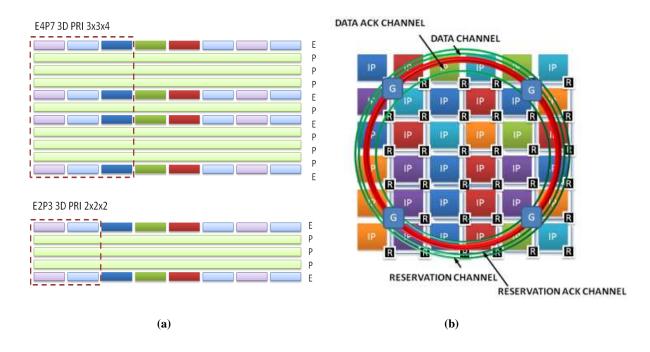

| Figure 42 (a) 3D photonic region of influence (3D-PRI) (b) photonic channels                                                                                                                                                                                                                                |

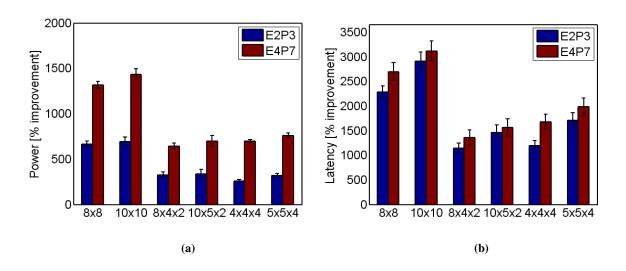

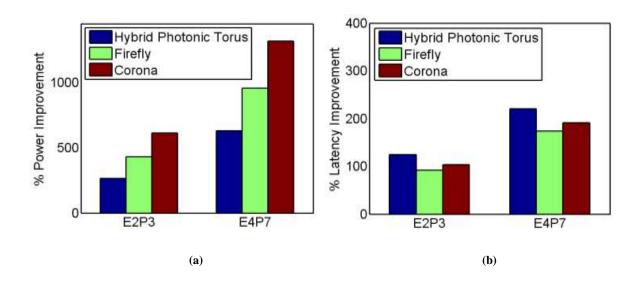

| Figure 43 Percentage improvement for <i>OPAL</i> configurations compared to 2D and 3D electrical mesh NoCs (a) power, (b) average packet latency                                                                                                                                                            |

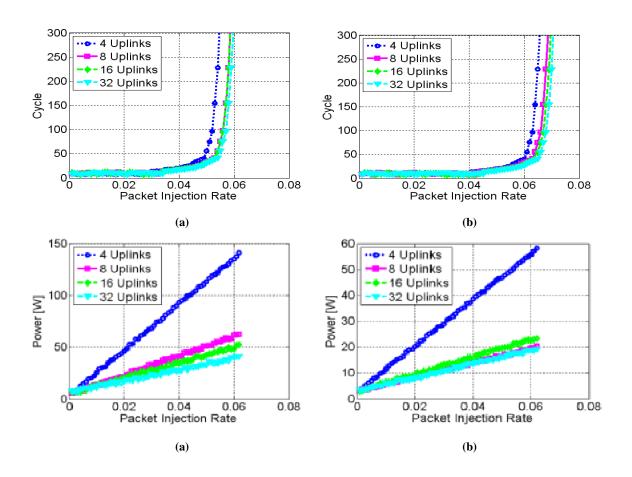

| Figure 44 Impact of changing number of uplinks on (a) latency of E2P3, (b) latency of E4P7, (c) average power of E2P3, (d) average power of E4P7                                                                                                                                                            |

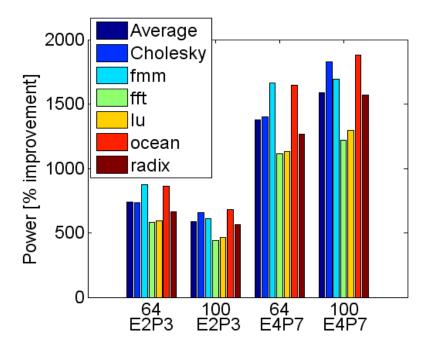

| Figure 45 Percentage improvement in average power dissipation for E2P3 and E4P7 <i>OPAL</i> configurations, with all runtime adaptations enabled (DVS/DFS, WDM, PRI) relative to baseline case with no runtime adaptation enabled                                                                           |

| Figure 46 Percentage improvement for E2P3 and E4P7 <i>OPAL</i> configurations compared with hybrid photonic torus [32], Corona [28] and Firefly [29] NoCs: (a) power dissipation (b) average packet latency                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 47 Hybrid ring-mesh photonic architecture [44]                                                                                                                                                                                                            |

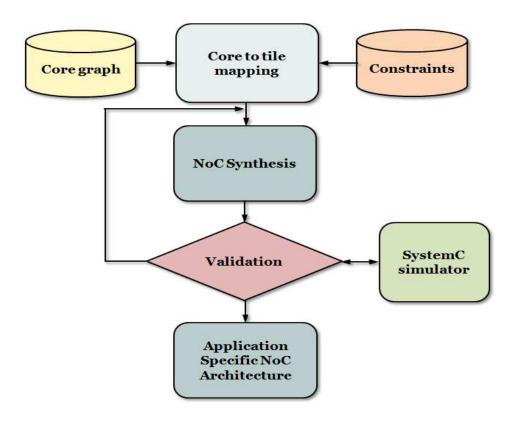

| Figure 48 NoC synthesis design flow of the synthesis process                                                                                                                                                                                                     |

| Figure 49 Core-to-tile mapping greedy heuristics                                                                                                                                                                                                                 |

| Figure 50 Particle swarm optimization formulation                                                                                                                                                                                                                |

| Figure 51 Ant colony optimization formulation                                                                                                                                                                                                                    |

| Figure 52 Simulated annealing algorithm formulation                                                                                                                                                                                                              |

| Figure 53 Genetic algorithm formulation                                                                                                                                                                                                                          |

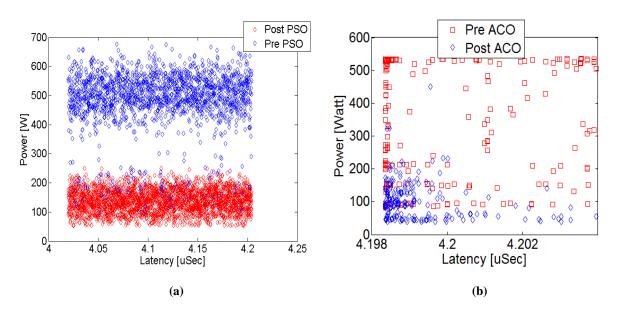

| Figure 54 Pre and post PSO and ACO power consumption and latency for solution space of lubenchmark                                                                                                                                                               |

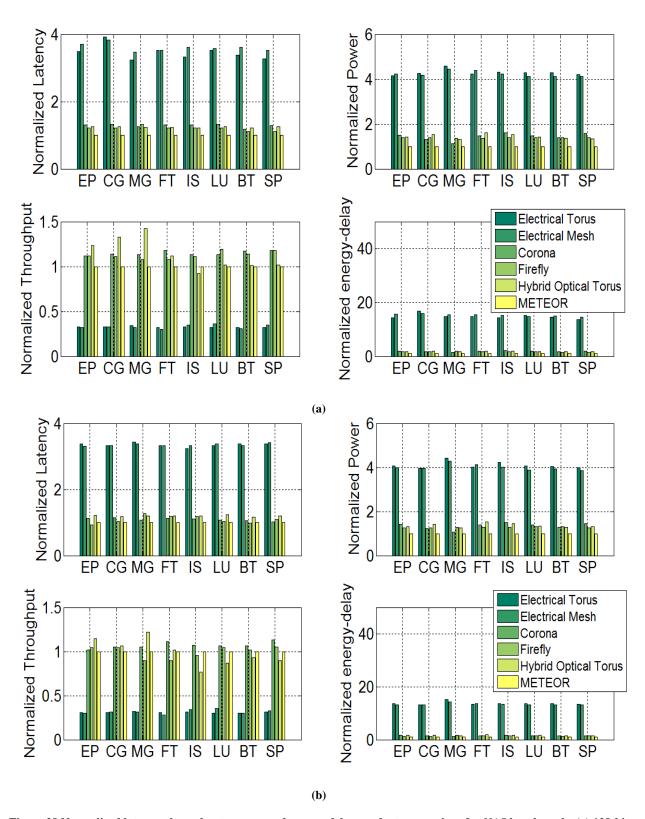

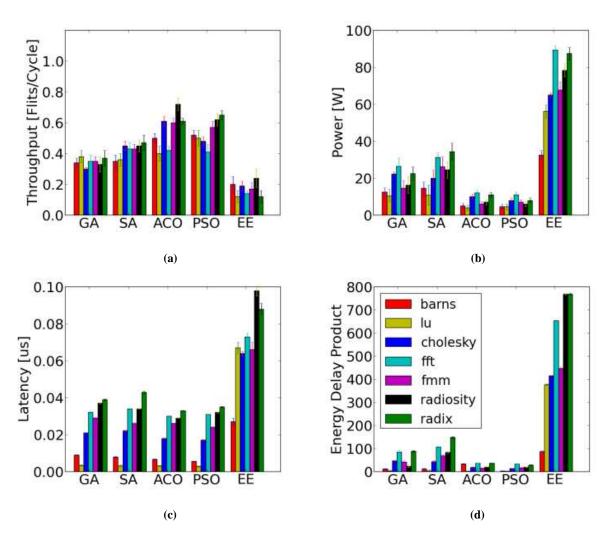

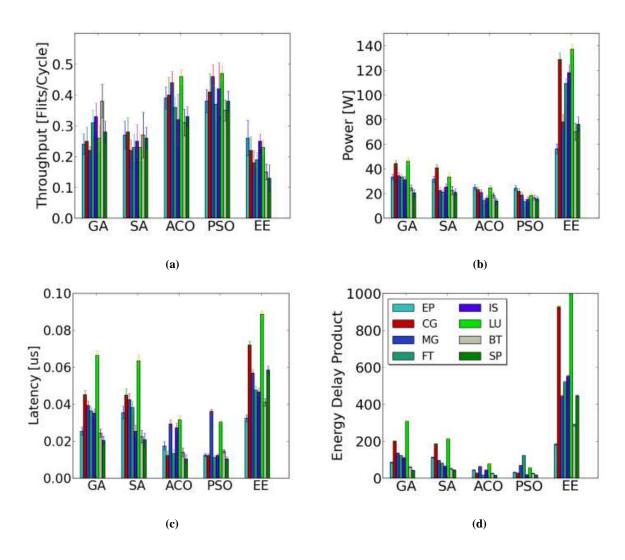

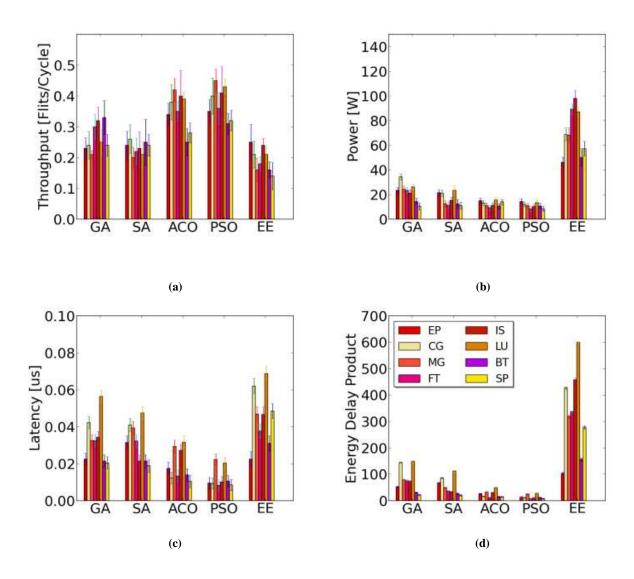

| Figure 55 Latency, throughput, power, and energy-delay product comparison for <i>SPLASH-2</i> benchmarks for 10x10 NoC                                                                                                                                           |

| Figure 56 Latency, throughput, power, and energy-delay product comparison for <i>SPLASH-2</i> benchmarks for 6x6 NoC                                                                                                                                             |

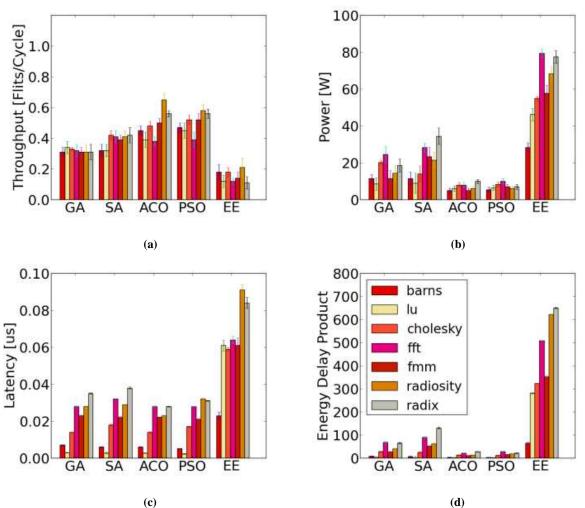

| Figure 57 Latency, throughput, power, and energy-delay product comparison for <i>PARSEC</i> benchmarks for 10x10 NoC                                                                                                                                             |

| Figure 58 Latency, throughput, power, and energy-delay product comparison for <i>PARSEC</i> [40] benchmarks for 6x6 NoC                                                                                                                                          |

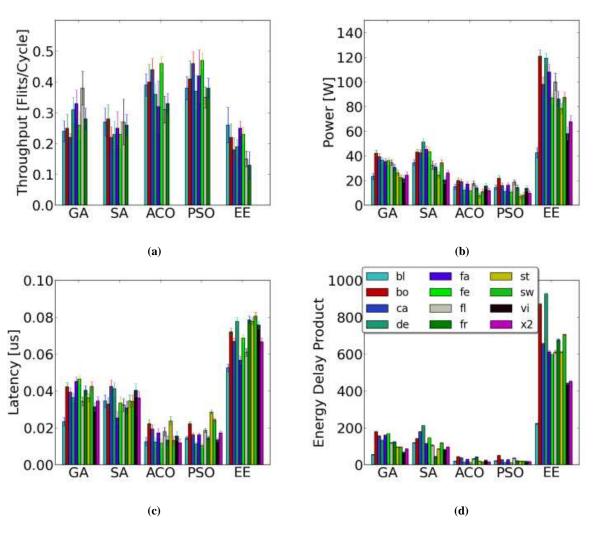

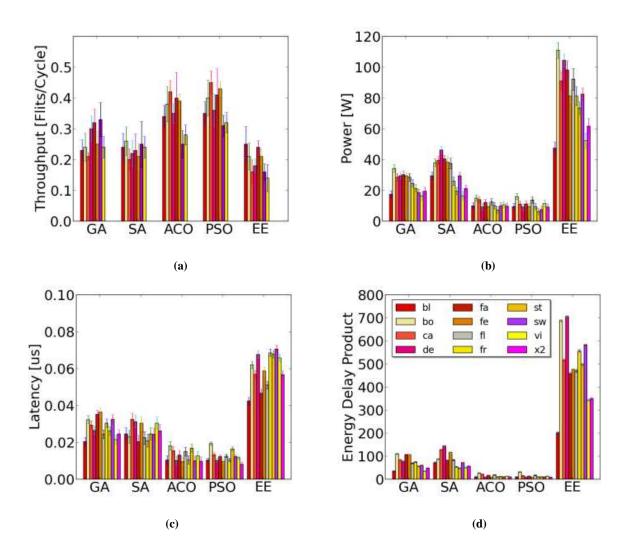

| Figure 59 Normalized latency, throughput, power, and energy-delay product comparison <i>NAS</i> [39] benchmarks for 10x10 NoC                                                                                                                                    |

| Figure 60 Latency, throughput, power, and energy-delay product comparison <i>NAS</i> [39] benchmarks for 6x6 NoC                                                                                                                                                 |

| Figure 61 Energy delay product improvements for solutions generated by ACO and PSO over SA and GA for (a) 6x6 <i>SPLASH-2</i> (b) 10x10 <i>SPLASH-2</i> , (c) 6x6 <i>NAS</i> , (d) 10x10 <i>NAS</i> , (e) 6x6 <i>PARSEC</i> , (f) 10x10 <i>PARSEC</i> benchmarks |

| Figure 62 Gateway interface router architecture                                                                                                                                                                                                                  |

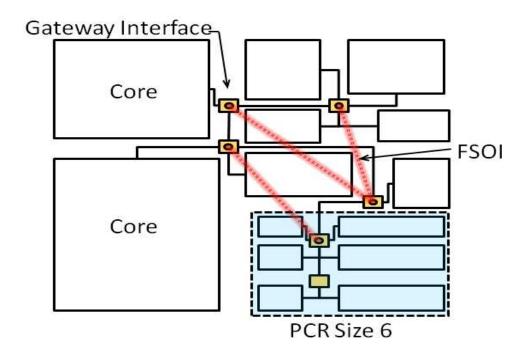

| Figure 63 Photonic concentration region (PCR)                                                                                                                                                                                                        | 156 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 64 HELIX hybrid electro-photonic NoC synthesis flow                                                                                                                                                                                           | 160 |

| Figure 65 (a) Output of floorplanner (b) Minimum Euclidean Distance Steiner Tree (MEST) electrical network (c) Minimum Rectilinear Distance Steiner Tree (MRST) for FSOI links (d) clustering and dual level router mapping.                         | )   |

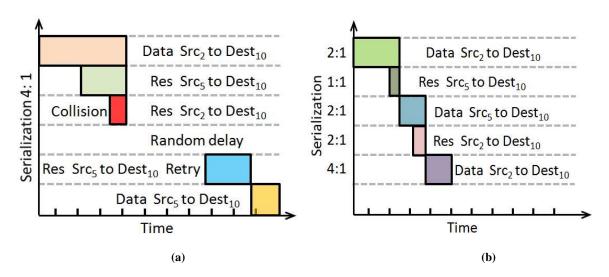

| Figure 66 Scenarios for reservation channel collision (a) reservation process with FSOI collis (b) reservation process after adjusting serialization degree                                                                                          |     |

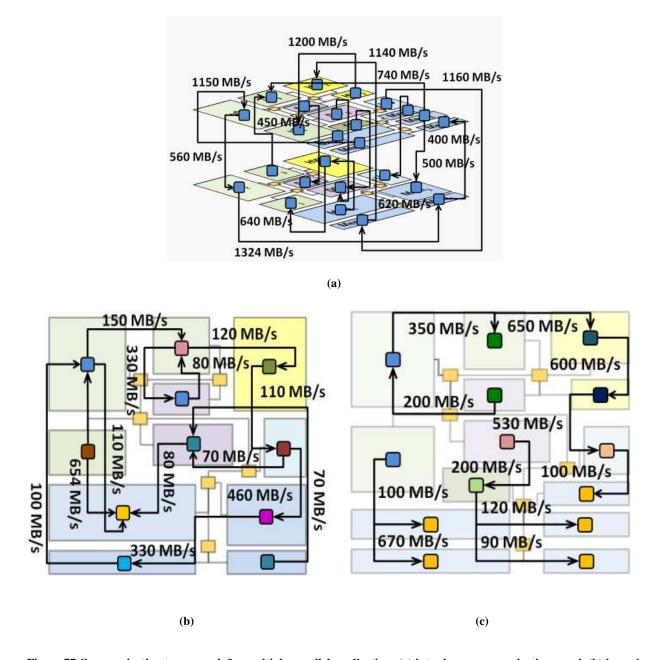

| Figure 67 (a) Communication trace graph for multiple parallel applications, nanophotonic link in red color (b) custom layout with irregular topology                                                                                                 |     |

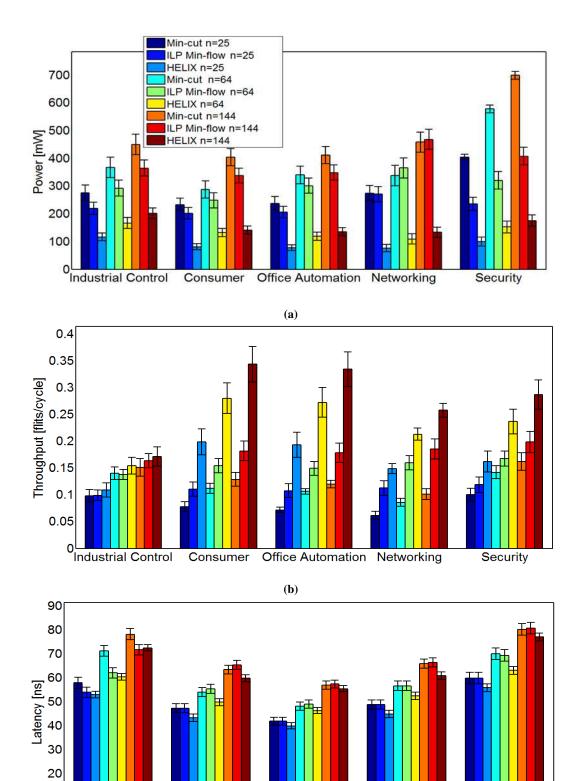

| Figure 68 Synthesis result comparison (a) power (b) throughput (c) latency                                                                                                                                                                           | 171 |

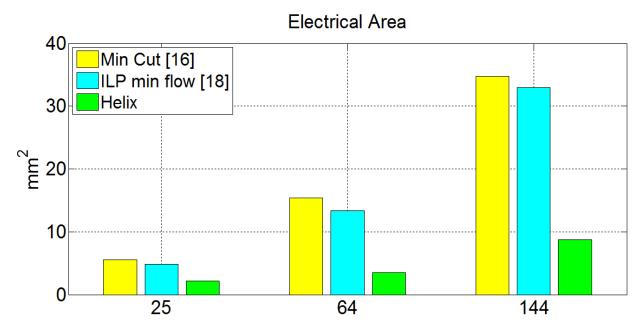

| Figure 69 Area overhead comparison for <i>HELIX</i> synthesized electrical network for <i>PARSEC</i> application benchmarks                                                                                                                          | 176 |

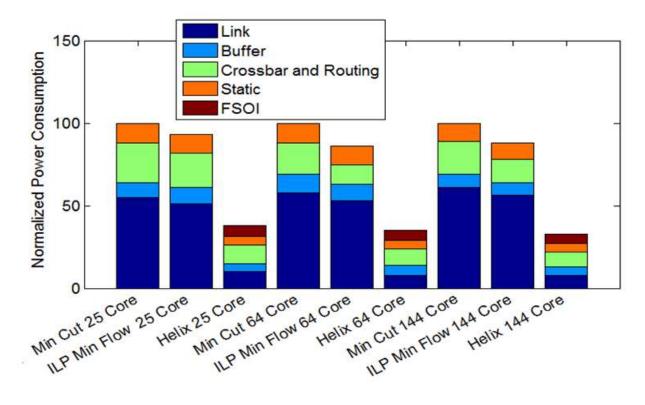

| Figure 70 Normalized breakdown of power consumption                                                                                                                                                                                                  | 176 |

| Figure 71 Synthesis result comparison for <i>PARSEC</i> multi-threaded workloads (a) average pov (b) throughput (c) average latency                                                                                                                  |     |

| Figure 72 Building blocks of free-space on-chip photonic interconnects: (a) modulator and receiver circuit (b) 3D integration of electrical and FSNPI layer interconnect including photon concentration region (PCR)                                 |     |

| Figure 73 3D Gateway interface FSNPI router architecture                                                                                                                                                                                             | 184 |

| Figure 74 3D-HELIX hybrid nanophotonic-electric NoC synthesis flow                                                                                                                                                                                   | 186 |

| Figure 75 (a) Layer one, Steiner tree (MEST) for electrical network and minimum rectilinear distance Steiner tree (MRST) for FSNPI links (b) layer two, MEST and MRST (c) clustering dual level router mapping (d) TSV assignment and PCR generation | for |

| Figure 76 Scenarios for reservation channel collision (a) reservation process with FSNPI collision (b) reservation process after adjusting serialization degree                                                                                      | 193 |

| Figure 77 Communication trace graph for multiple parallel applications (a) inter layer communication graph (b) layer 1 communication graph (c) layer 2 communication graph                                                                           | 199 |

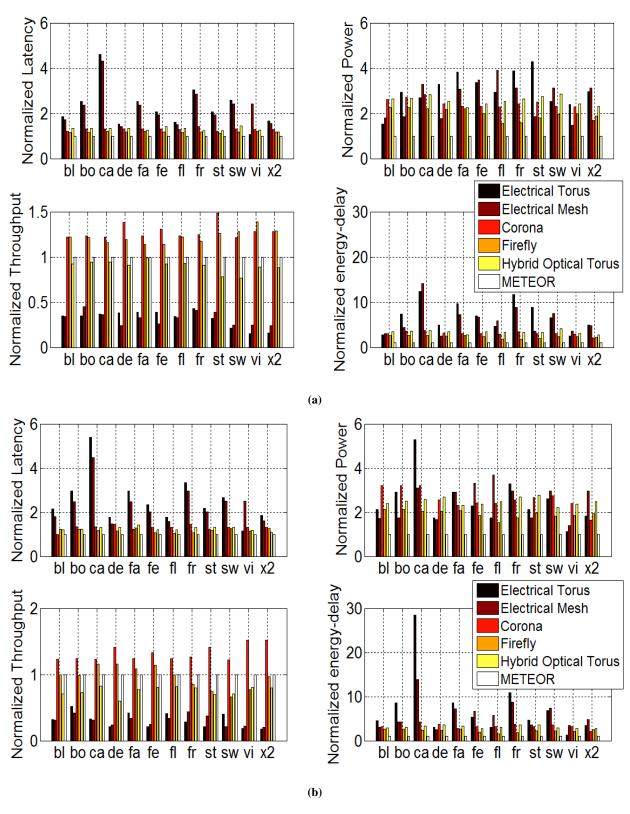

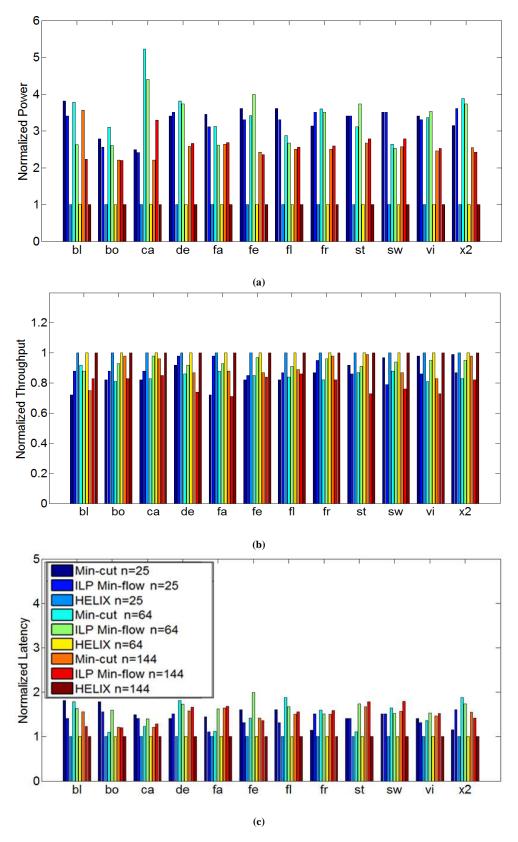

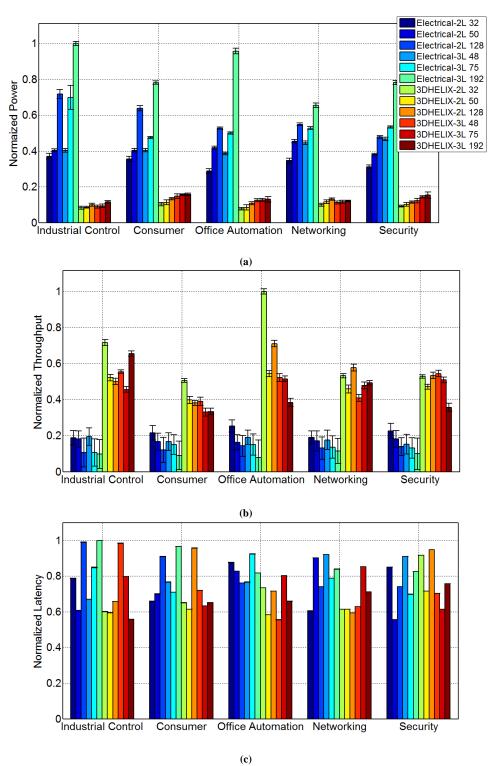

| Figure 78 MiBench [173] synthesis results (a) power (b) throughput (c) latency                                                                                                                                                                       | 200 |

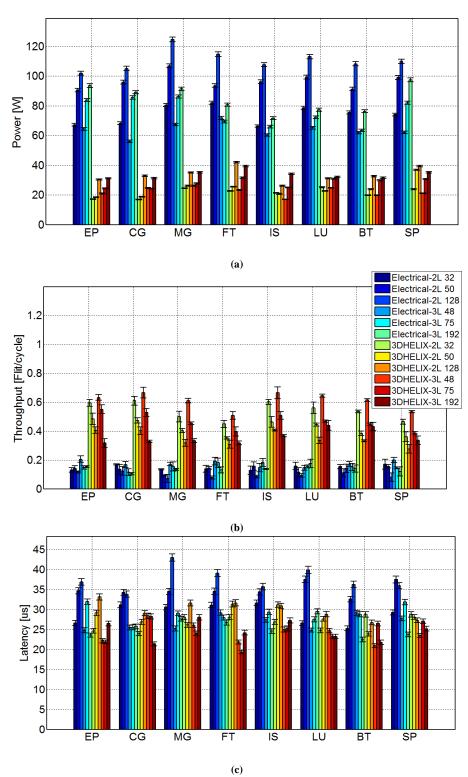

| Figure 79 NAS [136] synthesis results (a) power (b) throughput (c) tatency                                       | 201 |

|------------------------------------------------------------------------------------------------------------------|-----|

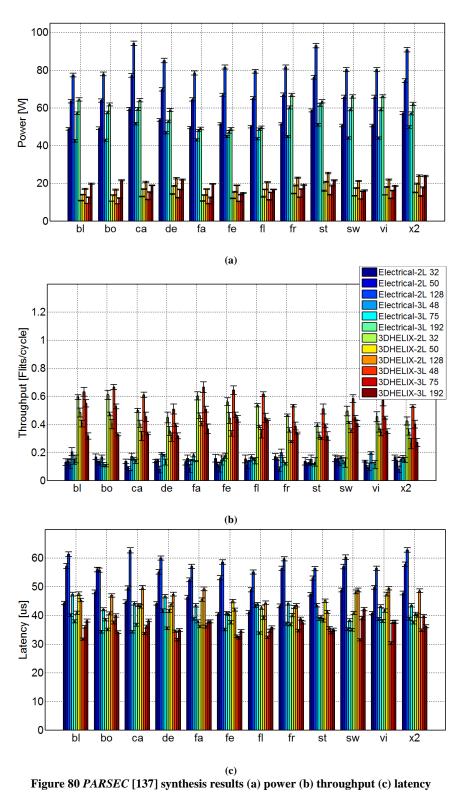

| Figure 80 PARSEC [137] synthesis results (a) power (b) throughput (c) latency                                    | 202 |

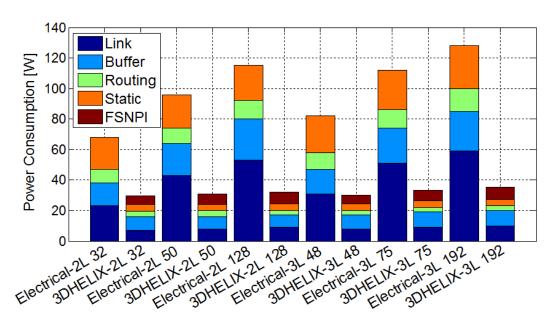

| Figure 81 Normalized breakdown of power consumption for 32, 50, 128 core 2-layer 192 core 3-layer configurations | , , |

| Figure 82 NoC research summary and direction                                                                     | 210 |

## LIST OF KEYWORDS

ACK : Acknowledge

ACO : Ant colony optimization

CFD : Computational fluid dynamics

CMOS : Complementary metal oxide semiconductor

CMP : Chip multiprocessors

CNT : Carbon nanotubes

CTG : Critical transition graph as an undirected graph CTG

DFS : Clock frequency scaling

DVS : Dynamic supply voltage

E/O : Electrical to optical

FDMA : Frequency division multiple access

FSNPI : Free space nanophotonic interface

FSOI : Free-space on-chip photonic interconnects

GA : Genetic algorithm

ITRS : International technology roadmap for semiconductors

MPSoC : Multi-processor systems-on-chip

MQW : Multiple quantum well

MWMR : Multiple write multiple read

NACK : Not acknowledge

NAS : NASA advanced supercomputing

NI : Network interfaces

NoC : Design of the network-on-chip

O/E : Optical to electrical

PARSEC: Princeton application repository for shared-memory computers

PCR : Photonic concentration region

PRI : Photonic region of influence

PSO : Particle swarm optimization

QCSE : Quantum-confined stark effect

QoS : Quality of service

QW : Quantum well

RF-I : Radio frequency interconnects

SA : Simulated annealing

SOC : System-on-chip

SOI : Silicon on insulator

SWMR : Single write multiple read

TDMA : Time division multiple access

TIA : Trans-impedance amplifier

TO : Thermo-optic

TSV : Through silicon via

UDSM : Ultra-deep submicron effects

UWB : Ultra wide band

VCSEL : Vertical cavity surface emitting lasers

#### 1 INTRODUCTION

This chapter outlines design challenges for modern chip multiprocessor (CMP) based on ever increasing application performance and power requirements. Network-On-Chip (NoC) communication fabrics in CMPs have led to a paradigm shift from classical bus based architectures to on-chip communication networks; however these network architectures still need to overcome a number of major challenges, which are also discussed in the chapter.

#### 1.1 MOTIVATION

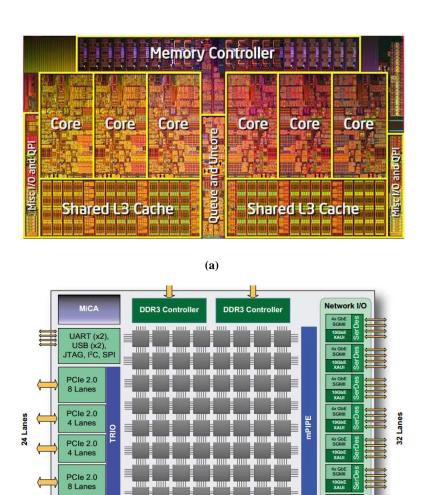

Multicore processors are currently hailed as a universal means to mitigate the power consumption challenge caused by ever increasing frequency scaling to maintain the performance growth required by modern applications. However the real challenge goes far beyond just frequency scaling and encompasses many other complex factors such as technology node scaling and leakage current that consumes power without doing anything useful. Figure 1(a) shows a recent *Intel 17 950 3.06GHz* six core processor. Processors with four to sixteen cores have today become a standard in prevailing computing systems. The trend towards larger multi-core processors is expected to continue, however there are many challenges with scaling the number of cores, such as communication bandwidth, communication power, and communication latency that are becoming limiting factors. Figure 1(b) presents the *Tilera Gx72* processor chip with on electrical mesh NoC that currently consumes around 30~40% pf the total chip power for interprocessor communication [1]. As a result of such high communication overhead, the current fairly explosive growth in the number of cores per processor will have to slow down unless some novel solution addresses many of these challenges in the on-chip communication fabric.

TILE-Gx8072 Processor Block Diagram

**(b)**

Figure 1 Modern processors (a) Intel 6 Core I7 950 3.06GHz, 2012 (b) Tilera Tile-Gx72 system-on-chip, 2013

It is projected that by 2017, as many as 256 cores would be integrated onto a single die. With the advent of such highly parallel chip multiprocessors (CMPs), the design of the interconnection fabric will be crucial to ensure that compute cores are able to communicate with cache banks, memory modules, and other I/O devices with high bandwidths, low latencies and minimal power dissipation. However, electrical communication fabrics today are already

severely constrained due to their long multi-hop latencies and high power dissipation, which will make it practically impossible to stay within the limited on-chip power budget while meeting performance constraints in the near future.

## 1.2 TECHNOLOGY TRENDS

Continuous CMOS technology scaling over the past several decades has led to transistors becoming faster, smaller in size, and consuming less power. This trend is expected to persist for upcoming years. Moore's law projects ~2× performance gains through process node technology advancements every 18 to 24 months. The computing world has seen dramatic increases in processor clock frequency from 5 MHz to 4 GHz from 1984 onwards, which has so far supported such performance gains. But the increase in frequency is also resulting in increasing power densities to the extent that on chip thermal management has become major a limitation to increasing clock frequency going forward as a means to improve performance.

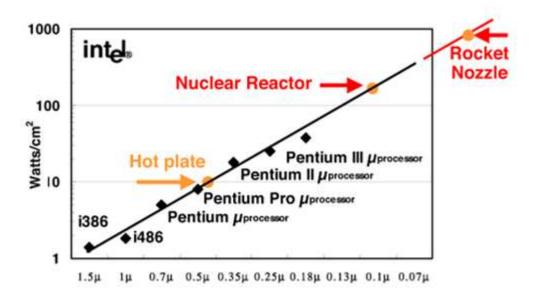

Figure 2 presents data from Intel<sup>®</sup> [2] that demonstrates how power density is becoming a critical design issue [1] that needs to be addressed for modern computing systems going forward. This is prompting new way of thinking about how to maintain performance gains without increasing power density. Today, performance gains are being realized through multicore architectures by doubling the number of cores about every two years. CMPs with multiple cores provide performance gains by exploiting thread level parallelism to complement the traditional instruction level parallelism in uni-core processor systems.

Figure 2 Node size Vs power density data from Intel® [2]

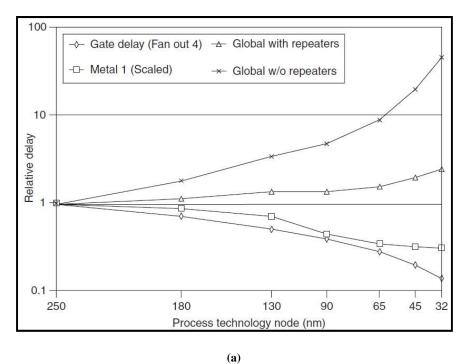

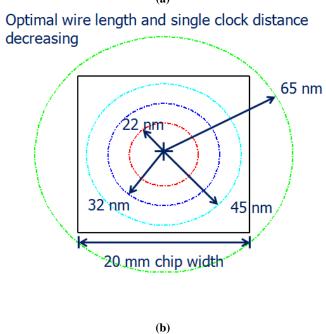

With smaller CMOS technology, gate delay has been decreasing, however the single clock distance travelled for on-chip communication is decreasing. Thus it is taking more clock ticks to communicate from one end of the chip to the other. Also wire delay is characterized by *RC* (Resistance, Capacitance) and this delay has been effectively increasing with technology scaling. As a result gate to wire delay ratio shows an ever increasing gap as shown in Figure 3. Thus it is becoming evident that focus on communication architecture design, customization, and is essential if performance gains are to continue in future generations on CMPs [3].

Figure 3 (a) Gate logic delay is decreasing, wire delay is increasing, and gate to wire performance gap is increasing with technology scaling [4] (b) optimal wire length and distance travelled in a single clock cycle is decreasing [2]

Figure 4 Networks-On-Chip (NoC), C: processor core, M: memory banks D: digital signal processors F: floating point processors P: global power management module

## 1.3 NETWORKS-ON-CHIP (NOC)

Many current processing systems that include multiple cores encompass a hierarchical or crossbar-type bus-based communication fabric. However bus-based communication architectures do not scale well with the increasing number of on chip cores in terms of bandwidth, clocking frequency and power [5]. Recent years have seen the emergence of a new form of on-chip communication fabric called Network-on-Chip (NoC). A NoC fabric (Figure 4) offers a structured network topology and architecture for on chip communication that reduces the complexity of designing communication fabrics for multi-core systems, providing more scalable latency, power and reliability than bus-based fabrics. NoCs are now therefore being considered as viable options for homogeneous CMPs as well as application-specific heterogeneous multi-processor systems-on-chip (MPSoCs). NoCs have been shown to offer significant benefits in bandwidth, scalability, and reliability compared to traditional hierarchical and crossbar-based shared bus communication architectures in UDSM technologies [6].

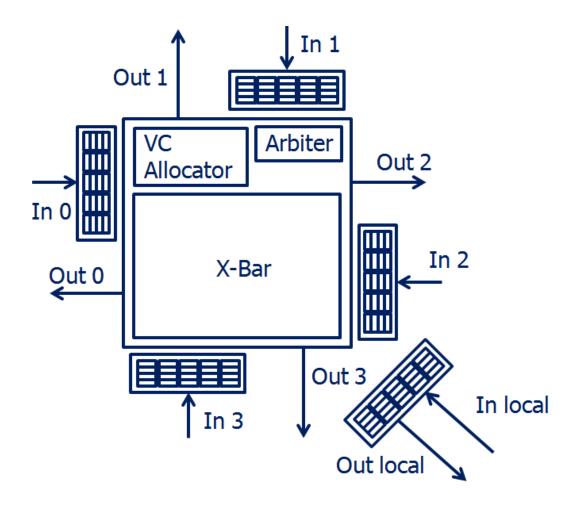

Figure 5 Electrical NoC router

Figure 5 presents an electrical NoC router that includes support for virtual channels (VCs) and wormhole network flow control. This router is designed for two-dimensional regular topologies such as mesh and torus. The NoC router includes 5-input and 5-output ports, where four of the ports are connected to neighboring routers on north, south, east and west directions, and one port is used to connect to a router's local processing core. Every input port supports five buffered FIFO virtual channels that are connected to a crossbar. Routing algorithms such as X-Y routing are enforced by an arbitration unit. The arbitration unit also ensures that there are no

conflicts between each virtual channel and that the arbitration is according to the defined policy.

Deadlock control and error handling units can utilize the fifth virtual channel as needed.

In practice, NoC communication fabrics still need to overcome two major challenges that are extremely relevant for emerging CMP applications [7]. Firstly, packet switched NoCs must support low latency transfers between cores (especially for real-time applications) but are often unable to meet QoS (Quality of Service) guarantees. Using virtual circuit switching instead of packet switching allows for better QoS management, but unpredictable circuit setup delays still exist. Secondly, NoCs must enable low power data transfers. However, the large number of network interfaces, routers, links, and buffers that are part of the NoC fabric lead to a communication infrastructure that consumes a significant portion of the power from the overall CMP power budget. For instance, several prototypes have shown NoCs taking a substantial portion of the system power, e.g., ~30% in the Intel 80-core teraflop chip [1] and ~40% in the MIT RAW chip [8]. Recent studies have suggested that NoC power dissipation is much higher (by a factor of 10×) than what is needed to meet peta- and exa-flop performance levels of future CMPs [7]. This power consumption becomes even worse when the NoC components are designed for adaptive operation with varying runtime application requirements. Power consumption also has a major influence on maximum temperature that determines CMP packaging and cooling costs. Studies [7] indicate that NoC power consumption will continue to ascend as the number of on-chip cores continue to increase. Thus, radical new approaches are required to overcome the power and performance brick walls facing NoCs in the near future [4].

#### 1.4 HYBRID NANOPHOTONIC NOC BASED ON WAVEGUIDES

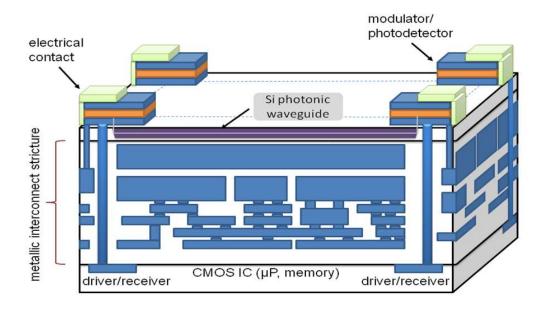

On-chip photonic communication provides a promising alternative to overcome the abovementioned drawbacks with electrical wires and electrical NoC fabrics. Nanophotonic waveguides have demonstrated bandwidths in the terabits per second range, along with lower access latency and susceptibility to electromagnetic interference [9]. Photonic signaling also has lower power consumption than electrical interconnects for long distance communication, as the power consumption of optically transmitted signals at the chip level is independent of the distance covered by the light [10]. Photonic NoCs were virtually inconceivable with previous generations of photonic technologies. But advances in the field of nanoscale silicon (Si) photonics have enabled the possibility of creating highly integrated photonic CMOS NoC platforms that can send and receive optical signals with superior power efficiencies [11] [12] [13] [14] [15]. In fact, photonic elements have become available as library cells in standard CMOS processes [16]. High-volume capable CMOS photonic transceiver process technology is today being offered by Luxtera [17] [18], in collaboration with ST-Microelectronics [19]. Device simulation libraries [20] now offer simulation of nanophotonic components that can project performance of optoelectronic modulators and waveguide-based silicon photodiodes. Thus, it has now become practical to consider an interconnection network for CMPs built with photonic elements. Such photonic NoCs will likely utilize 3D integration [21] as shown conceptually in Figure 6 with vertical through silicon via (TSV) providing interconnections between the silicon and photonic layers.

Figure 6 3D IC implementation of a hybrid photonic NoC with cores (bottom layer) and photonic waveguide (top layer) [22]

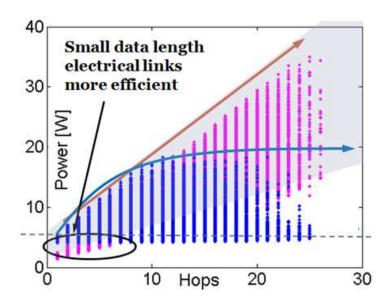

Recent works have also presented some interesting surveys motivating the need for new technologies on silicon chips. CMP performance scaling up to 20 Giga-flops/Watt will be one of the major challenges going forward [23]. Based on this survey, (i) approximately 40% of total power will be used by transistors, (ii) 40-50% by the external storage and cooling system thus leaving only (iii) 10-20% of the system power for interconnects at all levels. Si photonics is projected to be the leading technology to meet these aggressive requirements. Si photonic technology offers significant and unique advantages in terms of power consumption, access latencies, and high bandwidth for transfers over long distances (>~1mm) on a chip as shown in Figure 7. To realize true benefits of photonic communication, there is a need for intricate balancing of many trade-offs. Figure 7 presents the number of hops that represents distance travelled by a data packet (x-axis) and power consumed (y-axis). Each pink dot represents power consumed by electrical transmission as a function of data packet size, similarly each blue dot represents power consumed by photonic transmission. At smaller distances and small data sizes

electrical communication consumes lower power, but for longer distances photonic communication consumes lower power. Global long distance communication through nanophotonic waveguides however requires two essential enablers: (i) buffering and (ii) header processing. Both of these are relatively difficult to implement in the photonic realm. Thus a hybrid communication infrastructure with both photonic and electrical signaling becomes necessary.

Figure 7 Global/long distance communication, nano-photonic power stays constant/low while electrical communication power increases as a function of distance travelled

## 1.5 ON-CHIP WAVEGUIDE PHOTONIC COMMUNICATION BUILDING BLOCKS

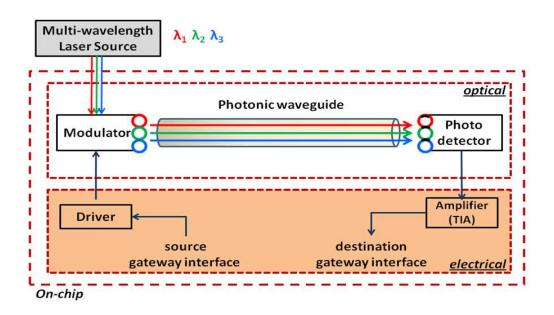

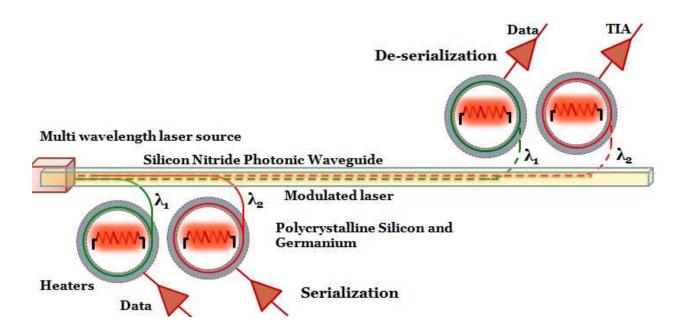

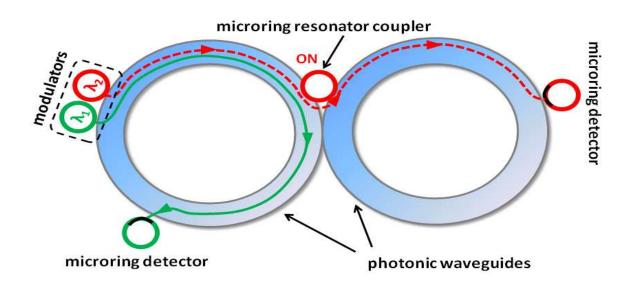

Figure 8 shows a high level overview of the primary on-chip waveguide photonic transmission components: a multi-wavelength laser light source, resonant modulators/filters, photonic waveguide, and photodetector receivers. Multiple wavelengths of light from a mode-locked, multi-wavelength laser [24] enable wavelength division multiplexing (WDM) that allows several data streams to coexist in the same waveguide, improving transfer bandwidth.

Conventional WDM approaches deploy separate single-frequency lasers with close loop feedback control to stabilize each wavelength that ensures correspondence with the pre-assigned WDM channels [25]. This requires high silicon area and complexity which is critical for an onchip nanophotonic WDM implementation. An alternative is to use a broadband laser source that supports multiple WDM channels simultaneously where WDM channels are carved out of the broadband spectrum by a passive filter instead of single frequency sources [25]. The main advantage of such an implementation is that the wavelength drift of the source does not influence the system as diffraction grating coupling enables spectrum spread for various wavelengths. Microring resonant modulators [26] convert electrical data signals into light that is propagated through a CMOS-compatible photonic waveguide. The light in the waveguide is eventually coupled into microring filters at the destination that drop the light on photodetectors [27], and thereafter the light signal is converted back into an electrical data signal. Trans-impedance amplifier (TIA) circuits finally amplify analog electrical signals from the photodetector to digital voltage levels. It is also vital for all microring resonators to be thermally tuned (using thermal heater elements) to maintain their resonance under on-die temperature variations.

The topology of the on-chip photonic waveguide has important implications. Photonic waveguides with highly angled structures (such as those commonly found in electrical topologies) may result in significant signal degradation due to bending losses. This degradation is compounded when laying out multiple waveguides for multi-bit parallel transfers on communication links. Consequently, it is preferable to employ simpler topologies, such as a ring topology, that is better suited to the physical characteristics of photonic waveguides. The waveguide is built using a high refractive index silicon on insulator (SOI) material, which has lower pitch and area footprint than low refractive index polymer waveguides such as those used

in [3]. SOI waveguides also have other advantages such as compact modulators that do not require high voltage drive for high frequency operation, the ability to carry light with low losses (on the order of 2–3 dB/cm), and the malleability to be curved with bend radii of  $\sim 10\mu m$  [15].

Figure 8 On-chip waveguide photonic transmission components

## 1.6 ON CHIP FREE SPACE COMMUNICATION BUILDING BLOCKS

Waveguide based nanophotonic communication fabrics that use silicon microring resonators face a few challenges for practical implementation even with recent promising developments. The key challenges for waveguide photonics include: (i) high complexity and overhead of thermally tuning microring resonators to ensure proper coupling of wavelengths, (ii) high power footprint due to significant waveguide crossing, propagation, and bending losses, (iii) need for complex tapered structures and optimized grating couplers with high coupling efficiency, and (iv) 0.5-3  $\mu m$  inter-waveguide spacing requirements to avoid crosstalk that can lead to lower bandwidth density than in optimized electrical wires [28] [29].

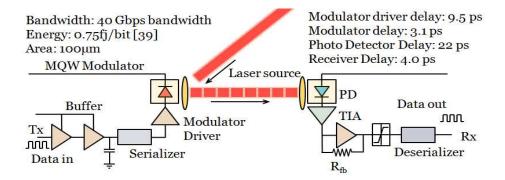

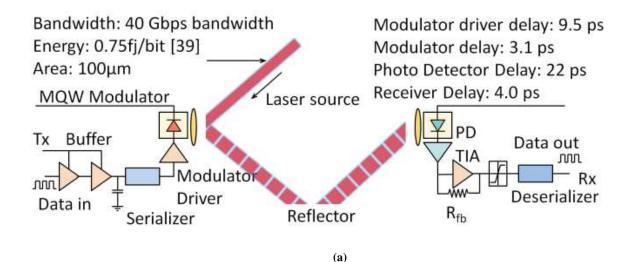

Figure 9 Building blocks of free-space on-chip photonic interconnects

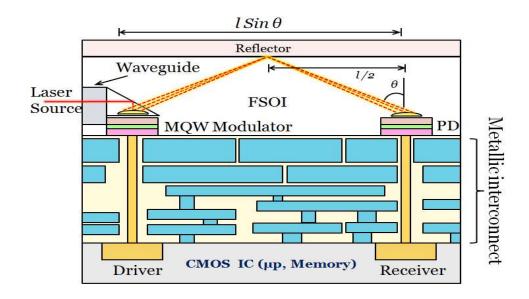

To overcome these challenges with waveguide nanophotonics, free-space nanophotonics based on GaAs/AlAs dense Multiple Quantum Well (MQW) devices [30] have recently been proposed as an alternative. In these architectures, light does not travel in a waveguide, instead it is transmitted and reflects off a reflector array (e.g. made of micro-mirrors) to arrive at its destination. Such free-space communication can be integrated with standard CMOS fabrication processes and is better suited for high-density optical interconnects due to its small active area and improved misalignment tolerance. MQW devices are projected to consume less than 1 pJ/bit energy and can be configured either as absorption modulators or photo-detectors (PDs). On-chip photonic interconnects utilizing MQWs can operate at 40 Gbps bandwidth [31] to instantiate single-hop or multi-hop transfers through free-space optical links. MQW modulators provide significant potential to get around the thermal tuning challenges of silicon microring resonators and can be fabricated in various angles to achieve out-of-plane beam steering directions. Figure 9 summarizes the building blocks of on-chip free-space optical interconnects (FSOI) with MQW modulators and PDs. It is also possible to utilize serializer/ deserializer circuits to enable tradeoffs between communication power and bandwidth. Figure 10 illustrates a FSOI with logic and photonics planes and vertical through silicon via (TSV) links providing interconnections between

the silicon and photonics layers [30]. MQW devices are fabricated on a GaAs substrate and then flip-chip bonded to the logic layer and waveguide coupled with a continuous wave external laser source. The modulated light can be directed through micro-mirrors and micro-lens to transmit data via the free-space medium.

Figure 10 Conceptual view of CMOS integrated free-space on-chip optical link [28]

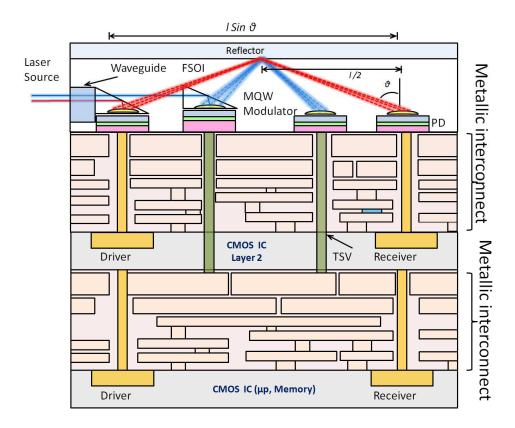

## 1.7 3D NOC INTERCONNECTS

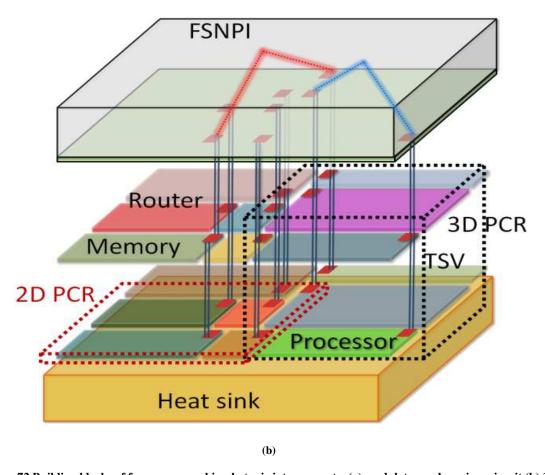

While photonic interconnects can reduce on-chip communication bottlenecks, other innovations are required to continually increase core counts on a die, to ensure sustained computation performance increases. Of the several different disruptive technologies that are being investigated for this purpose today, 3D integrated circuits (3D-ICs) with wafer-to-wafer bonding technology is one of the most promising candidates [32] [33] [34]. In wafer-to-wafer bonded 3D-ICs, active devices (processors, memories, peripherals) are placed on multiple active layers and vertical Through Silicon Vias (TSVs) are used to connect cores across the stacked layers. Multiple active layers in 3D ICs can enable increased integration of cores within the same

area footprint as traditional single layer 2D ICs. In addition, long global interconnects between cores can be replaced by shorter inter-layer TSVs, improving performance and reducing on-chip power dissipation. Recent 3D IC test chips from Intel [8], IBM [32], and Tezzaron [33] have confirmed the benefits of 3D IC technology.

Figure 11 Conceptual view of 3D CMOS IC with logic and FSNPI layers [35]

While 3D ICs are promising, the fundamental power, delay, and noise susceptibility limitations of traditional copper (Cu) interconnects will still limit their achievable improvements. To overcome these limitations, photonic interconnects [29] will be essential components in 3D-ICs to overcome latency and power bottlenecks of Cu interconnects. While several research efforts have individually explored the benefits of photonic interconnects and 3D IC technology,

using 3D ICs as a platform for the realization of hybrid electro-photonic NoCs has not received much attention to date.

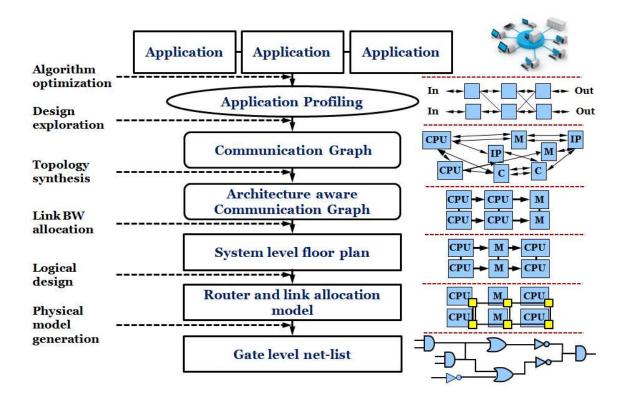

Figure 12 Modern CMP design flow

# 1.8 HYBRID NANOPHOTONIC-ELECTRIC NOC SYNTHESIS

Figure 12 presents a modern CMP design flow with emphasis given to on-chip communication optimization. The inclusion of photonics in this flow will require many changes. Significant recent research [36] [37] [38] [39] [40] [41] [42] [43] [44] has focused on developing hybrid photonic NoC architectures that optimize local and global communication distribution between electrical and photonic links. However, automated optimization of hybrid photonic NoCs for application-specific performance is an NP-hard problem and has yet to be addressed. Synthesis techniques used for application-specific electrical NoC fabrics [45] [46] [47] [48] [49]

[50] [51] [52] are not directly applicable to hybrid nanophotonic-electric fabrics that possess a more complex search space. Hybrid nanophotonic-electric fabrics require determining values for a diverse set of unique parameters such as wavelength division multiplexing (WDM) density, number of photonic uplinks, serialization degree, etc. in order to maximize communication performance-per-watt [53]. A photonic interconnect with n=256 waveguides and m=256wavelengths will require exploring  $n+(n)^2+(n)^3+...+(n)^m$  configurations to find the most power efficient solution that also meets performance goals. This is most certainly practically exorbitant [54]. Moreover, these two parameters are just a small subset of the much larger set of parameters that must be explored during hybrid NoC optimization. Finding the best solution for such a combinatorial optimization problem that is known to be NP-hard could take years if searching through the entire solution space, even with leading-edge supercomputing technology today. Thus, application-driven synthesis of hybrid nanophotonic-electric NoCs will become increasingly important as on-chip core counts increase, but this problem has not yet been addressed in prior work by researchers. There is a need to design polynomial-time heuristics that permit us to identify and search through a relevant portion of the solution space in a tractable amount of time to find a near optimal solution [53] [55]. Greedy heuristics are unlikely to find good quality solutions due to their inclination for getting stuck in local optima. In contrast, nongreedy search heuristics such as Simulated Annealing (SA) [56] operate through repeated transformations and have the hill-climbing ability to escape local optima by allowing acceptance of worse solutions within the evaluation process. A population of solutions being simultaneously manipulated is one of the major differences between the SA and traditional greedy search algorithms. Approaches based on SA and other non-greedy iterative algorithms have proven

highly effective in recent years for several hard problems in the realm of VLSI physical design, such as partitioning and placement [57].

## 1.9 CONTRIBUTIONS

In this thesis, we present novel hybrid nanophotonic-electric network-on-chip (NoC) architectures and synthesis techniques to optimize hybrid nanophotonic-electric NoC architectures for high performance and low power consumption. The main contributions of our work can be categorized in two key areas: architectural and algorithmic techniques.

Our first contribution is *METEOR*, a novel hybrid nanophotonic-electric NoC architecture that utilizes a low overhead photonic ring waveguide to complement a traditional 2D electrical mesh NoC. *METEOR* includes many novel features such as photonic region of influence (PRI), single write multiple read fast reservation channel and multiple write multiple read (SWMR-MWMR) low power data channels, and serialization for gateway interfaces. Experimental results indicate a strong motivation for considering the *METEOR* hybrid nanophotonic-electric NoCs for future CMPs, demonstrating as much as a 13× reduction in power consumption as well as improved throughput and access latencies, compared to traditional electrical 2D mesh and torus NoC architectures.

An enhancement to the above architecture is proposed to support multiple use-case chip multiprocessor (CMP) applications that require adaptive on-chip communication fabrics to cope with changing use-case performance needs. The proposed *UC-PHOTON* architecture is a novel hybrid nanophotonic-electric NoC communication architecture optimized to cope with the variable bandwidth and latency constraints of multiple use-case applications implemented on CMPs. Detailed experimental results indicate that *UC-PHOTON* can effectively adapt to meet diverse use-case traffic requirements and optimize energy-delay product and power dissipation,

with scaling CMP core counts and multiple use-case complexity. For the five multiple use-case applications we explored, *UC-PHOTON* shows up to 46× reduction in power dissipation and up to 170× reduction in energy-delay product compared to traditional electrical NoC fabrics, highlighting the benefits of using the novel communication fabric.

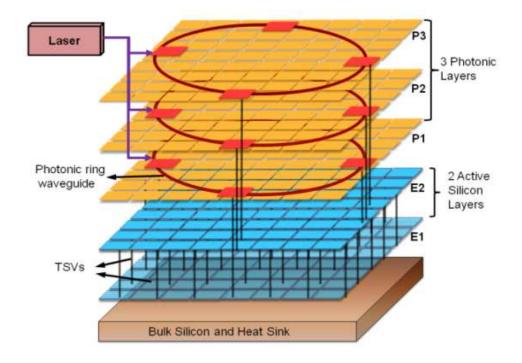

We extended the above work to address scalability issues with 2D ICs and demonstrated a novel multi-layer hybrid nanophotonic-electric NoC fabric called *OPAL* for 3D ICs. Our proposed hybrid nanophotonic-electric 3D NoC architecture combines low cost photonic rings on multiple photonic layers with a 3D mesh NoC in active layers to significantly reduce on-chip communication power dissipation and packet latency. *OPAL* also supports dynamic reconfiguration to adapt to changing runtime traffic requirements, and uncover further opportunities for reduction in power dissipation. Experimental results and comparisons with traditional 2D NoCs, 3D NoCs, and previously proposed hybrid nanophotonic-electric NoCs indicates a strong motivation for considering *OPAL* for future 3D ICs as it can provide orders of magnitude reduction in power dissipation and packet latencies.

As waveguide based hybrid nanophotonic NoCs are constrained due to high thermal tune up power, waveguide crossing losses, we proposed a heterogeneous free space photonics based hybrid nanophotonic-electric NoC architecture with multiple quantum well (MQW) devices and flip chip bonding. The photonic links, using micro-mirrors through free-space can be used to achieve single-hop direct communication links. The proposed architecture includes innovative mechanisms to address free-space collisions and combines single and multi-hop transfers to trade-off performance with power dissipation. We extended this architecture to 3D ICs and the resulting architecture allows for scalable and energy-efficient transfers in 3D ICs.

Any NoC architecture requires optimizations (synthesis) to allow tuning to application-specific characteristics. To date, prior work on automated NoC synthesis has mainly focused on electrical NoCs. For the first time, we proposed a suite of techniques for effectively synthesizing hybrid nanophotonic-electric NoCs with regular topologies by formulating and solving the synthesis problem using four search heuristics: (i) Ant Colony Optimization (ACO), (ii) Particle Swarm Optimization (PSO), (iii) Genetic Algorithm (GA), and (iv) Simulated Annealing (SA). Our experimental results reveal significant promise for the ACO and PSO based heuristics, with PSO achieving an average of 64% energy-delay improvements over GA and 53% over SA; and ACO achieving 107% improvements over GA and 62% over SA.

Finally, we have designed synthesis frameworks that can synthesize hybrid nanophotonic-electric NoCs with irregular topologies based on free-space photonics. The *HELIX* framework synthesizes application-specific hybrid nanophotonic-electric NoC architectures. This framework is also extended to 3D ICs. The resulting *3D-HELIX* framework synthesizes application-specific hybrid nanophotonic-electric 3D NoC architectures. These frameworks are the first to attempt to optimize hybrid nanophotonic-electric NoC architectures based on free-space photonics.

#### 1.10 OUTLINE

The research presented in this thesis is organized as follows. Chapter 2 discusses recent literature survey in the domain of 2D and 3D traditional electrical and nanophotonic NoC architectures as well as the prevailing NoC synthesis efforts that have been mainly focused on electrical NoCs. Chapter 3 describes our novel hybrid nanophotonic-electric ring-mesh NoC (METEOR) that utilizes a configurable photonic ring waveguide coupled to a traditional 2D electrical mesh NoC and analyzes performance based on parameter variations. Chapter 4

describes *UC-PHOTON*, a hybrid nanophotonic-electric NoC architecture optimized to cope with the variable bandwidth and latency constraints of multiple use-case applications implemented on CMPs. Chapter 5 presents a novel multi-layer hybrid nanophotonic-electric NoC fabric called *OPAL* for 3D ICs that combines low cost photonic rings on multiple photonic layers with a 3D mesh NoC in active layers to significantly reduce on-chip communication power dissipation and packet latency. Chapter 6 describes a suite of techniques for effectively synthesizing hybrid nanophotonic-electric NoCs with regular topologies. The synthesis problem is formulated and solved using several design space search heuristics. Chapter 7 describes the *HELIX* framework for application-specific synthesis of hybrid nanophotonic-electric NoC architectures with irregular topologies that combine electrical NoCs with free-space photonic links. Chapter 8 extends the *HELIX* framework to application-specific synthesis of hybrid nanophotonic-electric NoC architectures with irregular topologies in 3D ICs. Chapter 9 summarizes the conclusion of this thesis and lists some directions for future work.

### 2 LITERATURE SURVEY

This chapter describes key published work in the area of NoC architectures and synthesis techniques. We have made an effort to evaluate pros and cons for each approach presented in these works and also have discussed how the work presented in this thesis is different or complements previously published architectures and synthesis algorithms with an emphasis on the critical problems we are trying to address.

# 2.1 2D AND 3D ELECTRICAL NOC ARCHITECTURES

To overcome the power and latency limitations of traditional electrical NoC fabrics, several research efforts in recent years have focused on architectural customization of NoCs. These efforts aim to optimize performance and power constraints. For instance, [58] presents an interesting work to reduce communication latency and power dissipation in NoCs by inserting long links between certain cores. Express virtual channels are proposed in [59] that allow packets to bypass intermediate routers along their path, to reduce packet latency. Hybrid circuit-packet switched NoCs have been explored in [60] and shown to enable viable trade-offs between power and performance. Several works have also explored circuit-level techniques to reduce interconnect power, such as low swing signaling, power-optimal repeater design and insertion, current mode signaling, and pulsed transmission [61] [62] [63] [64] [65] [66]. Despite these and other architectural and circuit level advances in the field of NoC design, the International Technology Roadmap for Semiconductors (ITRS) [4] projects that in the near future, the fundamental limitations of copper-based electrical interconnects will become a serious bottleneck, requiring the exploration of innovative new technologies to sustain the evolution of

VLSI technology. On-chip networks in the Tilera 72 core [8] and Intel 80 [1] chips consume about 30-40% of the total power. This trend is expected to continue as more wire density becomes available within future process technologies [4]. Thus the expected on-chip network power will continue to rise as we scale to hundreds of cores on a single IC.