### DISSERTATION

# INVESTIGATION OF GROUP V DOPING AND PASSIVATING OXIDES TO REDUCE THE VOLTAGE DEFICIT IN CDTE SOLAR CELLS

Submitted by

Adam H. Danielson

Department of Mechanical Engineering

In partial fulfillment of the requirements

For the Degree of Doctor of Philosophy

Colorado State University

Fort Collins, Colorado

Fall 2022

Doctoral Committee:

Advisor: W.S. Sampath

Susan P. James Ketul C. Popat James R. Sites Copyright by Adam Danielson 2022

All Rights Reserved

#### ABSTRACT

# INVESTIGATION OF GROUP V DOPING AND PASSIVATING OXIDES TO REDUCE THE VOLTAGE DEFICIT IN CDTE SOLAR CELLS

Thin film cadmium telluride is one of the most successful photovoltaic technologies on the market today. Second only to silicon in yearly output and accounting for 40% of U.S. utilityscale photovoltaic installation, CdTe is known for its ease of manufacture, ideal bandgap, and low levelized cost of energy. Despite its commercial success, CdTe underperforms compared to its theoretical potential. The current world record CdTe device is only 21.0% compared to a theoretical maximum of 33.1%. This significant discrepancy in efficiencies can mostly be attributed to the poor open-circuit voltage of CdTe devices. Compared to silicon technologies, CdTe has a large voltage deficiency, exceeding 250 mV.

While copper doping has traditionally been used for CdTe devices, it has proven to be incapable of sufficiently doping CdTe. Copper typically dopes CdTe in the  $10^{14}$  to  $10^{15}$  holes/cm<sup>3</sup> range where most models predict that  $10^{16}$ – $10^{17}$  is needed. Additionally, interstitial copper is a fast diffuser in CdTe, and can lead to numerous stability issues. As an alternative to copper, this work explores arsenic as a dopant for CdTe. Using a novel arsenic doping technique, hole concentrations greater than  $10^{15}$  cm<sup>-3</sup>, microsecond lifetimes, and increased radiative efficiency are achieved. These are important prerequisites to achieving higher voltages.

Achieving high doping levels alone is not sufficient to achieve higher device performance. A well-passivated and carrier selective contact is needed to ensure that electron-

ii

hole pairs do not recombine and are extracted as useable energy. Aluminum oxide has been shown to passivate CdTe surfaces. This work illustrates the explorations of using  $Al_2O_3$  as a passivation layer, pairing it with highly doped amorphous silicon as a hole contact, resulting in excess-carrier lifetimes up to 8 µs, the highest reported to date for polycrystalline Cd(Se)Te.

Although the inclusion of arsenic doping and an aluminum oxide back contact are each explored separately, the combination of both methods result in massive improvements to the carrier lifetime, interface passivation and radiative efficiency. Through this combination, microsecond lifetime and External Radiative Efficiency of over 4% are achieved. The excellent ERE values measured here are indicative of large quasi-Fermi level splitting, leading to an implied voltage with multiple device structures of nearly 1 V and an implied voltage of 25%.

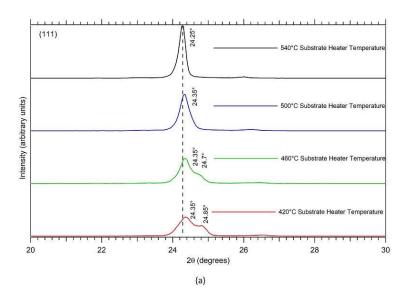

Finally, while CdSeTe serves as a more promising photovoltaic absorber candidate compared to CdTe, certain difficulties remain which must be addressed. Careful selection of processing conditions is shown to create a dense and large-grained film while eliminating wurtzite-phase crystal growth, which has been shown to degrade device performance. Surprisingly, as-deposited CdSeTe is shown to be n-type or nearly intrinsic rather than the previously supposed p-type. This necessitates additional steps to account for very poor hole conductivity, which can produce zero-current devices if not addressed. Challenges notwithstanding, CdSeTe absorbers are shown to be a key component in devices capable of a photovoltaic conversion efficiency of greater than 25%.

iii

#### ACKNOWLEDGMENTS

I would like to thank my lab mates and peers for their assistance, knowledge and comradery through many long hours in the lab. Specifically, I would like to thank Amit Munshi for first teaching me how to create solar cells and for the many lessons since. I would like to thank Carey Reich for the many fruitful and enjoyable discussions on solid state physics and philosophy in equal measure, and for demanding experimental and scientific rigor which made all of our work better. Arthur Onno's expertise in solid state physics and fundamental solar cell operation was foundational to this work, I owe him a great deal. Aanand Thiyagarajan, Akash Shah, and Anthony Nicolson, I would like to thank for their DFT insights and attempts to bridge the gap between the theoretical and the experimental. Finally, I would like to thank Alex Bothwell, Jen Drayton, Tushar Shimpi, Larry Maple, Kurt Barth, Anna Kindvall, Pascal Jundt, Ramesh Pandey, Ben Strauss, Daniel Shaw, Camden Kasik and Kevan Cameron for their collaboration, expertise, and support throughout my time here.

Additionally, I would like to acknowledge my advisor Dr. Walajabad Sampath for his inexhaustible wealth of photovoltaic and CdTe knowledge and the tens of thousands of hours of reading, studying, and preparing for our discussions and lectures together. I would also like to thank Dr. Sampath for his personal contributions and sacrifices to this field, which in many ways paved the way for CdTe, enabling research such as this. Furthermore, I wish to thank and acknowledge the members of my dissertation committee: Dr. Susan James, Dr. Ketul Popat, and Dr. James Sites for their support over the years. Their expertise has been invaluable to me over these past years and I am grateful for their combined efforts on my behalf.

iv

I would like to thank my parents, Bob and Cheryl, and my sister Rachel for their lifelong support in all of my endeavors, this not least of all. They instilled in me a love of learning which has been with me all my life. Without their unconditional support, this would not have been possible. Finally, and most importantly, I would like to thank my wife, Jenn, and my son, Liam, for making this world worth saving.

This material is based upon work supported by the U.S. Department of Energy's Office of Energy Efficiency and Renewable Energy (EERE) under the Solar Energy Technologies Office Award Number DE-EE0008557 and DEEE0008552. This work is partly funded by National Science Foundation I/UCRC (Award Number – 1540007 and 1821526). The author would like to thank the NSF I/UCRC Industrial Advisory Board for their guidance and support. Some of the deposition materials used in this work were provided by 5N Plus Inc. as in-kind support.

## TABLE OF CONTENTS

| ABSTRACTii |                    |                                                                                    |  |  |

|------------|--------------------|------------------------------------------------------------------------------------|--|--|

| ACKN       | ACKNOWLEDGMENTS iv |                                                                                    |  |  |

| LIST (     | LIST OF TABLES xi  |                                                                                    |  |  |

| LIST (     | OF FIC             | JURES                                                                              |  |  |

| LIST (     | OF NC              | MENCLATURE xvi                                                                     |  |  |

| СНАР       | TER                | 1. INTRODUCTION                                                                    |  |  |

| 1.1        | Wh                 | at are Photovoltaics?                                                              |  |  |

| 1.2        | Cor                | version of Thermal Radiation into Chemical Energy7                                 |  |  |

| 1.3        | Cor                | version of Chemical Energy into Electrical Energy 10                               |  |  |

| 1.         | .3.1               | Charge carrier selectivity and selecting appropriate electron and hole contacts 13 |  |  |

| 1.         | .3.2               | P-N Junctions                                                                      |  |  |

| 1.4        | Pho                | tovoltaics as Diodes                                                               |  |  |

| 1.5        | Cor                | nmon Characterization Techniques                                                   |  |  |

| 1.         | 5.1                | Current Density vs Voltage                                                         |  |  |

| 1.         | .5.2               | Steady-State Photoluminescence and Cathodoluminescence                             |  |  |

| 1.         | 5.3                | External Radiative Efficiency                                                      |  |  |

| 1.         | .5.4               | Time-Resolved Photoluminescence                                                    |  |  |

| 1.         | .5.5               | Capacitance vs Voltage and Capacitance vs Frequency                                |  |  |

| 1.         | 5.6                | External Quantum Efficiency                                                        |  |  |

| СНАР       | TER                | 2. THE NEED FOR SOLAR ENERGY                                                       |  |  |

| 2.1        | Wor                | ld Energy Needs                                                                    |  |  |

| 2.2        | Glob               | al Climate Change                                                                  |  |  |

| 2.3        | The                | Growth of Photovoltaics                                                            |  |  |

| 2.4        | The                | Falling Cost of Solar                                                              |  |  |

| СНАР       | TER                | 3. THE ADVANTAGES OF CdTe OVER Si                                                  |  |  |

| 3.1        | Max                | imum Theoretical Efficiency54                                                      |  |  |

| 3.2        | Man                | ufacturability                                                                     |  |  |

| 3.         | 2.1                | Device Fabrication at Colorado State University                                    |  |  |

| 3.3 | Ene   | ergy Payback and Harmful Emissions                           | 61 |

|-----|-------|--------------------------------------------------------------|----|

| 3.4 | Per   | formance in Hot/Humid Climates                               | 63 |

| CHA | PTEF  | <b>4.</b> MAJOR ISSUES IMPEDING > 22% CdTe DEVICES           | 65 |

| 4.1 | The   | coretical Performance of CdTe                                | 65 |

| 2   | 4.1.1 | Voltage Deficit in CdTe                                      | 65 |

| 4.2 | Cha   | arge Carrier Concentration                                   | 67 |

| 4.3 | Cha   | arge Carrier Lifetime                                        | 68 |

| 4.4 | Sur   | face/Interface Recombination                                 | 69 |

| 4.5 | Inte  | erdependence                                                 | 70 |

| 4   | 4.5.1 | Interdependence of Doping and Bulk Lifetime                  | 71 |

| 4   | 4.5.2 | Interdependence of Doping and Interface Recombination        | 71 |

| 4   | 4.5.3 | Interdependence of Bulk Lifetime and Interface Recombination | 72 |

| 4   | 4.5.4 | Quasi Fermi-level                                            | 72 |

| 4.6 | Мо    | deling Results                                               | 73 |

| 4   | 4.6.1 | Kanevce Model                                                | 74 |

| 4   | 4.6.2 | Ablekim Model                                                | 74 |

| 4   | 4.6.3 | Duenow Model                                                 | 74 |

| CHA | PTEF  | <b>8 5.</b> GROUP V DOPING                                   | 77 |

| 5.1 | Lin   | nitations of Copper Doping                                   | 77 |

| 5   | 5.1.1 | Self Compensation                                            | 77 |

| 4   | 5.1.2 | Low Activation                                               | 78 |

| 5   | 5.1.3 | Copper Mobility and Grain Boundary Segregation               | 79 |

| 5   | 5.1.4 | Carrier Lifetime in Cu-doped Devices                         | 80 |

| 5.2 | Gro   | oup V Doping                                                 | 81 |

| 4   | 5.2.1 | Previous Group V Dopant Work                                 | 81 |

| 4   | 5.2.2 | Previous Arsenic Doping Work                                 | 83 |

| 5.3 | Hy    | pothesis I                                                   | 85 |

| 4   | 5.3.1 | Device Structure                                             | 86 |

| 4   | 5.3.2 | Co-sublimation Hardware and Cadmium Overpressure             | 87 |

| 5.4 | Hy    | pothesis I Results                                           | 88 |

| 5   | 5.4.1 | JV Performance                                               | 88 |

|     | 5.4.2        | Arsenic Incorporation                                                 | 89  |

|-----|--------------|-----------------------------------------------------------------------|-----|

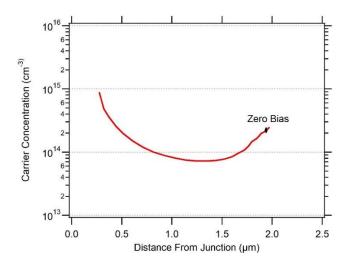

|     | 5.4.3        | Acceptor Concentration                                                | 90  |

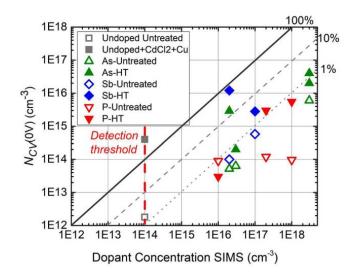

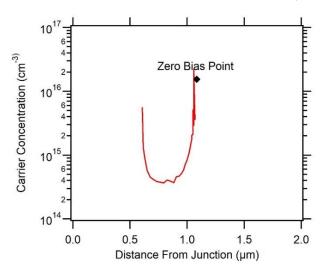

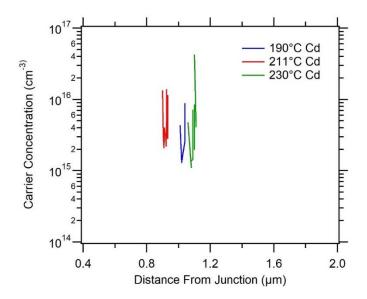

|     | 5.4.3.1      | Dopant Activation                                                     | 93  |

|     | 5.4.4        | Carrier Lifetimes                                                     | 93  |

|     | 5.4.5        | External Radiative Efficiency                                         | 94  |

|     | 5.4.6        | Scanning Electron Microscopy and Energy-Dispersive X-Ray Spectrometry | 95  |

|     | 5.5 (        | Conclusions                                                           | 96  |

| СН  | APTEF        | <b>R 6.</b> DIFFUSED-ARSENIC DOPING                                   | 98  |

| 6   | <b>.1</b> Hy | pothesis II                                                           | 98  |

|     | 6.1.1        | Diffused-Arsenic Methodology                                          | 98  |

|     | 6.1.2        | Device Structure                                                      | 98  |

| 6.2 | Нурс         | othesis II Results                                                    | 100 |

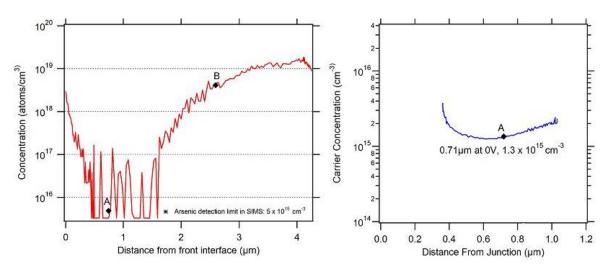

|     | 6.2.1        | Arsenic Incorporation                                                 | 100 |

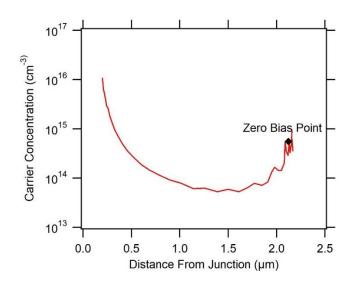

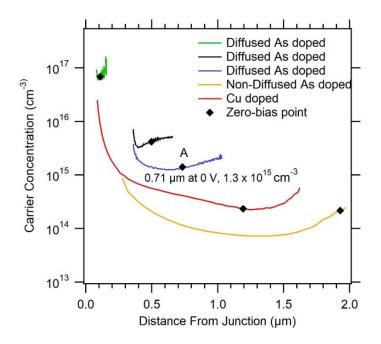

|     | 6.2.2        | Acceptor Concentration                                                | 102 |

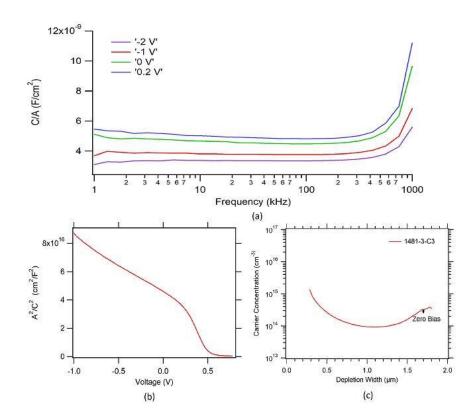

|     | 6.2.2.1      | Capacitance-Voltage                                                   | 102 |

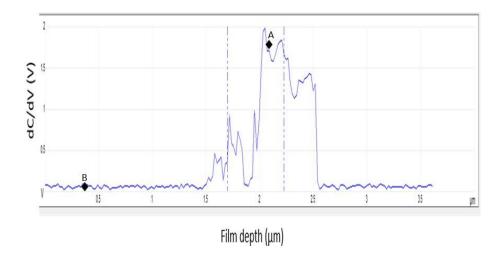

|     | 6.2.2.2      | 2 Scanning Capacitance Microscopy                                     | 104 |

|     | 6.2.2.3      | B Dopant Activation                                                   | 105 |

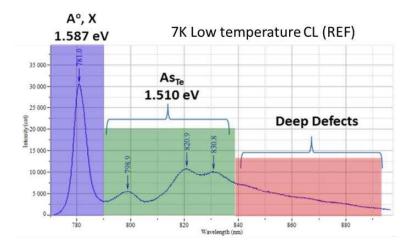

|     | 6.2.3        | Luminescence                                                          | 106 |

|     | 6.2.4        | Carrier Lifetimes                                                     | 107 |

|     | 6.2.5        | Interface Passivation                                                 | 110 |

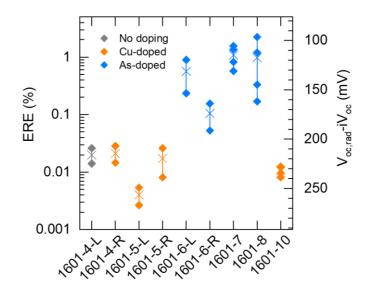

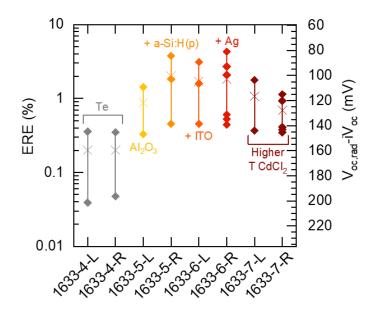

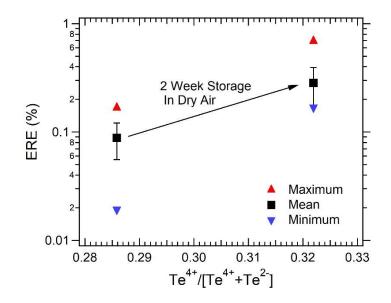

|     | 6.2.6        | External Radiative Efficiency                                         | 112 |

|     | 6.2.6.1      | Band Tails and Reduced Theoretical Maximum Voltage                    | 114 |

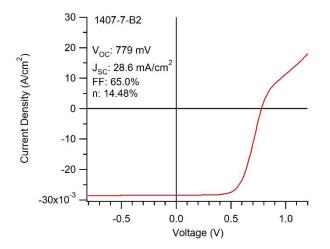

|     | 6.2.7        | JV Performance                                                        | 116 |

|     | 6.3 (        | Conclusions                                                           | 120 |

| CH  | APTEF        | <b>R7.</b> PASSIVATING OXIDES AND SELECTIVE CONTACTS                  | 121 |

| 7   | .1 Inte      | erface Passivation Mechanisms                                         | 121 |

|     | 7.1.1        | Chemical Passivation                                                  | 121 |

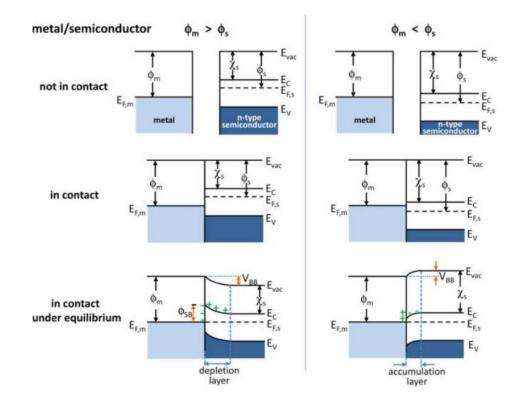

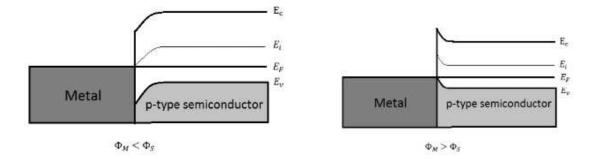

|     | 7.1.2        | Field Effect Passivation                                              | 122 |

| 7   | .2 Pre       | vious Passivating Oxide Work                                          | 125 |

|     | 7.2.1        | Electron Contact Work                                                 | 125 |

|     | 7.2.2        | Hole Contact Work                                                     | 127 |

| 7.  | 3 Hyp        | pothesis III                                                                  | . 131 |

|-----|--------------|-------------------------------------------------------------------------------|-------|

| 7.  | <b>4</b> Hy  | pothesis III Results                                                          | . 132 |

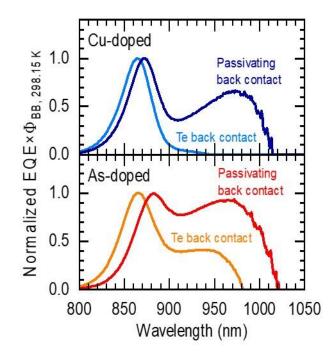

|     | 7.4.1        | Luminescence Results                                                          | . 132 |

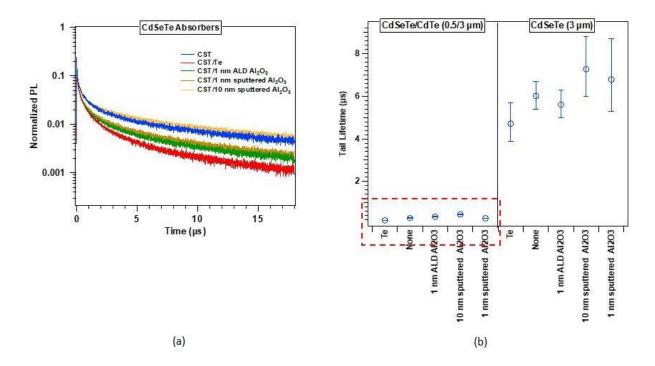

|     | 7.4.2        | Carrier Lifetimes                                                             | . 134 |

|     | 7.4.3        | Interface Passivation                                                         | . 136 |

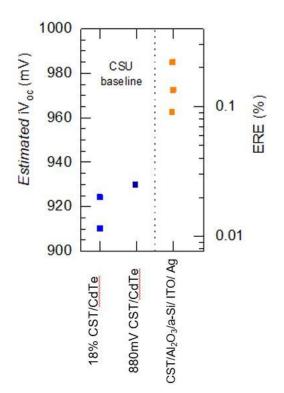

|     | 7.4.4        | External Radiative Efficiency                                                 | . 137 |

|     | 7.4.4.1      | Band Tails/sub bandgap features                                               | . 138 |

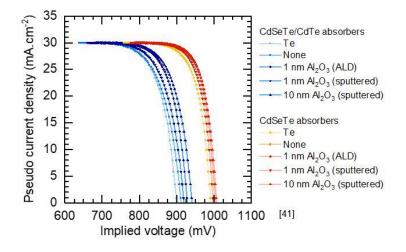

|     | 7.4.4.2      | Implied JV Curves                                                             | . 139 |

|     | 7.4.5        | JV Performance                                                                | . 141 |

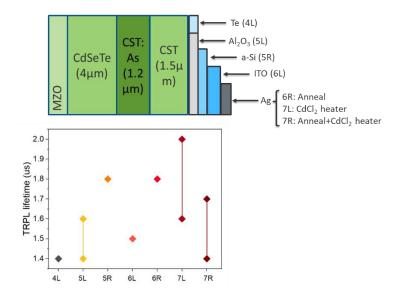

| 7.  | 5 Res        | sults of Combining Al <sub>2</sub> O <sub>3</sub> and Diffused-Arsenic Doping | . 142 |

|     | 7.5.1        | Carrier Lifetimes                                                             | . 142 |

|     | 7.5.2        | Interface Recombination                                                       | . 143 |

|     | 7.5.3        | External Radiative Efficiency                                                 | . 144 |

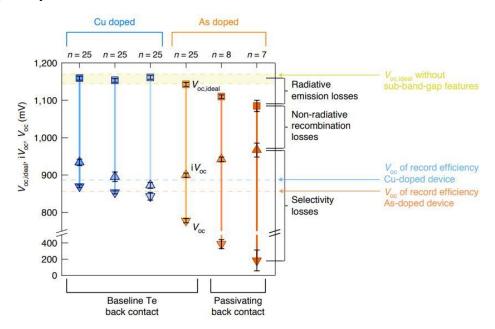

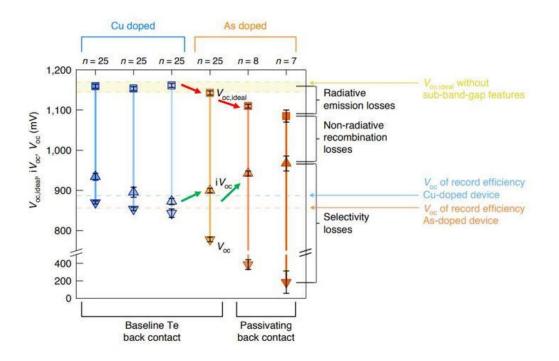

|     | 7.5.4        | Implied Voltage and Voltage Loss Analysis                                     | . 146 |

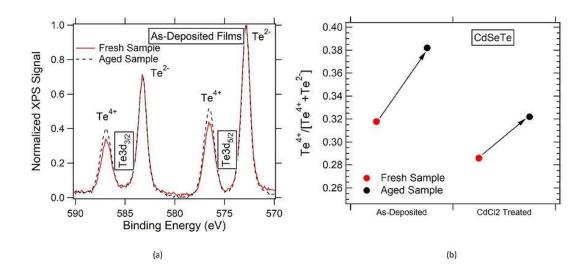

| 7.  | 6 TeC        | D <sub>x</sub> Passivation                                                    | . 149 |

| 7.  | 7 Cor        | nclusions                                                                     | . 151 |

| CH  | APTER        | <b>8.</b> EXTRACTING CURRENT FROM CdSeTe-ONLY DEVICES                         | . 153 |

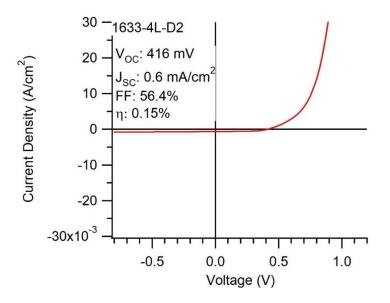

| 8.  | 1 Zer        | o Current Device                                                              | . 153 |

| 8.  | 2 Hyp        | pothesis IV                                                                   | . 156 |

| 8.  | <b>3</b> Нур | pothesis IV Results                                                           | . 156 |

|     | 8.3.1        | Determining Carrier Type                                                      | . 156 |

|     | 8.3.1.1      | Hall Effect and Hot Probe Measurements                                        | . 157 |

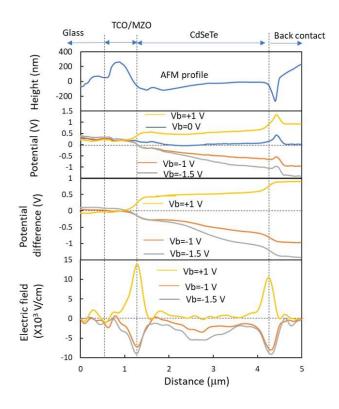

|     | 8.3.1.2      | Scanning Kelvin-Probe Microscopy Measurements                                 | . 157 |

|     | 8.3.2        | Wurtzite Phase CdSeTe                                                         | . 158 |

|     | 8.3.3        | Microstructural Changes and CdCl <sub>2</sub> Accumulation                    | . 161 |

| 8.  | 4 Rec        | covering Current in CdSeTe-only devices                                       | . 166 |

| 8.  | 5 Cor        | nclusions                                                                     | . 169 |

| CH  | APTER        | <b>89.</b> CONCLUSIONS AND FUTURE WORK                                        | . 172 |

| 9.1 | Concl        | usions                                                                        | . 172 |

| 9.2 | Future       | e Work                                                                        | . 175 |

|     | 9.2.1        | Optimizing CdSeTe-only devices                                                | 175   |

|              | 9.2.2 Explore undoped CdSeTe devices to maximize implied voltage |                                                     | 177 |

|--------------|------------------------------------------------------------------|-----------------------------------------------------|-----|

|              | 9.2.3                                                            | Utilize Arsenic doping to improve hole conductivity | 178 |

|              | 9.2.4                                                            | Find an effective hole contact for Cd(Se)Te         | 178 |

| TAI          | TABLE OF SAMPLES                                                 |                                                     |     |

| REFERENCES   |                                                                  |                                                     |     |

| PUBLICATIONS |                                                                  |                                                     |     |

## LIST OF TABLES

| Table 1. Current losses in a Cu(InGa)Se <sub>2</sub> device as measured by QE                                | 32    |

|--------------------------------------------------------------------------------------------------------------|-------|

| Table 2. Atmospheric concentrations of greenhouse gasses                                                     | 42    |

| Table 3. Comparison of current CdTe/c-Si performance to theoretical limits                                   | 65    |

| Table 4. Dopant defect energy levels                                                                         | 83    |

| Table 5. Average excess-carrier lifetime for diffused vs non-diffused arsenic-doped samples                  | 110   |

| Table 6. Back interface recombination velocities using various dopants                                       | . 111 |

| Table 7. Back interface recombination velocities for CdSeTe/CdTe w/ various back contacts                    | 137   |

| Table 8. Back surface recombination velocities for devices with As-doping and Al <sub>2</sub> O <sub>3</sub> | . 144 |

| Table 9. Implied V <sub>OC</sub> calculations for various device structures                                  | . 147 |

| Table 10. Current collection for CdSeTe samples with Cu-doping and an acid etch                              | . 168 |

| Table 11. Summary of Key Findings                                                                            | . 175 |

|                                                                                                              |       |

## LIST OF FIGURES

| Figure 1. Periodic Table of the Elements                                                           | 2    |

|----------------------------------------------------------------------------------------------------|------|

| Figure 2: Energy band diagram showing energy states spread into bands                              | 3    |

| Figure 3. Extraterrestrial (AM0) Solar Spectrum                                                    |      |

| Figure 4. Band Gaps of various materials                                                           | 6    |

| Figure 5. N and P-type doping in semiconductors                                                    | 7    |

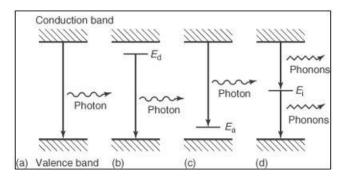

| Figure 6. Band diagrams for various recombination methods                                          | 9    |

| Figure 7. Quasi-Fermi Levels in an absorber under illumination                                     | . 10 |

| Figure 8. Band diagram of CdSeTe at J <sub>sc</sub>                                                | . 12 |

| Figure 9. Band diagram of CdSeTe at V <sub>OC</sub>                                                | . 13 |

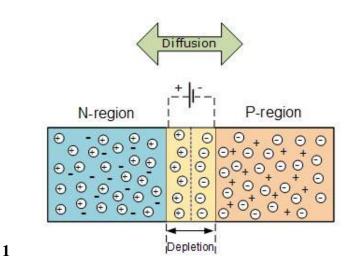

| Figure 10. Diagram showing quasi-Fermi levels, the implied voltage, and contact selectivity        | . 14 |

| Figure 11. Diagram of a P-N Junction                                                               | . 16 |

| Figure 12. Typical Diode IV Curve                                                                  | . 18 |

| Figure 13. JV curve showing key PV parameters                                                      | . 19 |

| Figure 14. CdTe substrate in CSU's JV tester                                                       | . 22 |

| Figure 15. Diagram illustrating the effects of changing series & shunt resistance                  | . 22 |

| Figure 16. Experimental Setup for Measuring Steady-State Photoluminescence                         | . 23 |

| Figure 17. Diagram of Radiative and Non-Radiative recombination                                    | . 24 |

| Figure 18. Steady-State PL spectra                                                                 | . 24 |

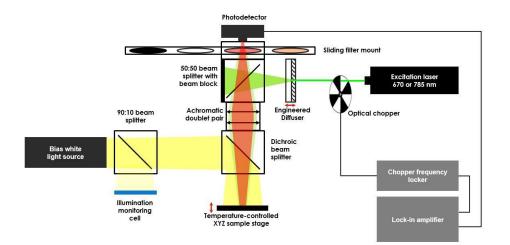

| Figure 19. Experimental Setup for Measuring External Radiative Efficiency (ERE)                    | . 25 |

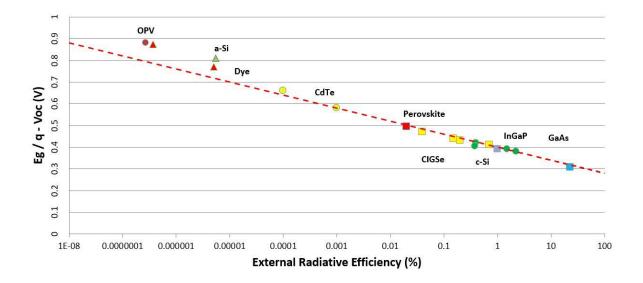

| Figure 20. Voltage Deficit vs External Radiative Efficiencies for Various Technologies             | . 26 |

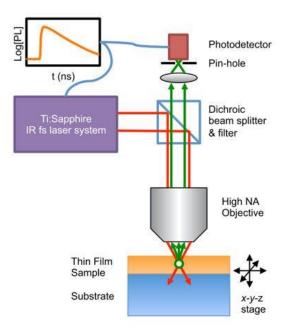

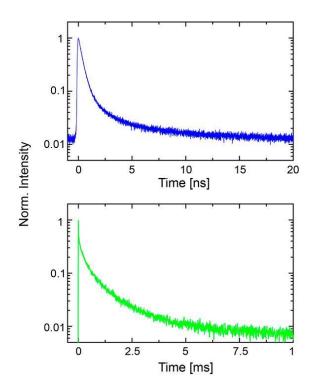

| Figure 21. Experimental Setup for Measuring Time-Resolved Photoluminescence                        | . 28 |

| Figure 22. TRPL decay curves for GaAs (Top) and Si (Bottom)                                        | . 28 |

| Figure 23. (a) CF Plot, (b) Mott-Schottky Plot, and (c) CV profiles for a CdTe device              | . 30 |

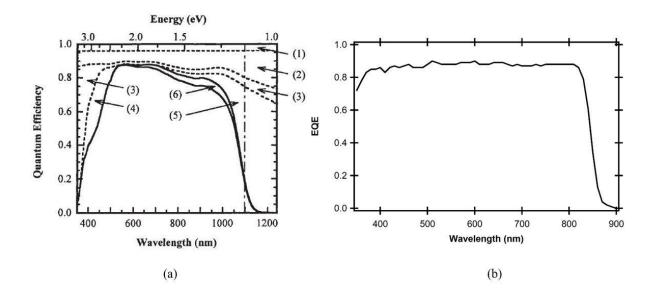

| Figure 24. (a) EQE curve for a Cu(InGa)Se <sub>2</sub> Solar Cell, adopted from [18]. (b) EQE of a |      |

| baseline CdSeTe/CdTe device fabricated at CSU                                                      | . 32 |

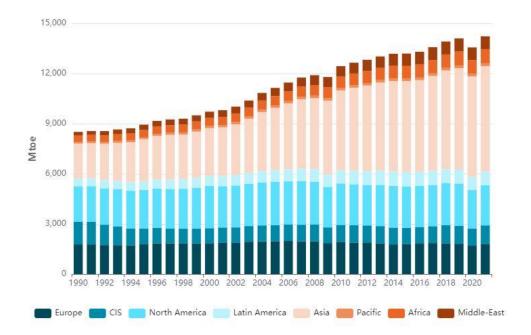

| Figure 25. World Energy Consumption by Year                                                        | . 33 |

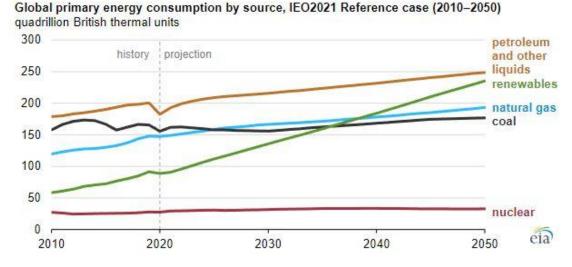

| Figure 26. World energy consumption by energy source (2010-2050)                                   | . 34 |

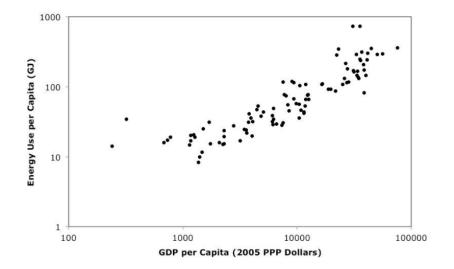

| Figure 27. Energy Use vs GDP                                                                       | . 35 |

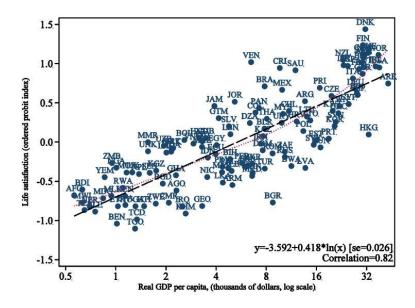

| Figure 28. Life Satisfaction vs GDP                                                                | . 35 |

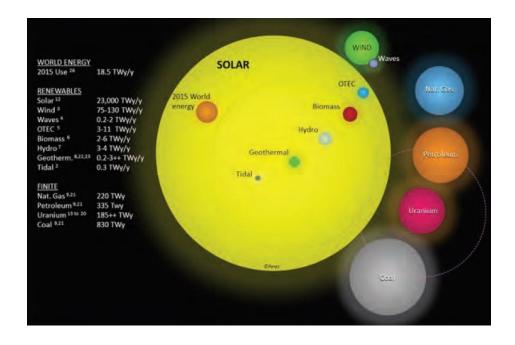

| Figure 29. Comparison of Energy Resources & Global Energy Consumption                              | . 36 |

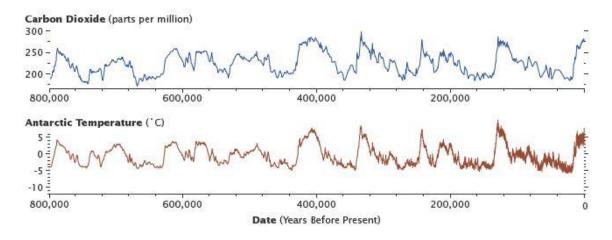

| Figure 30. Atmospheric CO <sub>2</sub> and Temperatures                                            | . 38 |

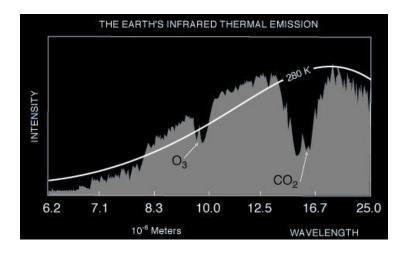

| Figure 31. Earth's Infrared Emission Spectrum                                                      | . 38 |

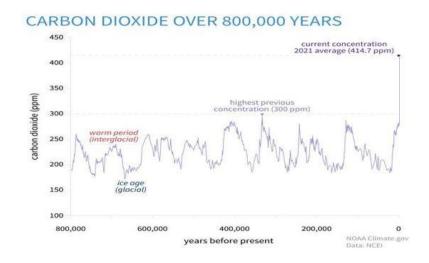

| Figure 32. Historic and Current Atmospheric CO <sub>2</sub> concentration                          | . 39 |

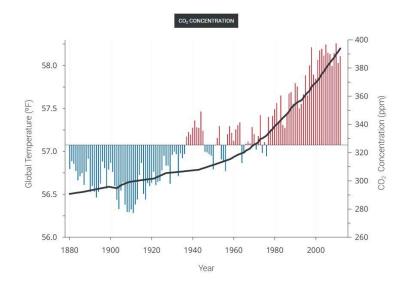

| Figure 33. Global Temperatures and CO <sub>2</sub> by year                                         | . 40 |

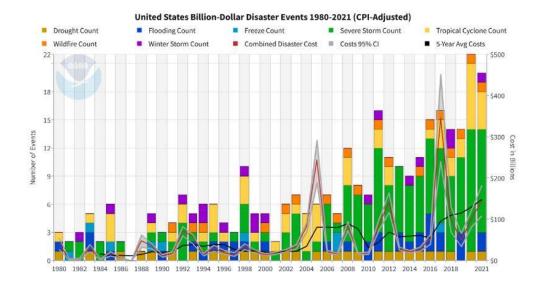

| Figure 34. Billion Dollar Disasters per Year                                                       | . 41 |

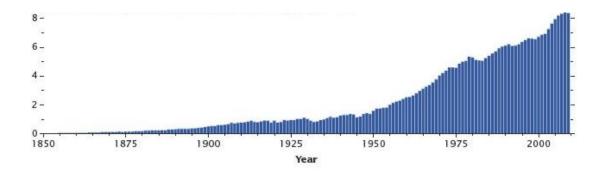

| Figure 35. Global Carbon Dioxide Emissions (Gigatons of Carbon per Year                            | . 42 |

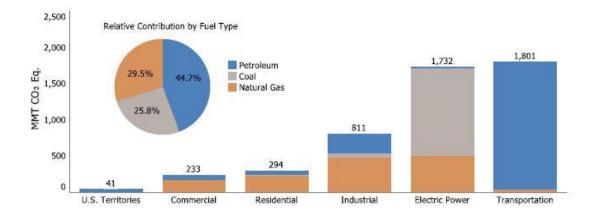

| Figure 36. Relative Contribution of CO <sub>2</sub> Emission by industrial sector and fuel type    | . 43 |

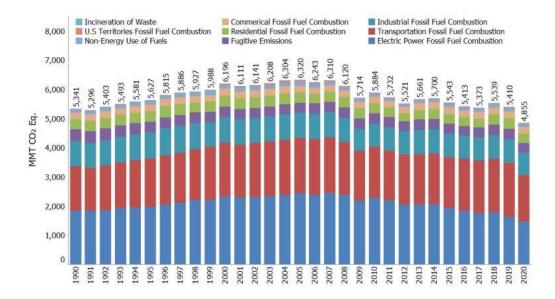

| Figure 37. U.S. Greenhouse Emissions by Sector, Over Time                                          | . 44 |

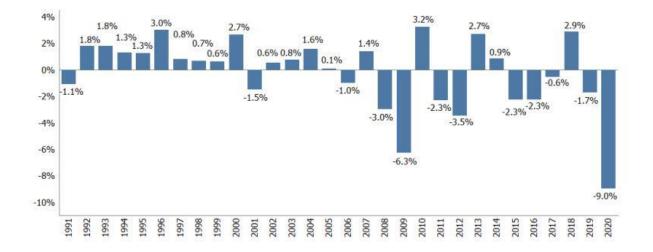

| Figure 38. | Percent Change per year, U.S Gross Greenhouse Gas Emissions                       | 44 |

|------------|-----------------------------------------------------------------------------------|----|

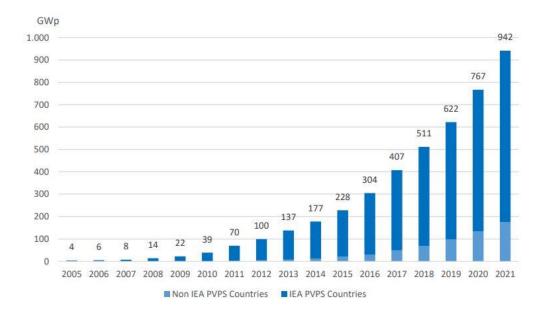

|            | Global PV capacity                                                                |    |

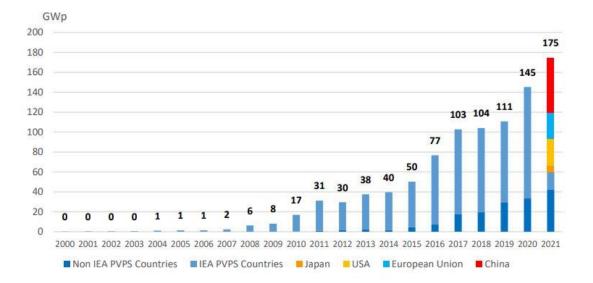

| Figure 40. | Annual PV Installations Worldwide                                                 | 46 |

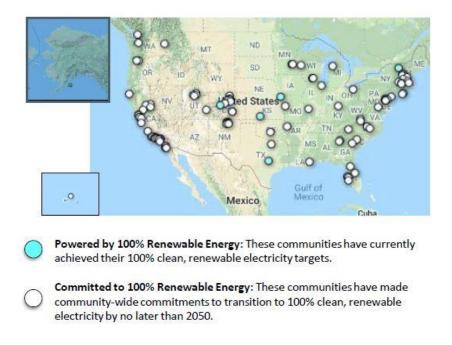

| Figure 41. | American Cities with a 100% Renewable Energy Commitment                           | 48 |

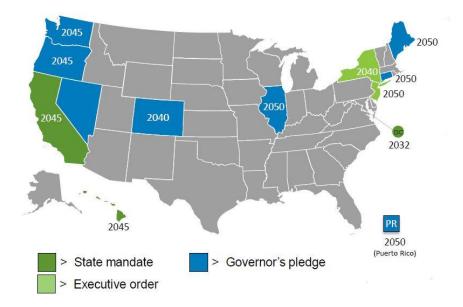

| Figure 42. | American States with 100% renewable energy commitments                            | 48 |

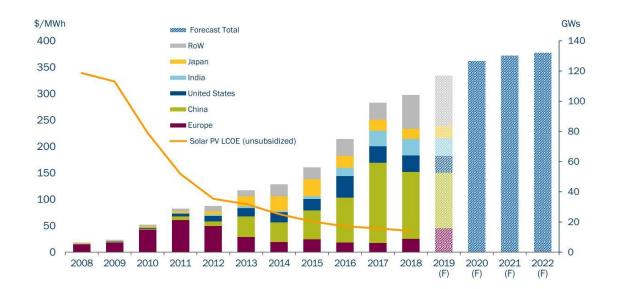

| 0          | PV Cost vs Global installation                                                    |    |

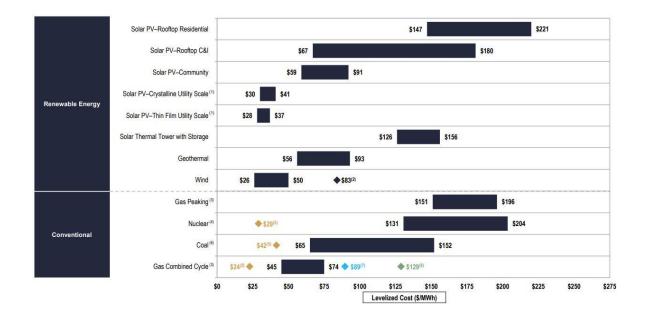

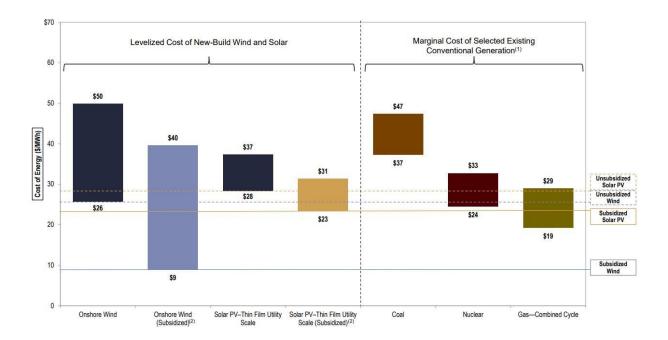

| Figure 44. | U.S. Levelized Cost of Energy                                                     | 50 |

| Figure 45. | Cost of New Solar vs Marginal Cost of Existing Conventional Generation            | 51 |

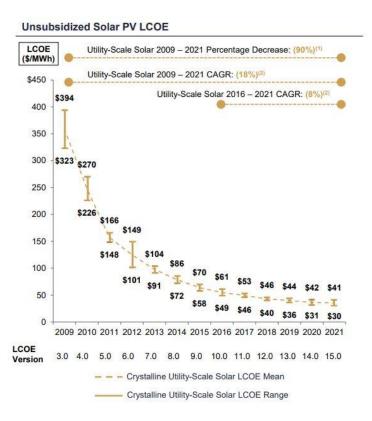

| 0          | Solar PV Learning Curve                                                           |    |

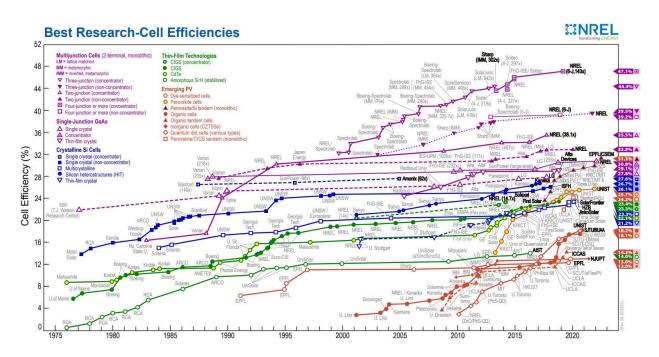

| -          | NREL Research Cell Efficiency Chart                                               |    |

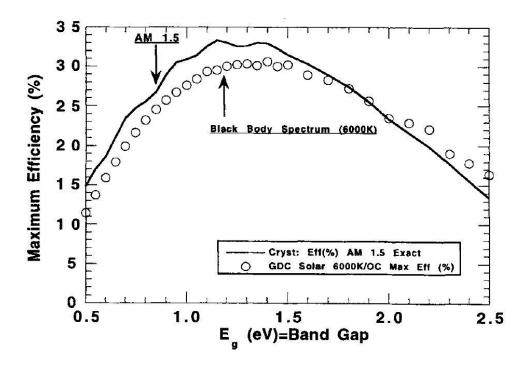

| Figure 48. | Theoretical Maximum Efficiency of a Single-Junction PV Device                     | 55 |

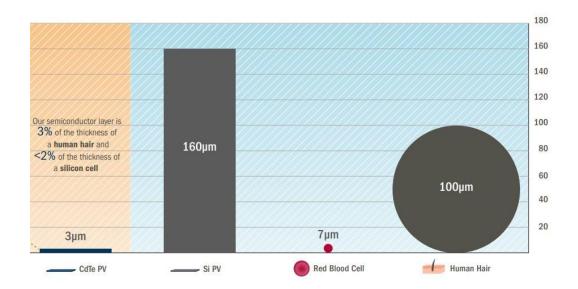

| 0          | Silicon vs CdTe absorber thickness                                                |    |

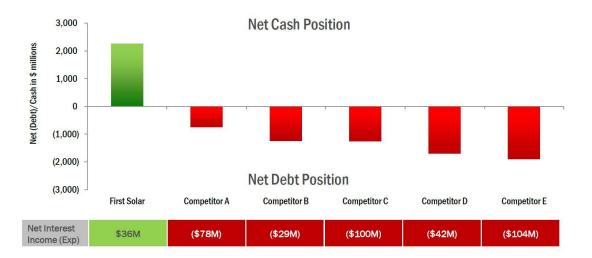

| Figure 50. | Net Cash to Debt for Six PV manufacturers as of 2019                              | 59 |

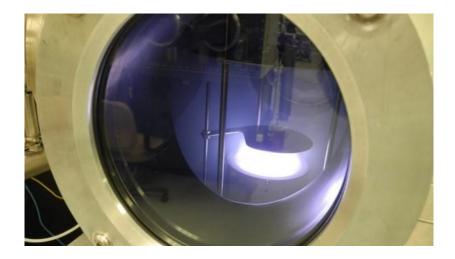

| •          | MgZnO deposited via magnetron sputtering                                          |    |

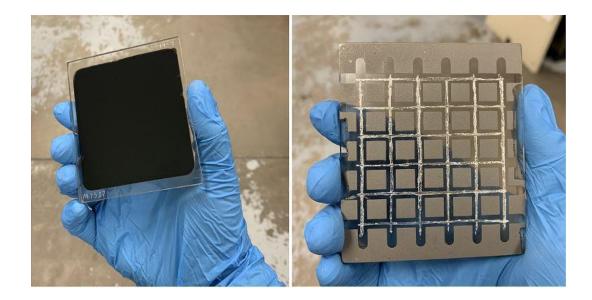

|            | Cd(Se)Te film seen from the front (left), and finished devices seen from the back |    |

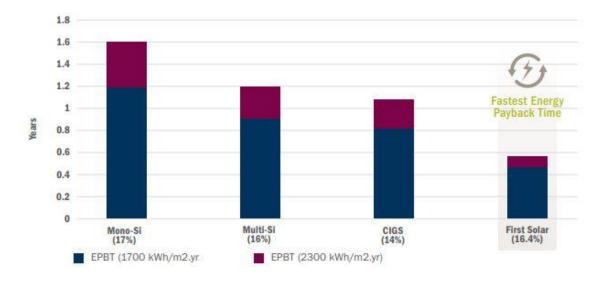

|            | Energy Payback Period for Four PV technologies                                    |    |

| -          | Carbon Footprint of Electricity Generating Technologies                           |    |

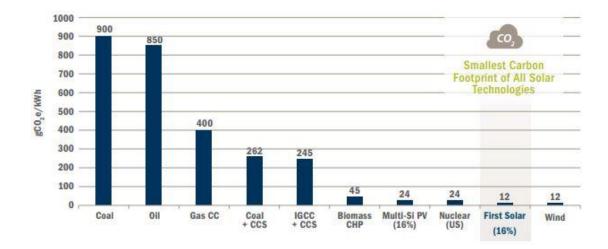

| -          | Energy Yield Advantage for CdTe vs Si                                             |    |

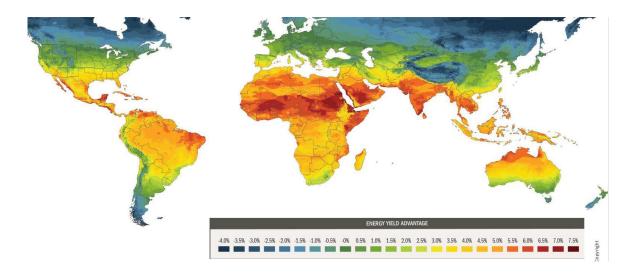

| -          | JV Plot and conversion efficiency parameters for CSU champion device              |    |

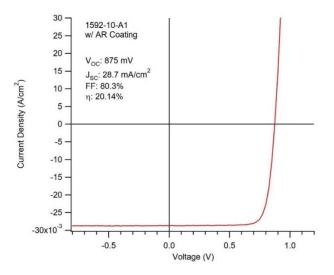

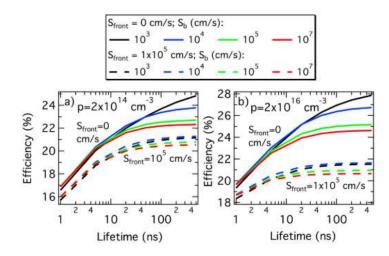

| -          | Modelled device efficiencies as a function of doping, lifetime and recombination  |    |

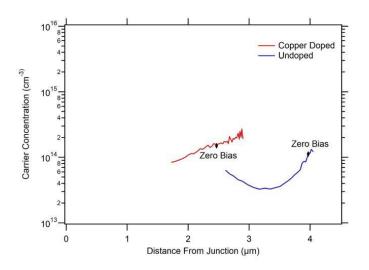

| e          | Comparison of CV profiles for a Cu-doped and undoped sample                       |    |

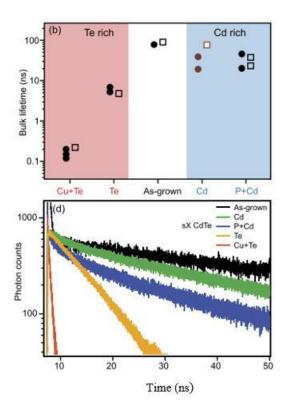

|            | CdTe lifetimes using varying dopants                                              |    |

| -          | Carrier Concentration and Dopant Concentration                                    |    |

|            | Device structure used in the initial arsenic-doping experiments                   |    |

|            | Co-sublimation Hardware used in Arsenic Doping Experiments                        |    |

| e          | JV curve for a 16.8% CdSeTe/CdTe:As Device                                        |    |

| -          | Arsenic profiles of CdTe:As films deposited under varying Cd overpressure         |    |

| 0          | CV Profile for the 16.8% CdSeTe/CdTe:As arsenic-doped device (1379-7)             |    |

| e          | CV Profile of a CdSeTe:As/CdTe/CdSeTe device (1732-8R)                            |    |

| e          | CV Profile of a CdSeTe:As-only device (1886-3)                                    |    |

| -          | CV Profiles for CdTe:As samples deposited under various cadmium overpressure      |    |

| -          | TRPL decays for a 2 µm CdSeTe:As sample under various injection levels            |    |

| -          | SEM/EDS Map for CdSeTe:As source charge showing high arsenic concentration.       |    |

|            | SEM/EDS Map for CdTe:As source charge showing high arsenic concentration          |    |

| -          | Device structure used in the diffused arsenic-doping experiments                  |    |

| -          | Diagram of the arsenic diffusion process                                          |    |

| -          | SIMS showing the arsenic profile of a "diffused" sample (1546-7) 10               |    |

| -          | SIMS showing the arsenic profile of a "diffused" sample (1968-2) 10               |    |

|            | CV profiles for three different diffused-arsenic devices 10                       |    |

| Figure 77. | Scanning Capacitance Microscopy measurements of a diffused-arsenic device10       | )5 |

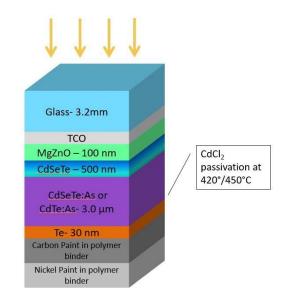

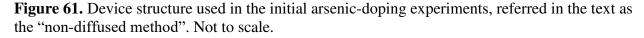

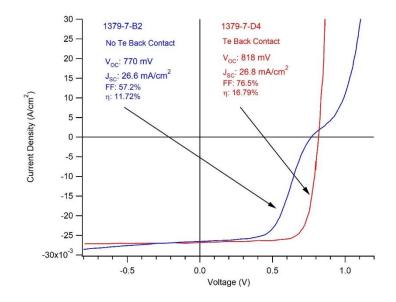

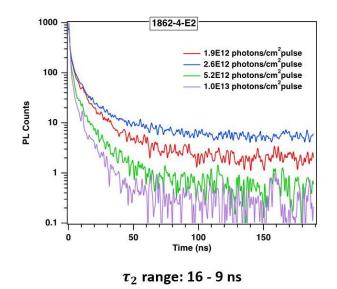

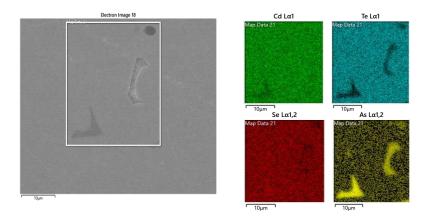

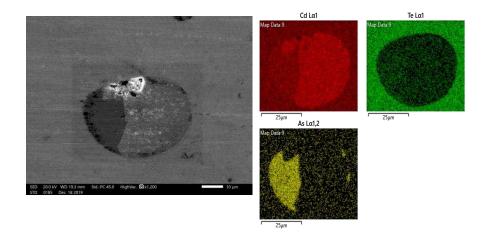

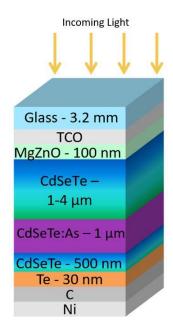

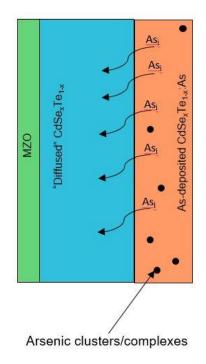

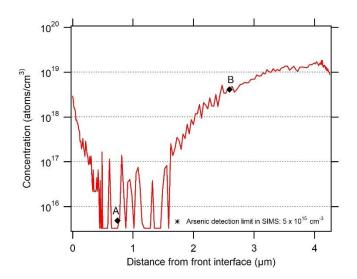

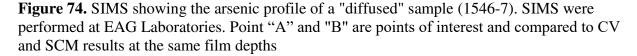

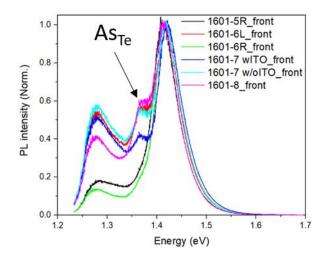

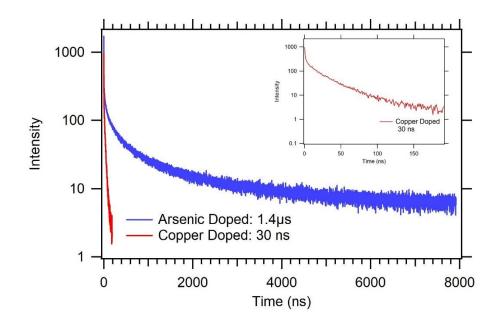

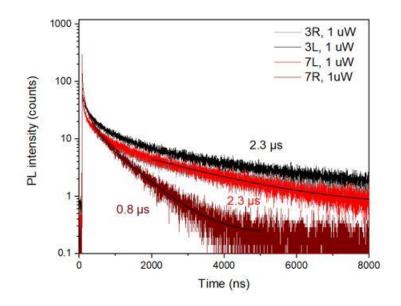

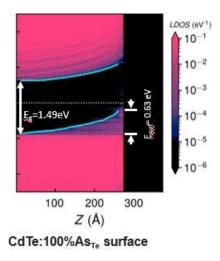

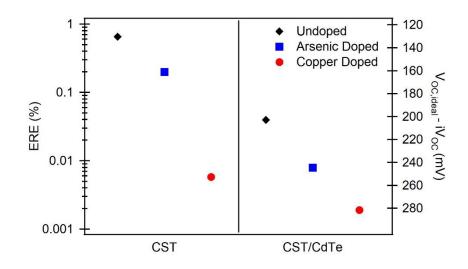

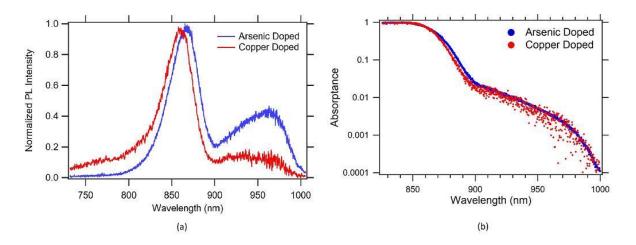

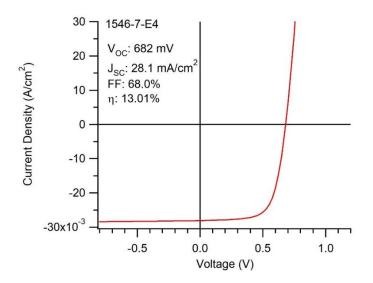

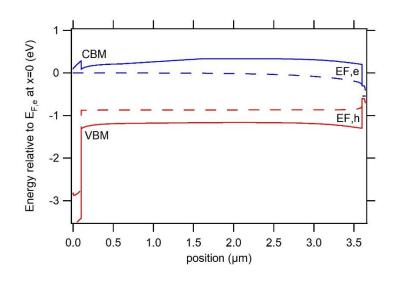

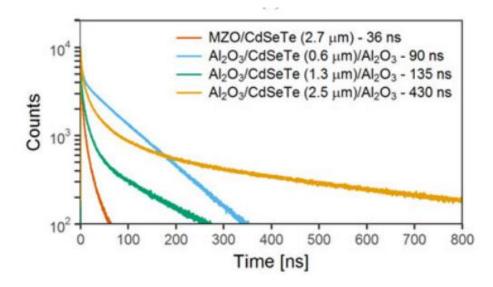

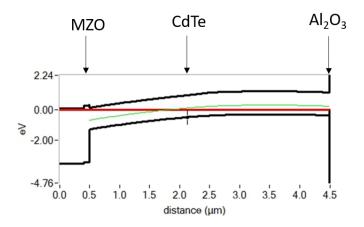

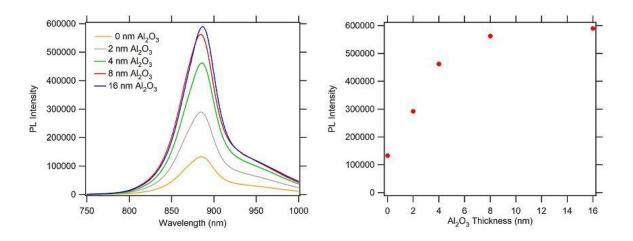

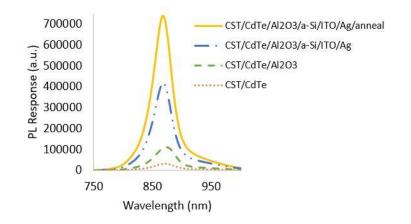

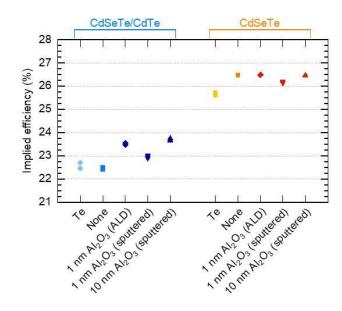

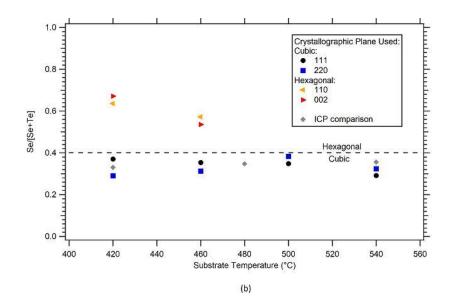

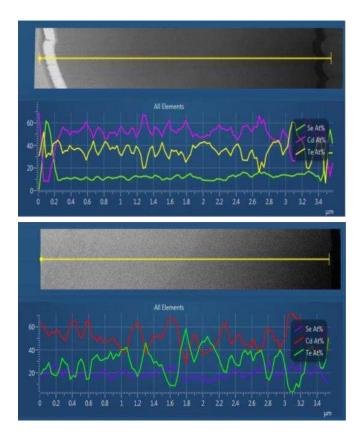

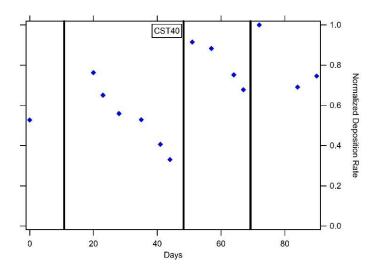

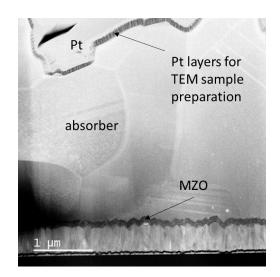

Figure 78. Side-by-side comparison of SIMS and CV results for a diffused-arsenic sample ... 105 Figure 79. Low Temperature CL spectrum of an As-doped device made at NREL...... 107 Figure 82. TRPL decay curves showing 2.3 µs lifetime for several diffused-arsenic devices .. 109 Figure 83. Upward band bending shown in the band diagram of CdTe with As<sub>Te</sub> at the back. 112 Figure 84. ERE measurement for undoped/arsenic/copper-doped CdSeTe and CdSeTe/CdTe 114 Figure 85. (a) Sub bandgap features in copper and diffused-arsenic (b) Absorptance extracted by Figure 89. Band alignment of the CdTe/Te interface showing non-ideal hole selectivity ...... 120 Figure 90. Band Bending Induced by Differing Work Functions with n-type semiconductors 123 Figure 91. Band bending induced in a semiconductor by a lower/higher work function metal 124 Figure 92. Upward Band Bending induced by p-type Doping, from CSU's photovoltaic lab.. 125 Figure 98 (a) PL spectra of CdSeTe/CdTe devices (1537) with increasingly thick layers of Figure 100. (a) TRPL decays for CdSeTe films with either no back contact, a tellurium back Figure 106. Structures/TRPL Lifetime for Devices with Diffused-Arsenic Doping/Al<sub>2</sub>O<sub>3</sub>..... 143 Figure 109. Voltage loss analysis for CdSeTe samples with various dopants & back contacts 148 Figure 110. Voltage Deficit vs ERE for Various Technologies with recent CdTe progress ..... 149 Figure 111. (a) XPS spectra for As-deposited CdSeTe films. (b) Plot showing the increase in oxidized tellurium fraction after aging for both as-deposited and CdCl2-treated CdSeTe ...... 150 Figure 112. Plot showing the increase in ERE as a function of oxidized tellurium fraction..... 151 Figure 113. Example of a zero short-circuit current device with a CdSeTe absorber ...... 154

| <b>Figure</b> 1 | <b>114.</b> Scanning Kelvin Probe Microscopy measurement of a CdSeTe-only device 1                             | 58 |

|-----------------|----------------------------------------------------------------------------------------------------------------|----|

| <b>Figure</b>   | 115. XRD measurements of as-deposited CdSe <sub>0.4</sub> Te <sub>0.6</sub> 1                                  | 61 |

| <b>Figure</b>   | 116. EDS linescans comparing two devices, Sample 1546-7 and Sample 1633-4 1                                    | 62 |

| Figure          | <b>117</b> . The normalized deposition rate of CdSeTe over several months                                      | 63 |

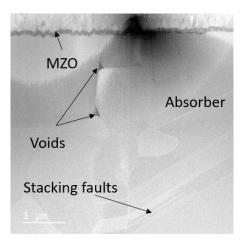

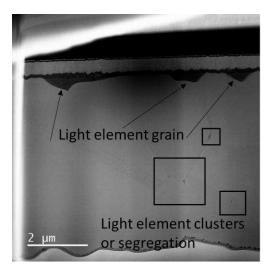

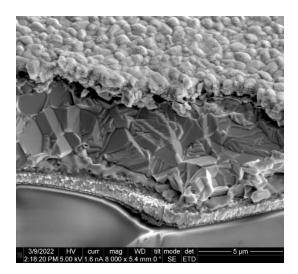

| <b>Figure</b>   | <b>118.</b> TEM image showing large grained microstructure in an arsenic-doped device 1                        | 64 |

| Figure          | <b>119.</b> TEM image showing an arsenic-doped film with voids and stacking faults 1                           | 65 |

| <b>Figure</b>   | 120. TEM image showing the segregation of chlorine in voids and at the interface 1                             | 66 |

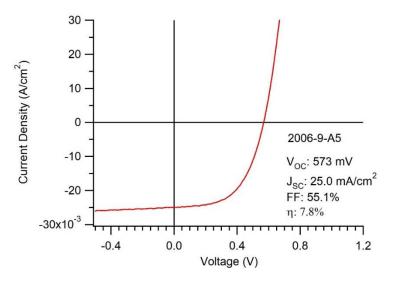

| <b>Figure</b>   | <b>121.</b> JV plot of a CdSeTe/ZnTe device exhibiting 25 mA/cm <sup>2</sup> current density                   | 67 |

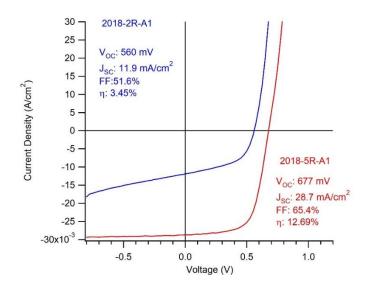

| Figure          | 122. JV plots of CdSeTe-only devices showing the effects of a 1800s Cd <sub>3</sub> As <sub>2</sub> anneal . 1 | 69 |

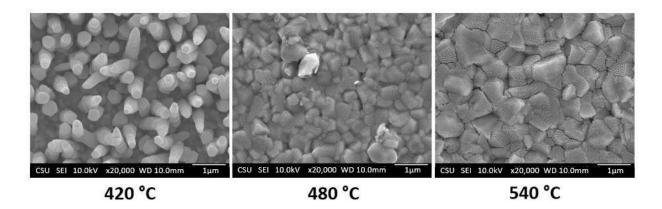

| <b>Figure</b>   | 123. SEM images of as-deposited CdSeTe 1                                                                       | 76 |

| <b>Figure</b>   | 124. Cross-sectional SEM image showing large dense grains of CdSeTe 1                                          | 77 |

|                 |                                                                                                                |    |

## LIST OF NOMENCLATURE

| AM                        | Air Mass                                     |

|---------------------------|----------------------------------------------|

| a-Si:H                    | Hydrogenated amorphous silicon               |

| BOS                       | Balance of System                            |

| BSF                       | Back-Surface Field                           |

| c-Si                      | Crystalline Silicon                          |

| CdTe                      | Cadmium Telluride                            |

| CdSeTe                    | Cadmium Selenium Telluride                   |

| CIGS                      | Copper Indium Gallium Selenide               |

| CF                        | Capacitance vs Frequency                     |

| CL                        | Cathodoluminescence                          |

| CV                        | Capacitance vs Voltage                       |

| $CO_2$                    | Carbon Dioxide                               |

| CSS                       | Close Space Sublimation                      |

| CSU                       | Colorado State University                    |

| EDS                       | Energy Dispersive X-Ray Spectrometry         |

| $\mathrm{E}_{\mathrm{g}}$ | Band Gap                                     |

| Ec                        | Conduction Band                              |

| Ev                        | Valence Band                                 |

| e-h                       | Electron-Hole Pair                           |

| eV                        | Electron-Volt                                |

| ERE                       | External Radiative Efficiency                |

| FF                        | Fill-factor                                  |

| FWHM                      | Full Width at Half Maximum                   |

| GaAs                      | Gallium Arsenide                             |

| GAXRD                     | Glancing Angle XRD                           |

| GDP                       | Gross Domestic Product                       |

| GHG                       | Greenhouse Gasses                            |

| GW                        | Gigawatt                                     |

| I <sub>mp</sub>           | Current at max power point                   |

| I <sub>sc</sub>           | Short-circuit Current                        |

| ICP-MS                    | Inductively-Coupled Plasma Mass Spectrometry |

| ITO                       | Indium-Tin Oxide                             |

| iV <sub>OC</sub>          | Implied Open-Circuit Voltage                 |

| $J_{sc}$                  | Short-circuit Current Density                |

| JV                        | Current Density vs Voltage                   |

| K                         | Degrees kelvin                               |

| kWh                       | kilowatt-hour                                |

| LCOE                      | Levelized Cost of Energy                     |

| MBE                       | Molecular Beam Epitaxy                       |

| MOCVD                     | Metal-Organic Chemical Vapor Deposition      |

| MTOE             | Million Tonnes of Oil Equivalent                    |

|------------------|-----------------------------------------------------|

| MZO              | Mg <sub>x</sub> Zn <sub>1-x</sub> O                 |

| NREL             | National Renewable Energy Laboratory                |

| PL               | Photoluminescence                                   |

| ppm              | Parts Per Million                                   |

| PTAA             | Poly[bis(4-phenyl)(2,4,6-trimethylphenyl)amine]     |

| P <sub>T</sub>   | Theoretical power of a perfect diode                |

| PV               | Photovoltaic                                        |

| QE               | Quantum Efficiency                                  |

| qFL              | Quasi-Fermi Level                                   |

| qFLS             | Quasi-Fermi Level Splitting                         |

| S                | Interface Recombination Velocity (cm/s)             |

| SCP              | Scanning Capacitance Microscopy                     |

| SEM              | Scanning Electron Microscope                        |

| Si               | Silicon                                             |

| SIMS             | Secondary Ion Mass Spectrometry                     |

| SRH              | Shockley-Reed-Hall Recombination                    |

| TCO              | Transparent Conducting Oxide                        |

| TOPCon           | Tunnel Oxide Passivated Carrier- Selective Contacts |

| TRPL             | Time-Resolved Photoluminescence                     |

| TWyr             | Terawatt-year                                       |

| V <sub>Cd</sub>  | Cadmium Vacancy                                     |

| Voc              | Open-circuit Voltage                                |

| V <sub>mp</sub>  | Maximum power point/voltage                         |

| VTD              | Vapor Transport Deposition                          |

| XPS              | X-ray Photoelectron Spectroscopy                    |

| XRD              | X-Ray Diffraction                                   |

| η                | Photovoltaic conversion efficiency                  |

| τ <sub>eff</sub> | Effective Carrier Lifetime                          |

| $	au_{b}$        | Bulk Carrier Lifetime                               |

| $	au_{s}$        | Surface Carrier Lifetime                            |

| 6N               | "6 Nine Pure" indicating 99.9999% purity            |

|                  |                                                     |

#### **CHAPTER 1.** INTRODUCTION

#### **1.1** What are Photovoltaics?

Since the discovery of the photovoltaic effect in 1839, photovoltaics (PV) have gone from a scientific curiosity, to a niche technology used only for space and distributed power systems, to a large-scale source of world energy today. Photovoltaics is the conversion of sunlight directly into electricity. The most common method of producing electricity via photovoltaics today is done with solar cells fabricated from semiconducting materials. These special materials produce an electrical voltage and current when exposed to light— a phenomenon which is the result of several subsequent energy conversion processes. Thermal radiation is converted to chemical energy within the absorber when a photon of light interacts with matter, exciting an electron to an elevated energy band and the energy is converted from chemical to electrical by the extraction of a flow of electrons from the material while under illumination. Semiconductors have unique material properties which make them particularly well-suited to the absorption and harnessing of energy from sunlight.

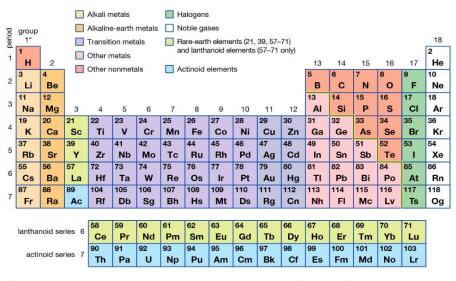

Semiconductor elements are found within a relatively narrow band of the periodic table of elements, in groups two through six (groups twelve through sixteen using the European convention.) Of these semiconductors, silicon (Si) is by far the most commonly used for photovoltaics. This is due to its abundant availability in the Earth's crust, its long history of use in electrical devices, and the fact that it is an elemental semiconductor. Other semiconductor materials consist of two or more elements. Known as compound semiconductors, these materials include pairings of elements that have an average of four valence electrons, such as II–VI or III–V semiconductors. Common semiconductors used in photovoltaic applications are Copper

1

Indium Gallium Selenide (CIGS), Gallium Arsenide (GaAs), and notably, Cadmium Telluride (CdTe), the material used in this work. These elements and their position in the periodic table of the elements can be seen in Figure 1 below.

\*Numbering system adopted by the International Union of Pure and Applied Chemistry (IUPAC). © Encyclopædia Britannica, Inc.

### Figure 1. Periodic table of the elements. Adopted from [1]

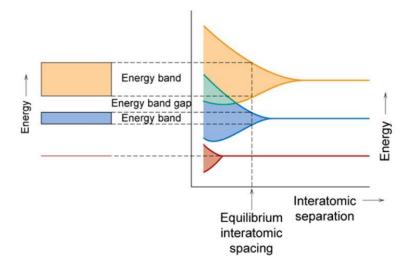

One of the key material parameters for any semiconductor used for PV applications is that of the bandgap ( $E_g$ .) Electrons in a single atom orbit around the nucleus in orbitals that reside at specific, quantized energies. As atoms move closer to one another however, the electrons in the outer shells begin to interact with one another, altering the energy levels of the electrons. The result is that the allowable energy states begin to spread in broad "bands" of allowable energies, as seen in Figure 2. The lower band of allowable energies is known as the valence band ( $E_v$ ) which corresponds with the energy of electrons that are bound to their host atoms. The upper band is the conduction band ( $E_c$ ) which corresponds with the energy levels of free electrons that are not bound to a particular atom and are free to move. Between these two energy bands there is a gap of forbidden energies, known as the bandgap. Without defects in the semiconductor, no electron can reside in a state with energy within this bandgap.

**Figure 2:** Energy band diagram showing energy states spread into bands as the interatomic distance decreases

Because no state can exist within the bandgap,  $E_g$  corresponds with the minimum energy required to excite an electron from the valence band up into the conduction band. If a photon of light has energy equal to or exceeding  $E_g$ , it may be absorbed and has sufficient energy to excite the electron into the conduction band, leaving behind a vacancy in the valence band. Rather than visualize a lack of electrons in the valence band, the common convention is to instead designate the absence of an electron as a "hole". This is analogous to visualizing a bubble moving through a liquid, although the liquid is actually moving, it is more convenient to describe the motion of the bubble [4]. This is the generation of an electron-hole pair (e-h.) Photons with energies less than the bandgap do not have enough energy to break the bond and thus do no interact with the electrons and largely pass through the material as if it were transparent. Importantly, the bandgap fundamentally affects how light of different energies interacts with the material. Within the bandgap of a semiconductor is the Fermi level. At temperatures above 0 K, the Fermi level is a statistical construct that represents the energy at which there is a 50% probability of finding a charge carrier when a Fermi-Dirac distribution is plotted. It does not necessarily mean that a charge carrier will be found at that energy level, considering its location within the bandgap.

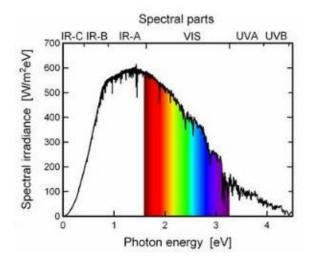

The light spectrum that reaches earth from the sun consists of an entire range of photon energies. As seen in Figure 3, this spectrum consists of photons with energies ranging from roughly zero to four electron volts (eV). The distribution of these photons is non-uniform and approximately matches the spectrum of a blackbody radiating at 5800 K. The result is that not all photons of light have enough energy to create an e-h pair and be absorbed into the semiconductor. The lower the bandgap of a material, the larger proportion of the spectrum that will have enough energy to be absorbed. However, if a photon with energy greater than the bandgap is absorbed, the electron is excited far above the conduction band minimum. Within the conduction band there are many allowable states, and thus the electron rapidly loses energy via phonons as it collides with the lattice over a time scale of  $10^{-12}$  s and thermalizes down to the conduction band minimum. Thus light-generated e-h pairs will only have energy equal to the bandgap, so any photons with energies greater than  $E_g$  will have the excess energy wasted as heat.

Figure 3. Extraterrestrial (AM0) solar spectrum, Adopted from [3]

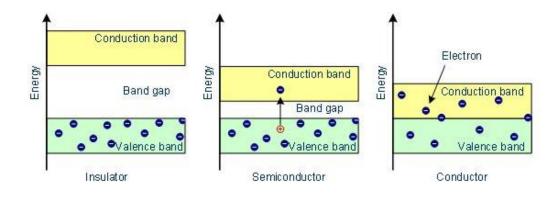

Insulators have very large bandgaps, meaning that any e-h pairs that are generated will have a large amount of energy (sufficient to jump the band gap.) However, very few photons in the solar spectrum are energetic enough to create an e-h pair in this material. At the other extreme, metals do not have a defined bandgap of forbidden energies, but instead have many allowable states in their valence and conduction bands that overlap. This allows many photons of many energies to be absorbed, but without a gap between the two bands, an excited electron can easily decay to a lower energy state, transferring or losing its energy. Semiconductors have a moderately sized band gap, which strikes an important balance between there being a large proportion of the solar spectrum with enough energy to excite an electron, and those excited e-h pairs having a large amount of energy and separation so that that energy may be extracted. Figure 4 shows the band diagrams for these different material types.

Figure 4. Bandgaps of various materials, adopted from [4]

The band structure of these materials also dictate their electrical conductivities. Due to the large bandgap of insulators, the conduction band is largely empty, and without sufficient electrons free to move, they exhibit poor conductivity. Alternatively, metals typically exhibit high conductivity because their overlapping bands allows for a cloud of unbound electrons free to conduct electrical charge. Semiconductors typically have an electrical conductivity that falls between the ranges of pure conductors and insulators. Semiconductors also have the unique property that their electrical conductivity can be greatly modified by adding trace amounts of impurities in a process known as "doping". These unique properties are derived from a specific atomic structure where the pure semiconductor bonds to create full valence shells of eight electrons, but the addition of impurities changes the number of valence electrons and thus changes the electrical conductivity of the substance.

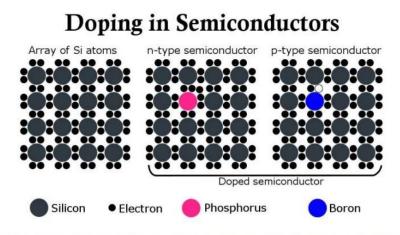

Semiconductors can be doped either n-type or p-type, depending on the impurity element that is added. N-type doping increases the number of electrons (negative charge) present in the lattice, and thus increases the electron conductivity of the semiconductor. P-type doping results in fewer electrons than the intrinsic semiconductor (positive charge) and similarly increases hole

6

conductivity. Figure 5 shows a diagram of doping in silicon where the presence of a phosphorus or boron atom dope silicon n-type or p-type, respectively.

Left: Pure silicon atoms. Center: Silicon doped with Phosphorus, resulting in an additional electron. Right: Silicon doped with Boron, resulting in an additional hole.

Figure 5. N and P-type doping in semiconductors, adopted from [5]

#### **1.2** Conversion of Thermal Radiation into Chemical Energy

We have established that when a photon of sufficient energy is absorbed in a semiconductor, it generates an energetically separated set of charge carriers. An electron is excited into the conduction band, leaving behind a hole in the valence band. Under constant illumination, many e-h pairs are generated. Once a photon of light has been absorbed, an electron only remains in its excited state for a finite amount of time before it loses its energy and falls back into the valence band. This is known as "recombination" as an electron and a hole recombine and mutually annihilate. This recombination may occur through several, parallel processes. The most preferable method is known as radiative recombination. In this process, the electron spontaneously transitions to an unoccupied state in the valence band, losing its energy in a single step, emitting a photon of light with energy equal to bandgap. This process is thermodynamically unavoidable, but because the energy transition must occur in a single radiative step, it is the slowest recombination processes and puts an upper bound on how long an excited e-h pair may survive, known as the "lifetime" [6], [7]. Since radiative recombination requires that electrons and holes interact directly with each other, the rate of radiative recombination increases as the concentration of electrons and holes increases. Finally this is the only recombination process which is reversible, with no entropy generation.

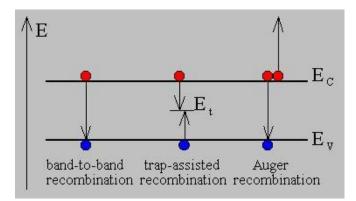

In a perfect semiconductor with no defects, the bandgap, by definition, is completely devoid of allowable energy states. In this case, radiative recombination is the only mechanism by which electrons may lose their energy. However, real materials have impurities and defects in the lattice which create states within the bandgap that facilitate the loss of energy over several steps. Known as Shockley-Read-Hall (SRH) or defect-assisted recombination, this occurs when both electrons and holes lose energy in small steps. The small energy steps may be lost to the lattice via individual phonons where it is dissipated as heat, thus no photon is emitted and this recombination is non-radiative. Additionally, because the non-radiative transition of an electron from the conduction band to the valence band via many intermediate steps requires small energy transitions — phonons typically disperse 30-50 meV — it may occur much more easily and over much shorter timescales than radiative recombination [8]. In most real materials, non-radiative recombination is the dominant mechanism and severely limits the charge carrier lifetime. One of the key objectives of solar cell design is to minimize non-radiative recombination. Non-radiative recombination may occur within the bulk of the material and at interfaces between adjoining layers, and multiple strategies may be employed to minimize it, as will be discussed later in this text. Figure 6 shows band diagrams for several prominent recombination methods. In this figure "trap-assisted recombination" is synonymous with SRH recombination. Auger recombination,

8

which is a non-radiative process which can become important in highly-doped direct bandgap materials [9] is a process where that includes the combination of an electron and a hole accompanied by energy transfer to another free carrier.

Figure 6. Band diagrams for various recombination methods, adopted from [10]

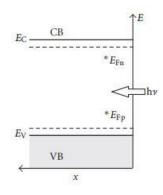

As previously discussed, the Fermi-level is a probabilistic construct which describes the energy at which there is a 50% chance of locating an electron. In semiconductors, the Fermi-level typically resides within the bandgap and an electron is therefore unlikely to actually reside at this energy. Under equilibrium conditions only one Fermi-level is allowed since only one of the bands will have any appreciable population of carriers. However, when under illumination, many e-h pairs are generated and two Fermi distributions exist— one for each band in which only one of the types of charge carrier (electron or hole) is considered. These are known as quasi-Fermi-levels (qFL.) These qFLs represent the electro-chemical potentials of electrons and holes respectively. The separation of these quasi-Fermi levels is known as quasi-Fermi-level-splitting (qFLS) and signifies the electrochemical potential available which could be extracted — known as the internal or implied voltage (iV<sub>OC</sub>). Increasing the population of electrons and/or holes moves their qFL closer to their respective bands. Therefore, increasing generation,

increasing equilibrium carrier concentrations through effective doping, minimizing non-radiative recombination in the bulk and at the interfaces, and maximizing charge carrier lifetimes all result in increased qFLS. Because the  $iV_{OC}$  indicates the upper limit to the voltage that a particular absorber can produce, maximizing the qFLS within the absorber is a vital first step to producing highly efficient solar cells. A visualization of the quasi-Fermi levels may be seen in Figure 7.

Figure 7. Quasi-Fermi levels in an absorber under illumination, adopted from [11]

#### **1.3** Conversion of Chemical Energy into Electrical Energy

Up to this point, we have discussed how energy from thermal radiation has been converted into chemical energy inside the semiconductor through the absorption of photons to excite electrons to higher energy states. However, in order to utilize this energy, it must be extracted as an electrical current flowing through an external circuit with a voltage difference between the electron and hole terminals. This is accomplished by driving electrons and holes out of the absorber through opposite contacts to create a net flow of charge. Electrons have numerous forces which may act on them, but the most pertinent for this discussion are an electric field (gradient in the electric potential) acting on its charge, and a diffusional force (gradient in the chemical potential) acting on its quantity. These "field" and "diffusion" currents are often

discussed as if they were separate entities, as if certain electrons only "felt" the field effect and contributed only to the field current while others only "felt" the diffusional force and contributed to the diffusion current. It is important to understand that while mathematically these currents can be calculated separately and then combined, in reality the movement of charge carriers within the absorber is influenced by the combination of these forces. It is at this point the concept of a quasi-Fermi level becomes extremely helpful, as the qFL is a representation of the electrochemical potential. Therefore, *the charge current is driven by a gradient in the quasi-Fermi level* according to Equation 1 where  $j_Q$  is the charge current density,  $\sigma_e$  and  $\sigma_h$  are the conductivity of electrons and holes respectively, e is the elementary charge, and  $\varepsilon_{FC}$  and  $\varepsilon_{FV}$  are the quasi-Fermi level energies for electrons and holes respectively.

$$j_Q = \frac{\sigma_e}{e} grad\varepsilon_{FC} + \frac{\sigma_h}{e} grad\varepsilon_{FV}$$

(1)

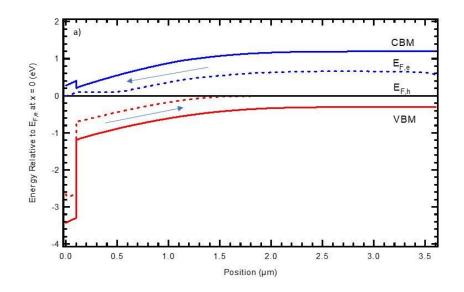

An important implication of equation 1 is that it is true whether an electric field, or a concentration gradient, or both exist. This means that a charge current can flow in the absence of one of these forces, as long as the other is present, or it can flow as the result of the combination of them. Alternatively, there is no charge current when there is no gradient in the quasi-Fermi level. This can best be illustrated by the band diagrams shown in Figure 8 and Figure 9. Figure 8 shows the band diagram of a CdSeTe device operating in the short circuit condition. The dashed lines represent the quasi-Fermi levels for electrons (blue) and for holes (red). The gradients which can be seen in these quasi-Fermi levels indicate that a net force will drive electrons "downhill" for electrons and "uphill" for holes. This drives electrons towards the left of the diagram, the electron contact, and holes towards the right, the hole contact, creating a net flow of carriers out of the device. Under short circuit conditions, with no external resistance to the flow

of electrons and holes, the charge carrier densities within the film are reduced by the extraction of current and the qFLs is minimized. At  $J_{SC}$ , there is no difference between the electrochemical potential of electrons at the electron contact and the holes at the hole contact (note the horizontal black line) thus there is no voltage across the device and no work may be performed, despite the flow of current.

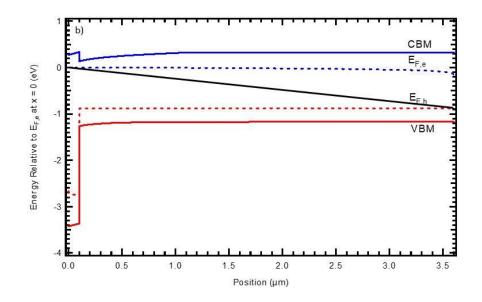

Figure 8. Band diagram of CdSeTe at J<sub>sc</sub>, modelling and figure by Carey Reich

Figure 9 illustrates the same CdSeTe device under open-circuit conditions. At opencircuit the quasi-Fermi levels are flat, an indication that there is no net flow of current. Without current extraction, the populations of electrons and holes, and thus the qFLS is maximized. In this configuration, the electrochemical potentials of the electrons and holes at their respective contacts are not equal, in fact the difference is maximized, this is the V<sub>OC</sub>. Note that in Figure 9, the black line is no longer horizontal, but connects two points of differing electrochemical potential. This is useful for visualizing the voltage across the device. Maximum power is extracted from a photovoltaic device at a point between the short and open circuit conditions where the voltage is maximized without sacrificing current flow. This max power point will be discussed in more depth shortly.

Figure 9. Band diagram of CdSeTe at Voc, modelling and figure by Carey Reich

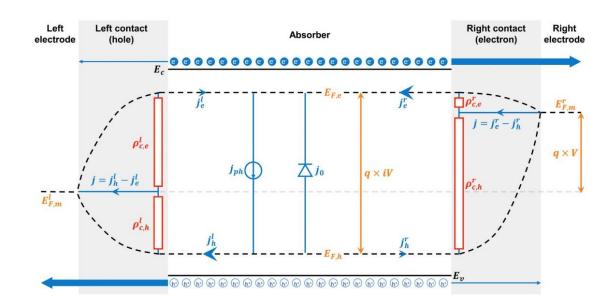

#### **1.3.1** Charge carrier selectivity and selecting appropriate electron and hole contacts

It has now been established that the gradient of the qFL is the driving force for the motion of charge carriers. However, the magnitude of the flow down a given gradient is still determined by the material's conductivity/resistivity to either electrons or holes. An excellent contact therefore will exhibit extremely high conductivity to one charge carrier while exhibiting extremely low conductivity to the other. The ratio of partial resistances to electrons and holes is known as the selectivity of the contact. Figure 10 illustrates this. The left (hole) contact exhibits poor selectivity, as seen by the size of red rectangles being only slightly unequal. As a result, the quasi-Fermi levels of electrons and holes both converge toward the center of the bandgap at the left of the diagram. Alternatively, the right (electron) contact exhibits excellent electron selectivity. The resistivity to electrons (inverse of conductivity) is extremely small compared to

that of holes. As a result, there is only a small drop in the electron qFL at the right, while the hole qFL drastically falls due to the fact that only a very few holes are able to traverse the contact. The voltage that this device would produce is annotated in Figure 10 as "q x V" and is the difference between the electro-chemical potentials of the carriers at the contacts. This voltage is less than maximum qFLs seen in the absorber (the implied voltage) and is a direct result of voltage drop across the contact, known as selectivity losses [12]. A theoretically perfect contact would exhibit infinite resistance to one carrier, completely blocking it, and the quasi-Fermi level would show no drop across the contact. Because perfect contacts don't exist in reality, choosing/engineering materials with the proper energetic alignment and high selectivity are the primary criteria when designing a contact. The conductivity of a material to a charge carrier is the product of that carrier density and the charge carrier mobility. While the latter is considered to be a material property and not particularly mutable, the carrier density may be increased by the doping methods discussed previously.

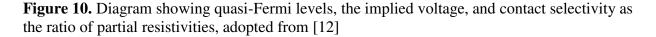

#### **1.3.2** P-N Junctions

Traditional PV device structures achieved asymmetrical carrier conductivities and selectivity through the use of a p-n junction. A p-n junction is formed when two semiconductors, one doped n-type and one doped p-type are fused together. The n-type material has a large number of free electrons, and the p-type has a large number of holes. When these materials are joined, a large density gradient is formed between the two sides of the junction. The result is that some of the electrons will begin to diffuse towards the P side of the junction. When the electrons diffuse, they leave behind positively charged ion cores which are fixed in the crystal lattice right at the junction. Similarly, holes will diffuse towards the N side, leaving behind negatively charged ion cores. Figure 11 illustrates the resulting configuration. The ion cores that are left behind create an electric field between them which opposes the diffusion of electrons and holes. The electrons and holes continue to diffuse until this electric field is strong enough to repel any additional charge carriers. This electric field is known as the built-in potential. The region formed within this electric field is known as the depletion region or depletion width because any charge carrier that diffuses into it is quickly repelled, and thus the region is virtually depleted of free carriers, compared to the material far from the junction.

P-N junctions were foundational to the first functioning solar cells, and are still the basis of many solar technologies today. However, we know that the electric field is not the only force which must be considered for carrier motion. Indeed, a functioning photovoltaic device may be constructed without a p-n junction or an electric field present [13]. Therefore viewing photovoltaics solely through the p-n framework forms an incomplete picture. P-N junctions are effective because they facilitate the separation of e-h pairs. Furthermore, the high concentration of only one carrier on each side of the junction inherently creates carrier-selectivity by creating a

15

high ratio of conductivities. State of the art solar cells incorporate well-engineered doping profiles and carefully selected contact materials to ensure that both diffusional and electrical forces work to maximize qFLs and carrier selectivity.

Figure 11. Diagram of a p-n junction, adopted from [14]

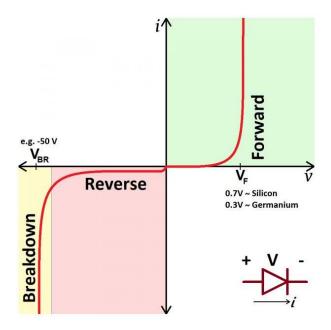

#### **1.4** Photovoltaics as Diodes

It has already been established that when a p-n junction is formed, electrons and holes diffuse, creating a depletion region at the junction with an electric field that opposes the flow of additional carriers. If the entire structure is subjected to a negative bias (where the n-side is biased positively and the p-side is biased negatively), electrons are attracted toward the positive electrode and away from the junction, at the same time, holes are attracted to the negative electrode and away from the junction. The lack of electrons and holes widens the depletion width, and because the depletion width is highly insulative due to the lack of free carriers, it acts similar to the dielectric layer within a parallel plate capacitor. When this dielectric layer widens, the barrier is increased, as is the amount of energy a carrier would need to move across the

depletion width. Alternatively, if the structure is subjected to a positive bias, the depletion width shrinks as the electrons and holes are pushed towards the junction. The external bias pushes the carriers, giving them energy to cross the depletion width. At a certain point, the barrier is sufficiently reduced and no longer prevents the flow of carriers. This creates what is known as a p-n junction diode, where an external bias can be used to either block or allow the flow of current. This diode only allows current to flow in one direction, and unlike with a resistor, the current does not vary linearly with voltage. Instead, the current-voltage curve exhibits exponential behavior according to Equation 2:

$$I = I_o \left[ e^{\frac{qV}{nkT}} - 1 \right] \tag{2}$$

Where I is the current,  $I_0$  is the dark saturation current, q is the elementary charge, V is the applied voltage, n is an ideality factor, k is the Boltzmann constant, and T is the absolute temperature. Figure 12 displays a typical diode IV curve that behaves according to the diode law expressed in Equation 2.

Figure 12. Typical diode IV curve, adopted from [15]

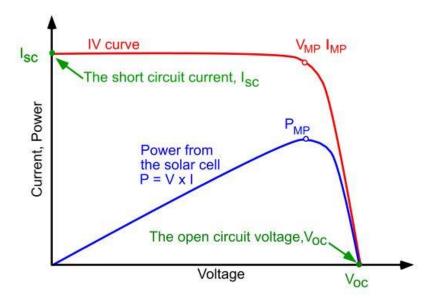

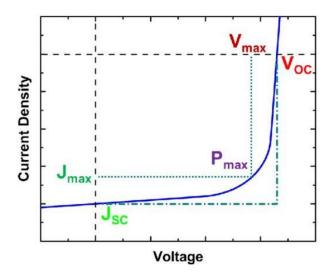

In order to appreciate a photovoltaic device operating as a diode, and the efficiency of photovoltaic energy conversion, it is first necessary to understand several parameters of the diode curve. When combined, these parameters are used to calculate the electrical power that is produced by a photovoltaic device. When the electrical power produced and the incident power of sunlight are both known, the photovoltaic conversion efficiency can be calculated. An e-h pair is generated when light with energy greater than or equal to the bandgap is incident upon the semiconductor. These carriers are known as light-generated carriers. Due to the electric field present at the junction, the electrons are swept to the N side while the holes are swept to the P side of the semiconductor. Under short-circuit conditions, there is no build-up of charge, as the carriers are allowed to leave the device without resistance and exit as light-generated current. This current is commonly known as Ise, the short-circuit current. When this current is divided by the device's physical area, the current density (Jsc) is the result. If the current is prevented from leaving the device, light-generated electrons and holes that are generated in the depletion width

are swept to the N and P sides of the junction, respectively, and the total number of electrons on the n-side and holes on the p-side increases. This separation of charges creates an electric field that is in opposition to the one existing inside the depletion width and has the effect of reducing the net field. As previously discussed, the depletion region electric field was acting as a barrier to carrier diffusion and when it decreases, carrier diffusion increases. At some point, the diffusion current is equal to the light-generated current, so that the net current is zero, known as opencircuit condition. The forward bias required to reach open-circuit conditions is known as the open-circuit voltage ( $V_{OC}$ ). Figure 13 shows a standard current density vs voltage (JV) curve with the I<sub>sc</sub> and V<sub>OC</sub> annotated.

Figure 13. JV curve showing key PV parameters, adopted from [16]

The electrical power produced by the solar device is simply the product of the current and the voltage. Looking at Figure 13, it can be seen that for most of the voltage range, the current is nearly constant. The very slight negative slope is due to the increase in diffusion current which is counteracting the light-generated current. Near  $V_{OC}$ , the current drops drastically, down to zero at the open circuit point. When the power is plotted, it becomes obvious that the maximum power produced from a solar cell is produced at a point just prior to open circuit voltage. While sweeping upward in voltage, this is the last point where the gains in voltage outweigh the loss in current in the power calculation. This is known as the maximum power point or voltage ( $V_{mp}$ ). A solar cell under illumination is operating under a forward light bias, and is ideally operating near the max power point. The final parameter is known as the fill factor (FF) and is related to the  $V_{mp}$ . In a perfect diode, the current would remain perfectly horizontal all the way up to the opencircuit voltage. At  $V_{OC}$ , the curve would make a sharp ninety-degree turn and point straight down. The area under the curve would be a perfect rectangle and the  $V_{mp}$  would equal the  $V_{OC}$ . Real diodes do not behave perfectly, and the JV curve has slope to it, and the "knee" of the curve is rounded. The fill-factor measures the "squareness" of the JV curve, and is a measure of the quality of the diode. FF can be calculated with:

$$FF = \frac{P_{max}}{P_T} = \frac{V_{mp}I_{mp}}{V_{oc}I_{sc}}$$

(3)

Where  $I_{mp}$  is the current at maximum power and  $P_T$  is the theoretical power of a perfect diode. With these three parameters, it is now possible to calculate the efficiency of photovoltaic conversion denoted with the Greek symbol eta ( $\eta$ ). Like most efficiencies,  $\eta$  is defined as power out divided by power in. In this instance, the input power is from the incident light. The efficiency can be calculated using the following equation:

$$\eta = \frac{V_{mp}I_{mp}}{P_{in}} = \frac{V_{oc}I_{sc}FF}{P_{in}} \tag{4}$$

# **1.5** Common Characterization Techniques

Although the photovoltaic conversion efficiency is an extremely important feature of a solar cell, as a single number, it does not explain why the value is what it is, or how it could be improved. Fortunately there are multiple optical and electrical characterization methods that provide useful insight into the performance of a PV device. Several common techniques are listed here because the results from these tests will be referred to extensively, but note that this is by no means an exhaustive list, and dozens of additional characterization methods exist in addition to those presented here.

# 1.5.1 Current Density vs Voltage

The current density vs voltage (JV) measurement is a simple test that reconstructs the diode curve of the solar cell in operation. A device of known area is mounted onto a testing apparatus with electrodes connected to the front and back contacts as shown in Figure 14. The device is then illuminated using a standardized light source at 1000W/m<sup>2</sup> with an AM1.5 spectrum at 25°C [17]. While illuminated, the short-circuit current for the device is measured. The bias across the contacts is slowly swept across the range from short-circuit to open circuit, with current measurements taken at set intervals. Once complete, The V<sub>OC</sub>, J<sub>sc</sub>, and FF, are all known, and since the input power is also known, the conversion efficiency can be calculated using Equation 4. In addition to these values, the series and shunt resistances of the device can be calculated using the slopes of the curve, as shown in Figure 15.

Figure 14. CdTe substrate in CSU's JV tester

**Figure 15.** Diagram illustrating the effects of changing series & shunt resistance, adopted from [18]

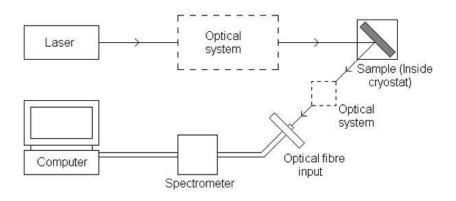

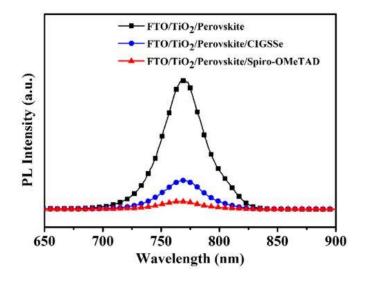

**1.5.2** Steady-State Photoluminescence and Cathodoluminescence

Steady-state photoluminescence is a method designed to indirectly gauge the presence of defects by measuring the amount the radiative vs. non-radiative recombination. To perform the

measurement, the sample to be tested is loaded onto a stage where it can be illuminated. A light source, commonly a laser with photon energy greater than the bandgap of the sample is steadily shone on the sample. Photons emitted from the sample are detected by a spectrometer and the spectrum is recorded. A series of short and long-pass filters are used to ensure that the excitation laser light is not included in the measurement. A sample setup is shown in Figure 16 and a diagram showing several radiative transitions as well as non-radiative recombination is shown in Figure 17 below. The resulting spectrum is a nearly Gaussian distribution centered on the bandgap energy of the sample, similar to those shown in Figure 18. Additional peaks may be present, usually associated with a shallow defect that cause longer wavelength photon emission. A common interpretation of this characterization method is that for a steady-state light input, as the number of defects and non-radiative recombination sites decrease, the proportion of radiative recombination will increase, and the PL peak height will increase. The total photoluminescence of a sample, determined by the integrated PL spectra, is closely related to the External Radiative Efficiency (ERE), a concept that will be discussed momentarily. Cathodoluminescence (CL) is performed similarly to PL, with the exception that electrons are used to excite the emission of photons, rather than light.

Figure 16. Experimental setup for measuring steady-state photoluminescence, adapted from [19]

Figure 17. Diagram of radiative and non-radiative recombination, adapted from [20]

Figure 18. Steady-state PL spectra, adopted from [21]

# **1.5.3** External Radiative Efficiency

External Radiative Efficiency (ERE) measurements have only recently been adopted and reported by the CdTe community as a method of evaluating the potential of device structures to produce increased voltage [22], [23]. The ERE is the ratio of photons that are emitted through the illuminated surface to the number of incident photons when a photovoltaic sample is illuminated. It is a measure of the number of recombination events which are radiative, and because non-radiative recombination reduces the quasi-Fermi level splitting, ERE is crucial for determining the true maximum voltage possible from an absorber. The quasi-Fermi level splitting may be

described by the implied voltage ( $iV_{OC}=qFLS/q$  with q the elementary charge); the voltage which a photovoltaic absorber is capable of producing with perfectly selective contacts [24]. A photovoltaic device can never extract a voltage greater than that represented by the potential difference between the electron and hole quasi-fermi levels. Because quasi-fermi level splitting is improved by increasing bulk minority-carrier lifetime, increasing doping, and decreasing grain boundary and interface recombination, it is a powerful tool for not only indirect measurement of these other parameters, but can also quantify the impact that changing these parameters has on the device's potential to produce a greater open-circuit voltage. Figure 19 illustrates the experimental setup for ERE measurements presented in this work.

**Figure 19.** Experimental setup for measuring external radiative efficiency (ERE), figure by Arthur Onno

The ERE contributes to the implied voltage according to Equation 5, where  $V_{OC,rad}$  is the radiative recombination limited voltage, about 1150 mV in CdTe [25],  $k_b$  is the Boltzmann constant, T is the absolute temperature, and q is the elementary charge. Most PV technologies currently exhibit very low ERE values, far below 1%. CdTe, for example, had previously been reported with an ERE of 0.0001% [26].

$$iV_{OC} = V_{OC,rad} - \frac{k_b T}{q} |\ln(ERE)|$$

(5)

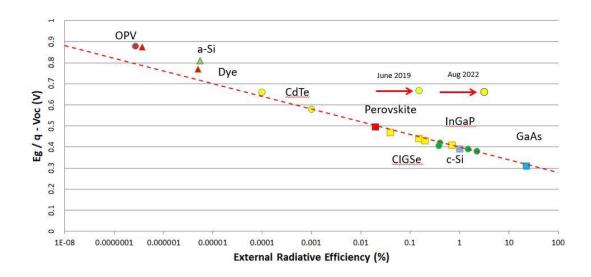

Finally, a general trend has been observed, that as ERE and  $iV_{OC}$  increase, regardless of technology, the voltage deficit generally decreases. Figure 20 shows the ERE and voltage deficit values for many technologies, and the resulting trend line that shows the beneficial effect of improving the ERE. Two definitions for voltage deficit exist: either the difference between the radiative recombination limited voltage and the open circuit voltage, or difference between the bandgap divided the elementary charge and the open circuit voltage, as in Figure 20.

**Figure 20.** Voltage deficit vs external radiative efficiencies for various photovoltaic technologies, adapted from [27]

# **1.5.4** Time-Resolved Photoluminescence

Although the information gleaned from steady-state photoluminescence is extremely valuable for understanding defects and sources of recombination, there is some information that is not available from spectral data alone. The minority-carrier lifetime of photovoltaic devices can be measured through the use of Time-Resolved Photoluminescence (TRPL.) During a TRPL

measurement, a sample is mounted inside a sample holder that has optics to deliver laser light to the sample, and to capture emitted light and transfer it to a detector. A femtosecond laser generates pulses of light that strike the sample. For single-photon TRPL, an optical parametric amplifier is used to ensure that the wavelength of laser light is adjusted so the photon energy is greater than the bandgap of the material in the sample. The laser light strikes the sample, where e-h pairs are generated. A fraction of these carriers radiatively recombine and photoluminescence occurs.