## DISSERTATION

# RESOURCE MANAGEMENT FOR EXTREME SCALE HIGH PERFORMANCE COMPUTING SYSTEMS IN THE PRESENCE OF FAILURES

Submitted by

Daniel Dauwe Department of Electrical and Computer Engineering

> In partial fulfillment of the requirements For the Degree of Doctor of Philosophy Colorado State University Fort Collins, Colorado Summer 2018

**Doctoral Committee:**

Advisor: Sudeep Pasricha Co-Advisor: H. J. Siegel

Anthony A. Maciejewski Patrick J. Burns Copyright by Daniel Dauwe 2018

All Rights Reserved

#### ABSTRACT

# RESOURCE MANAGEMENT FOR EXTREME SCALE HIGH PERFORMANCE COMPUTING SYSTEMS IN THE PRESENCE OF FAILURES

High performance computing (HPC) systems, such as data centers and supercomputers, coordinate the execution of large-scale computation of applications over tens or hundreds of thousands of multicore processors. Unfortunately, as the size of HPC systems continues to grow towards exascale complexities, these systems experience an exponential growth in the number of failures occurring in the system. These failures reduce performance and increase energy use, reducing the efficiency and effectiveness of emerging extreme-scale HPC systems. Applications executing in parallel on individual multicore processors also suffer from decreased performance and increased energy use as a result of applications being forced to share resources, in particular, the contention from multiple application threads sharing the last-level cache causes performance degradation. These challenges make it increasingly important to characterize and optimize the performance and behavior of applications that execute in these systems.

To address these challenges, in this dissertation we propose a framework for intelligently characterizing and managing extreme-scale HPC system resources. We devise various techniques to mitigate the negative effects of failures and resource contention in HPC systems. In particular, we develop new HPC resource management techniques for intelligently utilizing system resources through the (a) optimal scheduling of applications to HPC nodes and (b) the optimal configuration of fault resilience protocols. These resource management techniques employ information obtained from historical analysis as well as theoretical and machine learning methods for predictions. We use these data to characterize system performance, energy use, and application behavior when operating under the uncertainty of performance degradation from both system failures and resource contention. We investigate how to better characterize and model the negative effects from system failures as well as application co-location on large-scale HPC computing systems. Our analysis of application and system behavior also investigates: the interrelated effects of network usage of applications and fault resilience protocols; checkpoint interval selection and its sensitivity to system parameters for various checkpoint-based fault resilience protocols; and performance comparisons of various promising strategies for fault resilience in exascale-sized systems.

#### ACKNOWLEDGEMENTS

I am in debt to my academic committee, Dr. Sudeep Pasricha, Dr. H.J. Siegel, Dr. Tony Maciejewski, and Dr. Patrick Burns. I would like to express my deepest gratitude to my advisors Dr. Sudeep Pasricha and Dr. H.J. Siegel, and my committee member Dr. Tony Maciejewski for their support and guidance throughout my research and time spent at Colorado State University and for providing me with invaluable insight and assistance to help co-author much of the research in this dissertation. I would like to give a special thanks to Dr. Pasricha for allowing me the freedom to broadly explore the areas of HPC in which I am personally interested. He further helped to tailor my interests into research that brought benefit to the field of HPC in addition to my personal, academic, and professional advancement.

I would like to thank my friends and family for their patience and support throughout my time at CSU (and even before that as well) and especially Aspen for her deep-rooted encouragement. I would also like to give a special thanks to my lab mates for the late nights (and, let's be honest, early mornings) spent working, writing, and distracting me from the former. It has been a blast hanging out with all of you, and I never could have finished this dissertation without those distracting conversations! (And regardless of how much all of you have come to regret it, I still really appreciate you introducing me to lentils.)

# DEDICATION

I would like to dedicate this thesis to my friends, family, and the progress of HPC.

# TABLE OF CONTENTS

| ACKNOWLE<br>DEDICATIO<br>LIST OF TAB | EDGEMENTS       i         N       i         SLES       i                      | ii<br>v<br>v<br>x |

|--------------------------------------|-------------------------------------------------------------------------------|-------------------|

| Chapter 1                            | Introduction and Overview                                                     | 1                 |

| Chapter 2                            | HPC Node Performance and Energy Modeling with the Co-Location of Applications | 5                 |

| 2.1                                  | Introduction                                                                  | 5                 |

| 2.2                                  |                                                                               | 8                 |

| 2.2.1                                |                                                                               | 8                 |

| 2.2.2                                |                                                                               | 8                 |

| 2.2.3                                | Scheduling Heuristics                                                         |                   |

| 2.3                                  | Modeling Methodology                                                          |                   |

| 2.3.1                                | Overview                                                                      |                   |

| 2.3.2                                | Model Features                                                                |                   |

| 2.3.2                                | Generality of the Models                                                      |                   |

| 2.3.4                                | Linear Modeling Technique                                                     |                   |

| 2.3.5                                | Neural Network Modeling Technique                                             |                   |

| 2.3.6                                | Model Accuracy                                                                |                   |

| 2.3.0                                |                                                                               |                   |

| 2.4.1                                | Testing Environment                                                           |                   |

| 2.4.2                                | Data Collection and Experimental Setup                                        |                   |

| 2.5                                  | Experimental Results                                                          |                   |

| 2.5.1                                | Overview                                                                      |                   |

| 2.5.2                                | Results of Linear Modeling                                                    |                   |

| 2.5.2                                | Results of Neural Network Modeling                                            |                   |

| 2.5.4                                | Calculating System Energy Use from Time Predictions and Average               |                   |

| 2.3.1                                | Power                                                                         | 1                 |

| 2.5.5                                | Model Accuracy                                                                |                   |

| 2.5.5                                | Prediction Model Utility                                                      |                   |

| 2.6.1                                | Overview                                                                      |                   |

| 2.6.2                                | Simulator                                                                     |                   |

| 2.6.3                                | Data Collection                                                               |                   |

| 2.6.4                                | Task Simulation   33                                                          |                   |

| 2.6.5                                | Scheduling Heuristics                                                         |                   |

| 2.6.6                                | System Measurements                                                           |                   |

| 2.6.7                                | Experimental Setup                                                            |                   |

| 2.6.8                                | Experimental Results                                                          |                   |

| 2.0.0                                |                                                                               | /                 |

| 2.7       | Conclusions                                                           | . 52 |

|-----------|-----------------------------------------------------------------------|------|

| Chapter 3 | A Performance and Energy Comparison of Fault Tolerance Techniques for |      |

|           | Exascale Computing Systems                                            | . 54 |

| 3.1       | Introduction                                                          |      |

| 3.2       | Related Work                                                          | . 55 |

| 3.2.1     | Overview                                                              |      |

| 3.2.2     | Rollback Recovery                                                     | . 55 |

| 3.2.3     | Redundancy                                                            | . 57 |

| 3.3       | HPC System Simulator                                                  |      |

| 3.3.1     | Overview                                                              |      |

| 3.3.2     | Modeling System Failures                                              | . 58 |

| 3.3.3     | Resilience Technique Simulation                                       |      |

| 3.4       | Exascale Modeling Methodology                                         | 61   |

| 3.4.1     | Overview                                                              | 61   |

| 3.4.2     | NAS Block Tridiagonal Benchmark at Extreme Scales                     |      |

| 3.4.3     | Real-World System Measurements                                        |      |

| 3.4.4     | Communication Power Model                                             | 63   |

| 3.4.5     | Resilience Technique Specific Parameters                              | . 64 |

| 3.4.6     | Simulated System Setup                                                | . 66 |

| 3.5       | Simulation Studies                                                    | . 68 |

| 3.5.1     | Overview                                                              | . 68 |

| 3.5.2     | System Node Reliability                                               | . 69 |

| 3.5.3     | System Size Scalability                                               | . 71 |

| 3.6       | Conclusions                                                           | . 72 |

| Chapter 4 | Resilience-Aware Resource Management for Exascale Computing Systems . | . 73 |

| 4.1       | Introduction                                                          | . 73 |

| 4.2       | Related Work                                                          | . 76 |

| 4.2.1     | Overview                                                              | . 76 |

| 4.2.2     | HPC Resilience                                                        | . 76 |

| 4.2.3     | HPC Resource Management                                               | . 79 |

| 4.3       | Exascale Modeling Methodology                                         |      |

| 4.3.1     | Overview                                                              |      |

| 4.3.2     | Modeling Extreme Scale Applications                                   | . 81 |

| 4.3.3     | Simulated System Setup                                                | . 83 |

| 4.3.4     | System Failure Model                                                  |      |

| 4.3.5     | Communication Model                                                   |      |

| 4.4       | Resilience Protocol Modeling                                          |      |

| 4.4.1     | Overview                                                              | . 86 |

| 4.4.2     | Checkpoint Restart                                                    |      |

| 4.4.3     | Multilevel Checkpointing                                              |      |

| 4.4.4     | Parallel Recovery                                                     |      |

| 4.4.5     | Partial Redundancy                                                    |      |

| 4.5       | Resilience Protocol Execution Time Prediction                         |      |

| 4.5.1     | Overview                                                               | 91      |

|-----------|------------------------------------------------------------------------|---------|

| 4.5.2     | Execution Time Model with Checkpoint/Restart                           | 93      |

| 4.5.3     | Execution Time Model with Multilevel Checkpoint                        | 96      |

| 4.5.4     | Execution Time Model with Parallel Recovery                            | 98      |

| 4.5.5     | Execution Time Model with Redundancy                                   | 100     |

| 4.5.6     | Checkpoint Interval Optimization                                       | 102     |

| 4.6       | Resilience Protocol Performance with Application Scaling               | 103     |

| 4.7       | System Resource Management                                             | 105     |

| 4.7.1     | Overview                                                               | 105     |

| 4.7.2     | FCFS Technique                                                         | 105     |

| 4.7.3     | Random Technique                                                       | 105     |

| 4.7.4     | Slack-Based Technique                                                  | 106     |

| 4.7.5     | Value-Based Techniques                                                 | 106     |

| 4.8       | Resilience Protocol Effects on Resource Management                     | 109     |

| 4.9       | Resilience-Aware Resource Management                                   | 111     |

| 4.10      | Conclusions                                                            | 115     |

| Chapter 5 | Optimizing Checkpoint Intervals for Reduced Energy Use in Exascale Sys | tems117 |

| 5.1       |                                                                        |         |

| 5.2       | Related Work                                                           |         |

| 5.3       | Exascale Modeling Methodology                                          |         |

| 5.3.1     | Overview                                                               |         |

| 5.3.2     | Applications Model                                                     |         |

| 5.3.3     | Simulated System Setup                                                 |         |

| 5.3.4     | System Failure Model                                                   |         |

| 5.3.5     | Communication Model                                                    |         |

| 5.4       | Fault Resilience Techniques                                            |         |

| 5.4.1     | Overview                                                               |         |

| 5.4.2     | Checkpoint Restart                                                     |         |

| 5.4.3     | Multilevel Checkpointing                                               |         |

| 5.5       | Energy Use Prediction and Checkpoint Interval Optimization             |         |

| 5.6       | Simulation Experiments                                                 |         |

| 5.6.1     | Overview                                                               |         |

| 5.6.2     | Optimization Trade Off                                                 | 132     |

| 5.6.3     | Sensitivity Analysis                                                   |         |

| 5.7       | Conclusions                                                            | 134     |

| Chapter 6 | An Analysis of Multilevel Checkpoint Performance Models                | 136     |

| 6.1       |                                                                        |         |

| 6.2       | Related work                                                           |         |

| 6.2.1     | Overview                                                               |         |

| 6.2.2     | Multilevel Checkpointing Techniques Considered                         |         |

| 6.2.3     | Multilevel Checkpoint Interval Optimization                            |         |

| 6.3       | Multilevel Checkpointing Model                                         |         |

| 6.3.1     | Overview                                                               |         |

| 0.0.1     |                                                                        |         |

| 6.3.2        | Execution Time Prediction Model                                        |

|--------------|------------------------------------------------------------------------|

| 6.3.3        | Checkpoint Interval Optimization                                       |

| 6.4          | Simulation Studies                                                     |

| 6.4.1        | Overview                                                               |

| 6.4.2        | HPC System Simulator                                                   |

| 6.4.3        | Performance on Prior Work Test Systems                                 |

| 6.4.4        | Failures During Checkpoints and Restarts                               |

| 6.4.5        | Performance at Extreme-Scale System Difficulty                         |

| 6.4.6        | Consideration of Application Execution Time                            |

| 6.4.7        | Model Prediction Accuracy                                              |

| 6.5          | Conclusions                                                            |

| Chapter 7    | Modeling Application Fragmentation and Network Congestion in the pres- |

| I            | ence of HPC Resilience                                                 |

| 7.1          | Introduction                                                           |

| 7.2          | Related Work                                                           |

| 7.3          | Modeling Methodology                                                   |

| 7.3.1        | Overview                                                               |

| 7.3.2        | Network Model                                                          |

| 7.3.3        | Application Communication Pattern                                      |

| 7.3.4        | Parallel File System                                                   |

| 7.3.5        | System Resilience                                                      |

| 7.4          | Simulation Experiments                                                 |

| 7.5          | Conclusions                                                            |

| Chapter 8    | Conclusions and Future Work                                            |

| 8.1          | Conclusions                                                            |

| 8.2          | Future Work                                                            |

| Bibliography |                                                                        |

# LIST OF TABLES

| 2.1 | Model features                           |

|-----|------------------------------------------|

| 2.2 | Model feature sets                       |

| 2.3 | Memory intensity classification          |

| 2.4 | Multicore processors used for validation |

| 2.5 | Training schedule                        |

| 3.1 | Simulated System Parameters              |

| 4.1 | Characteristics of Application Types     |

|     | Resilience Protocol Parameters           |

| 6.1 | Test Systems Examined in Prior Work      |

#### LIST OF FIGURES

2

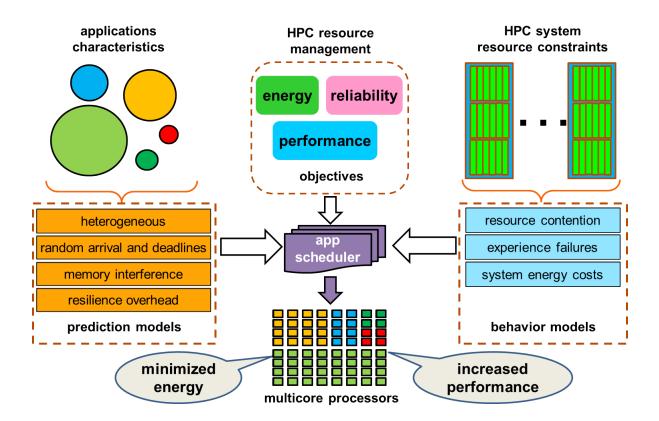

- 1.1 Overview of the framework proposed for HPC resource management.

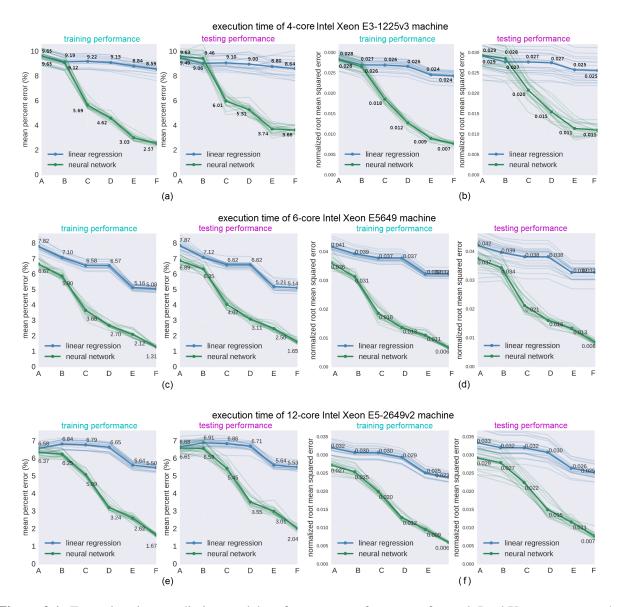

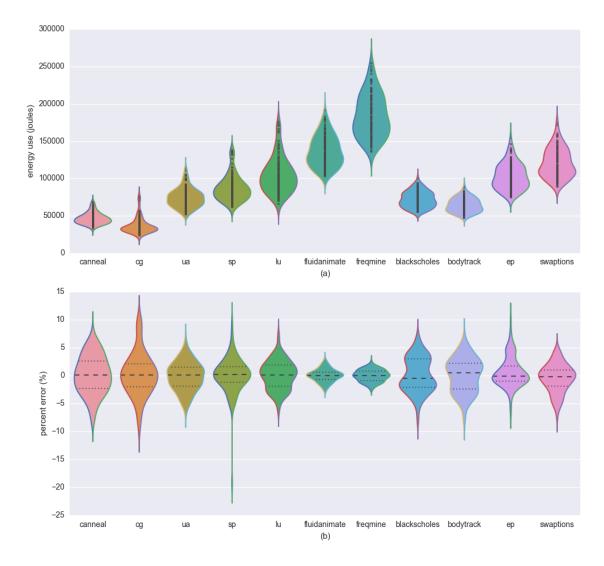

- 2.1 Execution time prediction model performance per feature set for each Intel Xeon processor. (a, c, e) Show MPE for the performance of training and testing data sets for model feature sets A through F. (b, d, f) Show NRMSE for the performance of training and testing data sets for model feature sets A through F. The figure shows results for each of the machine learning techniques: *linear* (blue) and *neural networks* (green). Each point on the figure represents an average of twenty different partitions of the data into training and testing data. Annotations next to points indicate the value of the point. The lighter shaded lines indicate the average value across all twenty partitions. 25

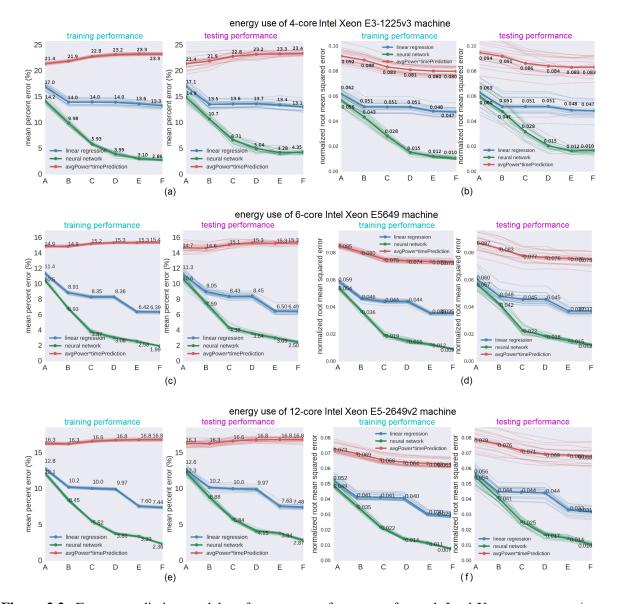

- 2.2 Energy prediction model performance per feature set for each Intel Xeon processor. (a, c, e) Show MPE for the performance of training and testing data sets for model feature sets A through F. (b, d, f) Show NRMSE for the performance of training and testing data sets for model feature sets A through F. The figure shows results for each of the machine learning techniques: *linear* (blue) and *neural networks* (green), as well as a comparison to the results that are obtained by simply multiplying the corresponding feature set of the neural network execution time prediction for each processor (the results shown in Figure 2.1) to each test's measured baseline average power value (red). Each point on the figure represents an average of twenty different partitions of the data into training and testing data. Annotations next to points indicate the value of the point. The lighter shaded lines indicate the average value across all twenty partitions. 26

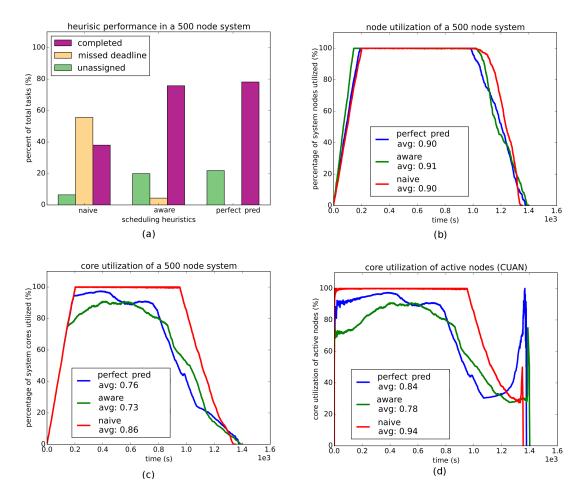

- 2.5 Simulation results of an <u>oversubscribed</u>500 node homogeneous system comprised of 4-core Intel Xeon E3-1225v3 processors. (a) Shows scheduling heuristic performance.

(b) Shows node utilization of the simulated system. (c) Shows core utilization of the simulated system. (d) Shows core utilization of active nodes (CUAN) of the simulated system. In (a), the purple bar shows the percentage of total tasks completed, the brown bar shows the percentage of total tasks that missed their deadlines, and the green bar shows the percentage of tasks that were left unassigned. In (b), (c), and (d) the red line indicates the naïve heuristic utilizations, the green line indicates the co-location aware heuristic utilizations, and the blue line indicates the perfect prediction utilizations. . . . 50

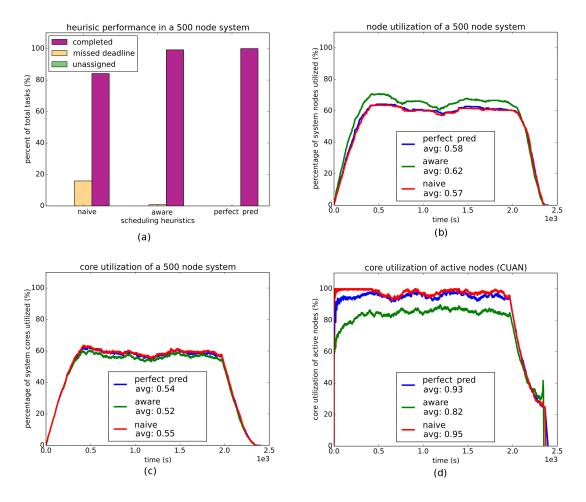

| of 4-core Intel Xeon E3-1225v3 processors. (a) Shows scheduling heuristic perfor-<br>mance. (b) Shows node utilization of the simulated system. (c) Shows core utilization<br>of the simulated system. (d) Shows core utilization of active nodes (CUAN) of the<br>simulated system. In (a), the purple bar shows the percentage of total tasks completed,<br>the brown bar shows the percentage of total tasks that missed their deadlines, and the<br>green bar shows the percentage of tasks that were left unassigned. In (b), (c), and (d)<br>the red line indicates the naïve heuristic utilizations, the green line indicates the co-<br>location aware heuristic utilizations, and the blue line indicates the perfect prediction<br>utilizations.       | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

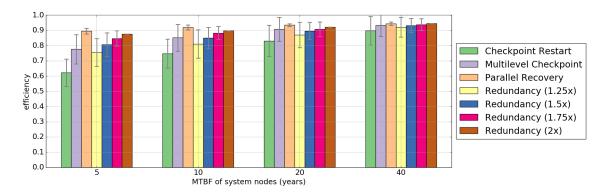

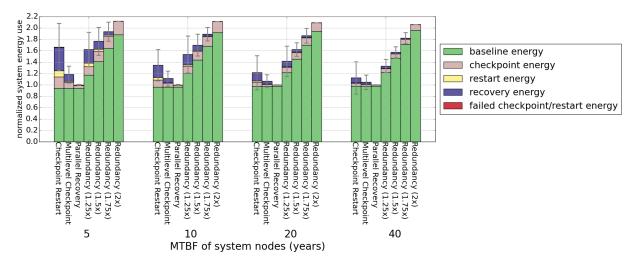

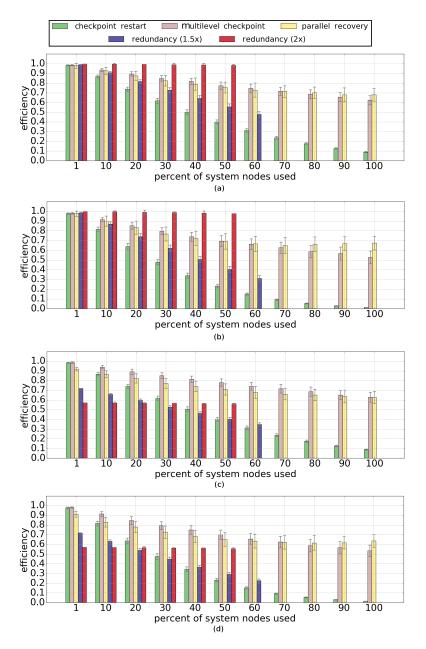

| Resilience technique efficiency at various levels of system node reliability. Efficiency is defined to be the ratio of an application's time without slowdowns (from failures or checkpointing) over the application's execution time with slowdowns (from failures or checkpointing). Each bar in the figure represents the average of 200 trials. Standard                                                                                                                                                                                                                                                                                                                                                                                                     | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| deviations are shown for each bar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68<br>68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

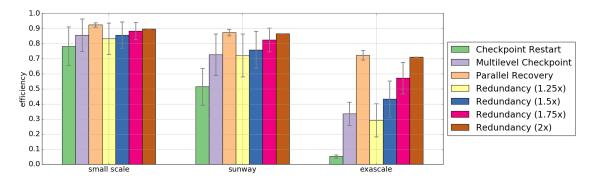

| Resilience technique efficiency at various system sizes. Efficiency is defined to be<br>the ratio of an application's time without slowdowns (from failures or checkpointing)<br>over the application's execution time with slowdowns (from failures or checkpointing).<br>Each bar in the figure represents the average of 200 trials. Standard deviations are                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Resilience technique energy use at various system sizes. The height of each bar in the figure depicts the normalized total energy consumed by each technique. The colors of each bar represent how system energy was consumed. Total energy consumption for each system size is normalized to the Parallel Recovery technique. Each bar in the figure represents the average of 200 trials. Standard deviations of each technique's normalized total energy are shown for each bar. Annotations in the subset of the exascale                                                                                                                                                                                                                                    | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

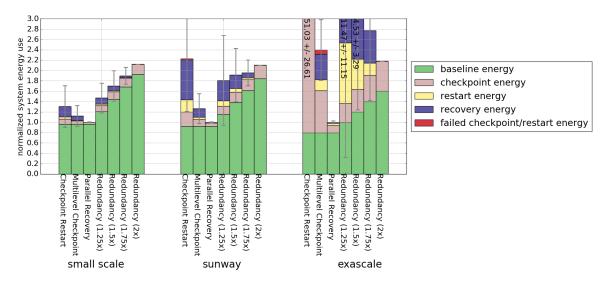

| Resilience protocol efficiency at increasing percentages of total system use, ( <b>a</b> ) by the low memory use and low communication application defined in Table 4.1 as $L_{32}$ , ( <b>b</b> ) by the high memory low communication application ( $L_{64}$ ), ( <b>c</b> ) by the low memory high communication application ( $H_{32}$ ), ( <b>d</b> ) by the high memory high communication application ( $H_{64}$ ). Efficiency is defined to be the ratio of an application's execution time without slowdowns (from failures or checkpointing) over the application's execution time with slowdowns (from failures and checkpointing). Processors in the system experience a 2.5 year MTBF. Each bar in the figure represents the average of 200 trials. | 70<br>92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | of the simulated system. (d) Shows core utilization of active nodes (CUAN) of the simulated system. In (a), the purple bar shows the percentage of total tasks completed, the brown bar shows the percentage of total tasks that missed their deadlines, and the green bar shows the percentage of tasks that were left unassigned. In (b), (c), and (d) the red line indicates the naïve heuristic utilizations, the green line indicates the colocation aware heuristic utilizations, and the blue line indicates the perfect prediction utilizations |

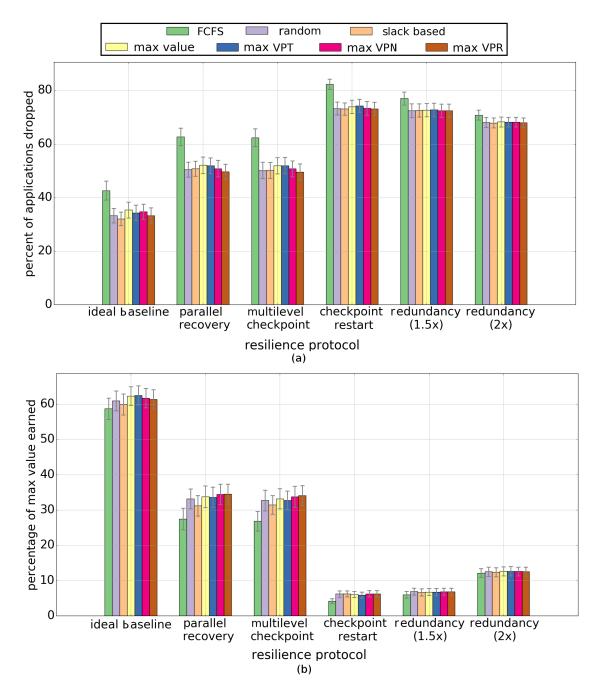

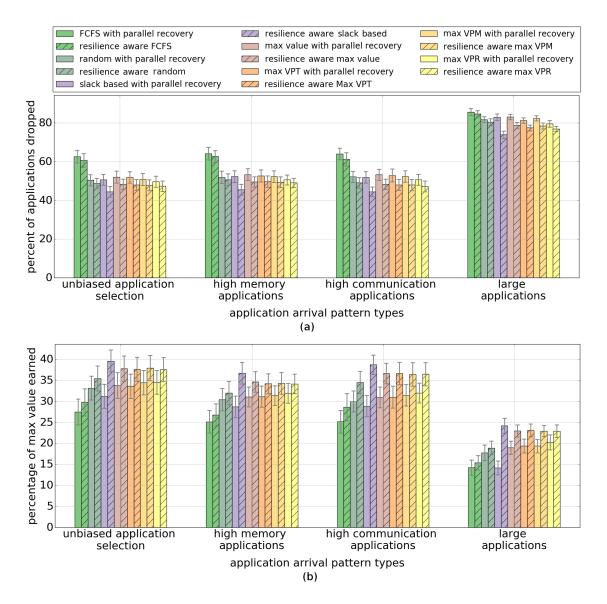

| 4.2 | Performance of the system by: (a) percentage of applications dropped from the system, and (b) percentage of the maximum value earned by the system, for each resilience protocol and resource management technique combination. Bars in the figure represent the average of 50 arrival patterns. Standard deviations are shown for each bar Performance of the system by (a) percentage of applications dropped from the system, and (b) percentage of the maximum value earned by the system, for each resource management technique when resilience-naïve and using the parallel recovery resilience protocol, and each resource management technique when resilience-aware and employing resilience-selection. Groupings of bars show four different types of application arrival patterns. Bars in the figure represent the average of 50 arrival patterns. Standard deviations are shown for each bar |     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

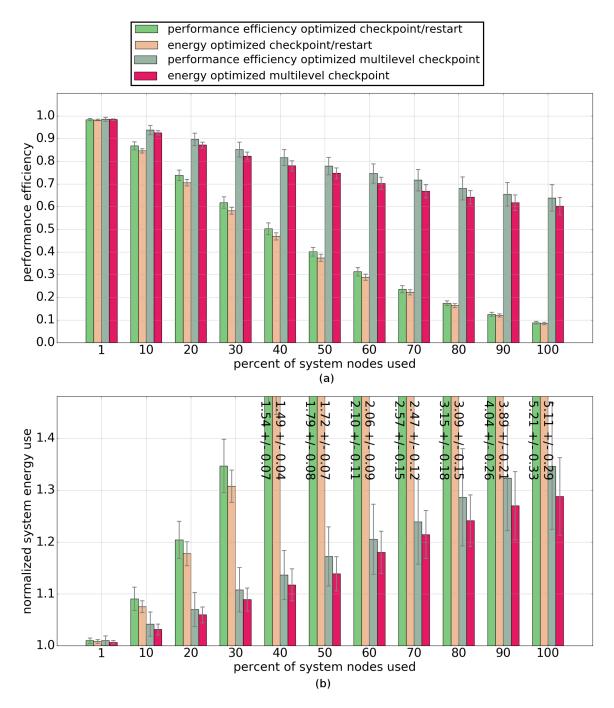

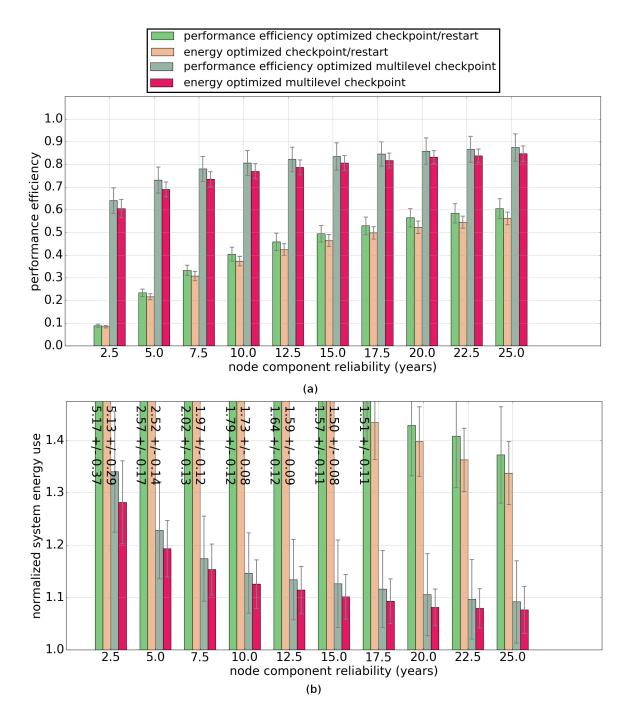

| 5.1 | Application (a) performance efficiency and (b) normalized energy use, when resilience technique checkpoint intervals are optimized for either performance efficiency or energy use and the percentage of system nodes used by the application is increased. Bars in the figure represent the average of 200 simulated trials. Standard deviations are shown for each bar. Annotations in the figure indicate values for the average and                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

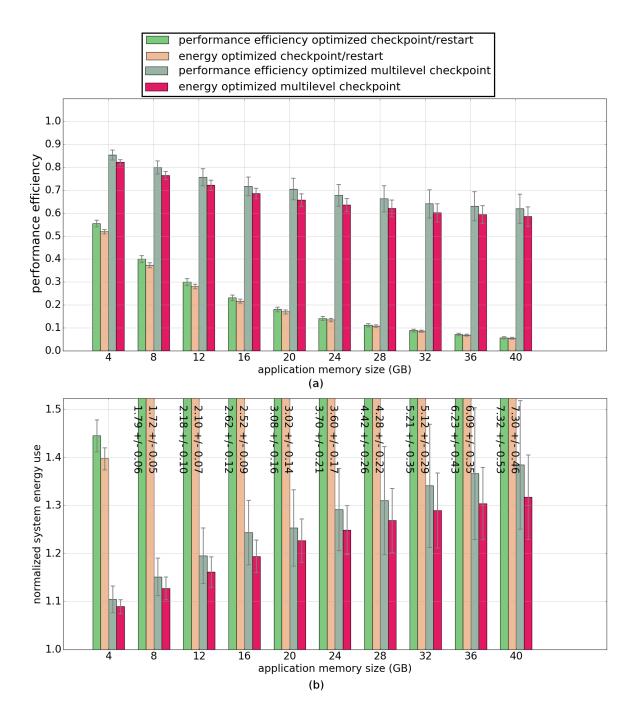

| 5.2 | standard deviation of bars that have been truncated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 128 |

| 5.3 | deviation of bars that have been truncated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

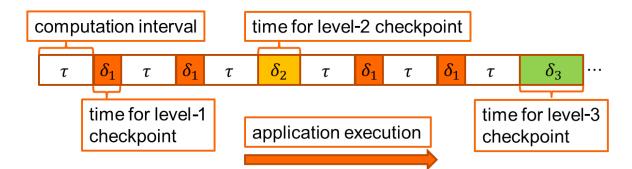

| 6.1 | A checkpoint interval pattern for a three-level checkpointing protocol with its compu-<br>tation interval denoted $\tau$ , its checkpoint lengths of each level <i>i</i> denoted $\delta_i$ , and a pattern<br>that performs two level-1 checkpoints before a level-2 checkpoint and a single level-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

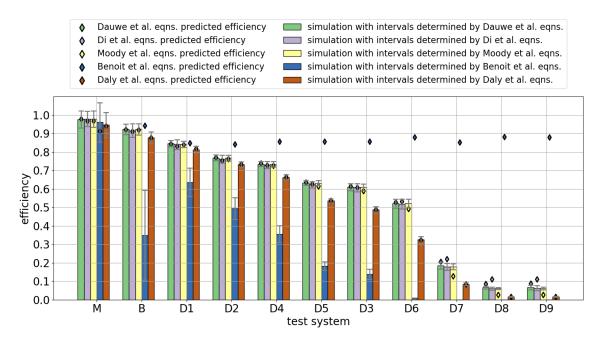

| 6.2 | checkpoint before each level-3 checkpoint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

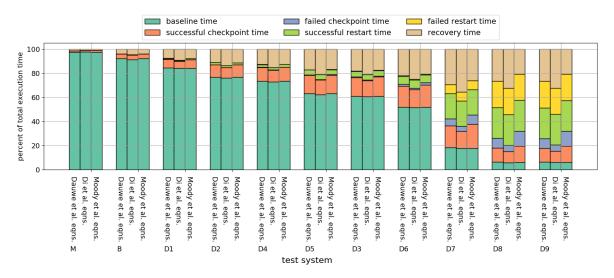

| 6.3 | Percentage of application execution spent on baseline execution of the application as well as all resilience and failure event related overhead during the application's execution. Each test scenario shown represents the average of 200 trials with randomly occurring failures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

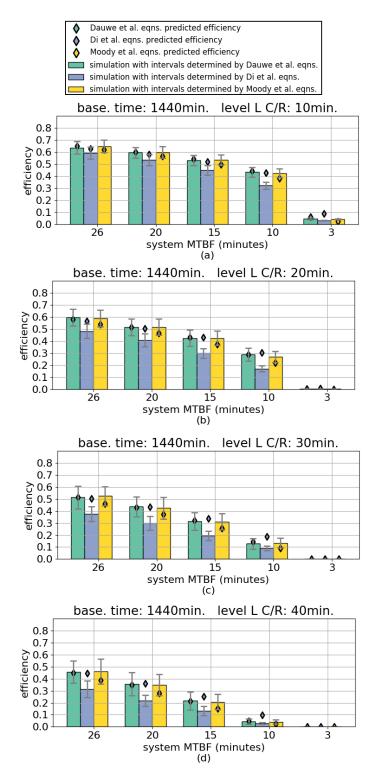

| 6.4 | The execution of a 1440 minute application under a variety of execution scenarios with level-L checkpoint and restart times of (a) 10 minutes, (b) 20 minutes, (c) 30 minutes and (d) 40 minutes. Bars in the figure indicate the average of 200 simulation trials with randomly occurring failures. Diamonds in the figure indicate each technique's prediction of the simulated performance. Standard deviations are shown for each bar.                                                                                                                         | 154 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

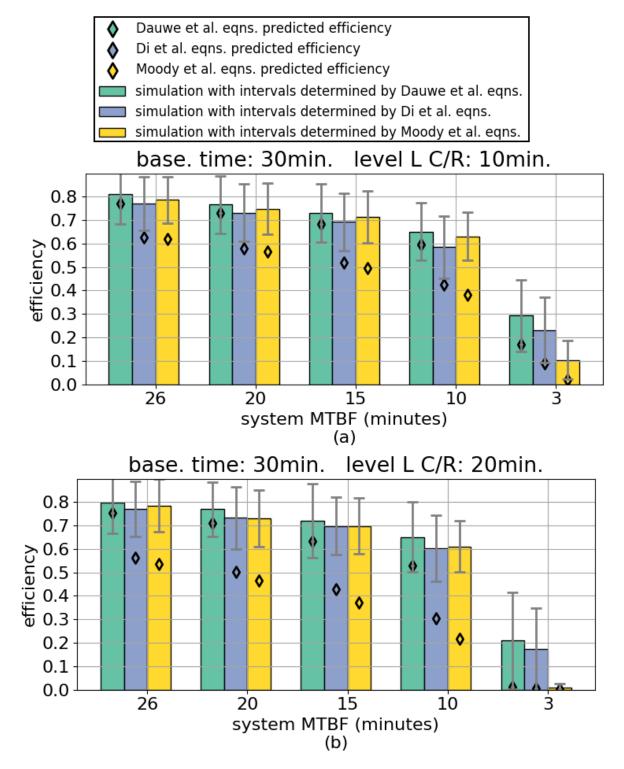

| 6.5 | The execution of a 30 minute application under a variety of execution scenarios with level-L checkpoint and restart times of (a) 10 minutes and (b) 20 minutes. Bars in the figure indicate the average of 400 trials with randomly occurring failures. Diamonds in the figure indicate each technique's prediction of the simulated performance. Standard                                                                                                                                                                                                         |     |

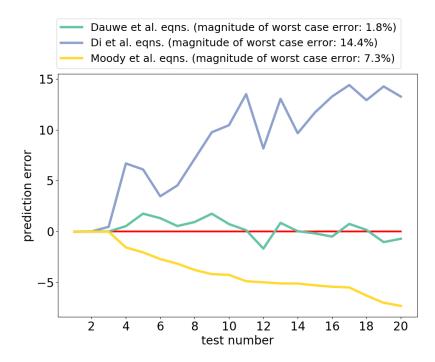

| 6.6 | deviations are shown for each bar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

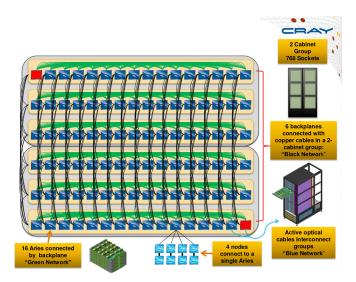

| 7.1 | Overview of the interconnection of the Cray XC30 network. Dark blue tiles indicate system blades composed of eight compute nodes (compute nodes indicated by the light-blue tiles at the bottom of the figure). Red tiles indicate blades used as cabinet service nodes with each cabinet having two service nodes. Green links indicate all-to-all backplane link connections present between blades in a chassis (with chassis indicated by the tan boxes). Black links indicate the connections existing between chassis. This forum has been adopted from [1]. | 166 |

| 7.2 | chassis. This figure has been adapted from [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 166 |

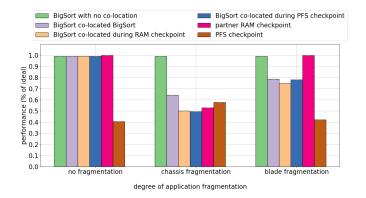

|     | execution scenarios.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 170 |

# **Chapter 1**

# **Introduction and Overview**

High-performance computing (HPC) systems such as data centers and supercomputers are complex systems that coordinate the execution of large-scale computation of applications over tens or hundreds of thousands of multicore processors. Unfortunately, applications executing in parallel across multicore processors can suffer from decreased performance and increased energy use as a result of the applications being forced to share resources and consequently interfering with each other's execution. This interference occurs at multiple levels of the system from individual components (e.g., threads in a multicore processor forced to share the last-level processor cache) to the system level (e.g., applications sharing network resources). Complicating matters further, as the size of HPC systems continues to grow exponentially the systems also experience an exponential growth in the number of failure-related events that occur and cause interrupts in application execution. These failures cause further decreases in performance and increases in energy use, making HPC progress more challenging. The research discussed here examines ways of intelligently utilizing system resources and addressing distributed failures to mitigate these negative effects in HPC systems.

The progress of HPC systems in terms of both performance and energy efficiency are continually monitored by the Top500 [2] and Green500 [3] lists respectively. Extrapolating the energy use and performance from the top supercomputers on these lists highlights the necessity of designing the next generation HPC systems around energy efficiency. Even if the most energy-efficient HPC system from [3] were scaled to exascale complexities and able to retain its peak performance efficiency of 17 GFlops/W, such a system would still require at least \$59 million per year just to operate. Additional overhead from increased system failures add further operational costs. Without suitable resilience techniques in operation the system would experience significantly increased energy costs from failed applications. It is estimated that the significantly smaller 13 petaflop Blue Waters systems would spend over \$400,000 in wasted energy without checkpoint/restart resilience helping to mitigate the wasted energy of system failures. Given the superlinear increase in failure rates that is expected as systems progress toward exascale, the consideration of HPC resilience is critical for the design of an exascale system.

This research investigates both how to better characterize and model the negative effects that resource sharing and system failures have on large-scale computing systems, as well as developing techniques for intelligently utilizing system resources through optimal application scheduling. Relying on scheduling to better utilize system resources for solving these performance and energy problems allows the users of HPC systems the benefit of being able to be unaware of the complex strategies employed by the system on their behalf to provide the most efficient execution possible.

Figure 1.1: Overview of the framework proposed for HPC resource management.

Here we describe our development of a resource management framework used for analyzing and improving these HPC environments. An overview of this framework is depicted in Figure 1.1. The top center of the figure shows the framework's three resource management objectives of energy, reliability, and performance for HPC systems.

The left-hand side of the figure details examples of the uncertain characteristics associated with application execution (e.g., execution overhead and inter-application interference) that make resource management in HPC systems challenging. To help reduce this uncertainty several of the chapters in this dissertation detail methodologies that allow for the creation of application performance prediction models that can be utilized by HPC resource management techniques to make better scheduling decisions for the applications demanding system resources.

The right-hand side of the figure gives examples of system constraints that limit the demand that can be satisfied by the system scheduler when attempting to accommodate an application's expected (or predicted) execution behavior. Interactions among the demands of applications on system resources, the resource's respective constraints, and the effects of decisions made by the system scheduler are complex. The research discussed throughout this dissertation employs models that describe the behavior of system resources (e.g., resource contention, application resilience behavior, and the system's responses to failures) for these complex situations.

Our proposed framework ensures that the design of the system's application scheduler can be made aware of the system's design objectives as well as the constraints associated with the system's available resources, the application's resource demands, and the application's execution characteristics. The system scheduler then works with the available data to ensure the system's objectives are met by determining for each application:

- when the application should begin execution;

- on which processors the application should execute;

- the type and timing of events associated with the application's resilience to system failures.

The models and design methodologies discussed in this dissertation have been integrated into our simulated analyses of system behavior and are used to assess our resource management technique's ability to accommodate the system objectives of performance, reliability, and minimized energy.

3

The remainder of this dissertation is organized as follows. The next chapter (Chapter 2) discusses the impact that memory interference has on HPC systems and outlines a methodology that can be used to model application memory interference behavior and make predictions about the effects that co-location will have on the application's execution. We utilize this prediction methodology by creating a memory interference aware resource management framework and analyzing its benefit to an environment that suffers from performance degradation due to application co-location. We analyze the behavior of resilience protocols used for mitigating system failures in HPC systems in Chapter 3 and develop models for simulating the behavior of several resilience protocols being proposed for future extreme scale HPC systems. Chapter 4 discusses how the resilience protocol models from Chapter 3 can be utilized to build a resilience aware resource management framework. Chapters 5 and 6 consider in more detail the optimization of multilevel checkpointing intervals for improving application performance, system energy use, and application execution time prediction accuracy. A closer examination of the interrelated effects of checkpointing and the system's communication network is conducted in Chapter 7. We conclude in Chapter 8 with a discussion of future directions for this research.

# **Chapter 2**

# HPC Node Performance and Energy Modeling with the Co-Location of Applications

# 2.1 Introduction

There is an inherent trade-off in large-scale computing systems between reducing the use of system resources by consolidating applications into as few server processor nodes as possible (to reduce system power), and the performance degradation that occurs to these applications as a result of sharing system resources with other applications (e.g., [7], [8]). Memory interference caused by multiple applications co-located on a multicore processor has been shown to negatively impact application performance (e.g., [9], [10], [11], [6], [12]). Specifically, the sharing of system resources such as DRAM and the last-level cache by co-located applications creates contention and increases the memory intensity of all applications running on the multicore processor [6]. This increase in memory intensity results in a corresponding increase in average memory access time, which ultimately contributes to an increase in the application's overall execution time. This increase in execution time is significant, and in some cases can as much as double or triple the execution time of an application as compared to its baseline execution time, i.e., when unhindered by co-location interference [13].

Multicore processors are pervasive throughout many kinds of computing systems, but the performance degradation effects caused by co-location interference are most likely to be prevalent

This work was done jointly with Ph.D. student Ryan Friese and masters student Eric Jonardi. The full list of coauthors is listed in [4]. This work was supported by the National Science Foundation (NSF) under grant numbers CNS-0905339, CCF-1252500, CCF-1302693, ACI-1339745, and an NSF Graduate Research Fellowship. Any opinion, findings, and conclusions or recommendations expressed in this material are those of the authors and do not necessarily reflect the views of the NSF. The authors thank Hewlett Packard (HP) of Fort Collins for providing us some of the machines used for testing. A preliminary version of portions of this work appeared in [5] and [6].

in large-scale server systems and high-performance computers. This is because in those types of computing systems, executing multiple applications on multicore processors results in high memory interference and therefore causes performance degradation [14]. Having a methodology that is capable of predicting how well a system will run in a particular co-location scenario is very useful for such systems. The results of this work show how the information obtained from accurate predictions of co-location performance degradation can be integrated into intelligent application scheduling, and thus lead to system performance improvement due to better utilization of the hardware. Better utilization of the hardware provides increased opportunities to reduce power and save energy through server consolidation, while still maintaining quality of service constraints in an improved manner over a co-location naïve scheduler. This work provides a methodology that can be used to create co-location aware performance models capable of predicting application execution time and energy use when co-located with other applications on a multicore processor in an HPC node.

The methodology for analyzing system performance that is described in this work is general enough to be applicable to any set of applications running on any multicore processor. Once application performance information for a particular combination of multicore processor and target applications has been collected, the methodology uses machine learning techniques to construct performance models characterizing that information. After they are trained, these models require only a single serial baseline measurement of parameters for each application running alone in the system. The models use this serial baseline measurement to make predictions about the performance degradation from memory interference that will occur when the application is executing with different types of co-located applications. While it has been shown in [10] that the degree to which an application's use of memory resources varies among different phases throughout the application's execution, this work illustrates that having such fine grain information is not always necessary to make accurate predictions.

After describing how the methodology operates, the theory behind the proposed methodology is validated by using real-world data collected on three Intel Xeon server-class machines that were

6

set to execute a collection of scientific application workloads, with some models providing up to 98% accuracy. In addition to creating and demonstrating a methodology that is capable of being ported across processor architectures, this work also provides insight into what memory-use information is most important to obtain for a set of applications running in a system to predict the impact of co-location on performance and energy use.

The last portion of this work demonstrates the utility of the proposed modeling methodology through the creation and analysis of a consolidating slack-based scheduling heuristic that utilizes the execution time prediction models generated from the proposed modeling methodology to assist in its application co-location decisions. This "co-location aware" scheduling heuristic is shown in simulated studies to provide a significant performance improvement over a similar consolidating slack-based scheduling heuristic that is naïve to the effects of performance degradation caused by co-location.

This chapter makes the following contributions:

- (a) identifies factors that can characterize slowdown during application co-location scenarios;

- (b) proposes a novel methodology to integrate these factors into multi-granularity and multifidelity performance models that can be used to predict application execution time and energy use under co-location scenarios;

- (c) shows that a fine level of detail is not always necessary to achieve reasonable prediction accuracy;

- (d) validates the methodology with real-world data obtained from running co-located scientific workloads on contemporary Intel Xeon server-scale multicore processors with up to 12 cores per processor;

- (e) demonstrates through simulation the utility of the modeling methodology through the creation of a consolidating slack-based scheduling heuristic that utilizes models created from the proposed modeling methodology for its scheduling decisions.

The rest of this chapter is organized as follows. The following section discusses related work in this area. The modeling methodology is presented in Section 2.3. Section 2.4 details the testing environment and data collection used for validating the models. Experimental results that validate the models are examined in Section 2.5. A demonstration of the modeling methodology's utility is shown in Section 2.6. The chapter concludes with a summary of the main contributions in Section 2.7.

# 2.2 Related Work

# 2.2.1 Overview

Several works have explored the effect of co-location on application performance and energy use in multicore environments and the use of scheduling heuristics for improving the efficiency of high performance computing. Here the most relevant prior works in these areas are briefly summarized.

# 2.2.2 The Effect of Application Co-location on Performance and Energy Use

The authors in [9] examine how co-locating multiple applications on a single multicore processor affects performance. However, their work focuses on a general examination of the effects that co-location has on the system as a whole, and does not examine the effects on specific applications as our work does. This work also does not create co-location performance models the way that our work does, nor does it discuss modeling energy use. Our work also discusses a heuristic approach for mapping co-located processes to processor cores, whereas their analysis only examines a single processor node, providing a less precise view than our work where we consider an entire system.

The study in [10] provides an excellent review of how the architecture on which an application is executed can affect the cache use and memory intensity of that application. That work, however, does not attempt to make predictions about performance degradation as we do, but rather it shows the importance of including memory intensity and cache usage information when characterizing performance degradation in the presence of application co-location. The work in [15] describes the challenges faced by applications sharing resources, and a need for the ability to perform precise predictions of performance degradation. The paper presents its "Bubble-Up" methodology for predicting performance degradation. However, it does not consider the impact of dynamic voltage and frequency scaling on application performance as we do in our work, and their study does not collect experimental data or characterize the memory interference effects of having more than two applications co-located, whereas we examine the performance degradation effects of more than two co-located applications

The authors in [11] present an extension to the "energy roofline" model that explores the effect of memory intensity (from the perspective of arithmetic intensity) on execution time and power use. The study executes a series of constructed microbenchmarks on twelve machine architectures and provides an analysis of the performance of the systems. While that study collects data about performance degradation from memory interference on a set of real machines, it uses small "microbenchmark" tests on machines, as opposed to the scientific workloads we use. Moreover, their work does not create models to predict execution times or energy use based on memory interference.

Similar to our work, the work in [16] examines creating a portable methodology using machine learning techniques for predicting application performance degradation from shared resources. The authors in that paper also incorporate shared resources beyond the last-level cache. However, incorporating those resources causes the resulting model to be complicated, and their model requires the constant monitoring of a large number of processor performance counters, which can cause system-wide slowdown for all running applications. In contrast, our methodology needs to collect performance counter information about each application only a single time, and provides a better prediction of performance. Additionally, our methodology guarantees a uniform selection of training data over the possible co-location space (allowing for more portability) while the work from these authors selects the vast majority of its training data at random.

A methodology for online estimation of an application's execution under co-location is presented as the "Application Slowdown Model" in [12]. Similar to our work, their work makes

9

predictions of application performance degradation by monitoring processor performance counters. However, their work does not perform any experiments on how the methodology performs for any actual server class processor as our work does, and therefore it is potentially limited in its portability or performance on actual systems. Additionally, their work limits their proposed models to analyzing the effect of performance degradation on application execution time and does not attempt to model energy as our work does.

Our work in [6] measures memory interference from application co-location, and its impact on system performance and energy use for a single Intel i7 machine. However, that work does not create models that predict system performance, and the scope is restricted to only a single consumer class machine.

We acknowledge that work exploring the effect of simultaneous multithreading (<u>SMT</u>) on application performance is an open and active area of research. Papers such as [17], [18], and [19] examine scheduling and resource use of applications executed utilizing SMT. We chose to focus our study on the interference that applications experience at an inter-core granularity, and for this study we have turned off SMT to remove the possibility of application interference in the L1 cache.

## 2.2.3 Scheduling Heuristics

Examples of prior work in scheduling for large-scale HPC systems have appeared in [20], [21], [22], and [23]. In [20], the authors look at the problem of energy-constrained dynamic allocations of tasks in heterogeneous cluster computing environments, in the presence of individual task deadlines. The work in [21] proposes power and thermal-aware scheduling to optimize individual tasks reaching their deadlines. A "utility" metric is defined in [22] that is used in combination with several energy-aware scheduling heuristics to provide a method of resource allocation that can maximize task performance while operating under a system energy constraint. The work in [23] examines energy-aware static resource allocation of a "bag of tasks" in a heterogeneous computing system. However, all of these existing techniques in scheduling do not focus on co-location effects that can significantly impact the validity of scheduling decisions.

In contrast to the above prior works, some researchers have proposed slack-based heuristics to improve system performance. For example, the work in [24], [25], [26], and any of the other numerous works that rely on the backfilling technique first described in [27], all rely on slack-based heuristics that perform their calculations based on predictions of application execution time. All of these works use application slack to provide better scheduling around uncertainty, but none of them account for the effects of performance degradation from co-location. As we demonstrate later, slack-based heuristics that are co-location aware can outperform co-location naïve slack-based heuristics. Consideration of co-location in the slack calculations of these works could be used to improve upon the work presented in these papers.

# 2.3 Modeling Methodology

# 2.3.1 Overview

The proposed modeling methodology uses two types of machine learning techniques, *linear modeling* and *neural networks*, for constructing the predictive models. These techniques have been used in prior related work [16], [15], but were limited in attribute selection and scope. For each machine learning technique, several models of varying levels of complexity and utilization of application features were built.

## 2.3.2 Model Features

Both the execution time and energy prediction models use up to eight separate features of application execution to predict how the target application performance or energy use is impacted by co-located applications. The eight features were chosen by performing a principal component analysis (<u>PCA</u>) [28] on the data collected from multicore processors considered in this work. PCA allows us to observe which features were most important to include in the models.

The features selected are a general set that are observable in almost all multicore processors. The models we construct use various combinations of the features. These models use different combinations of features, ranging from those that are most-commonly available to a scheduler to combinations that require detailed information about the application and may be difficult to obtain on some platforms. The eight features that we selected after our PCA analysis are shown in Table 2.1. The table gives the name of the feature in the first column, and the description of that feature in the second column. The "target" application in the table is the one for which slowdown or increased energy use due to co-location is being predicted. The <u>baseline execution time</u> is the execution time of the target application without any co-location present. A task's <u>memory intensity</u> is defined to be the ratio of a task's last-level cache missed to the total number of instructions that the task has executed. Memory intensity is discussed further in Section 2.4.

| ŗ | <b>Fable</b> | 2.1: | Model | features |  |

|---|--------------|------|-------|----------|--|

|   |              |      |       |          |  |

| feature name                               | description of feature                                        |  |

|--------------------------------------------|---------------------------------------------------------------|--|

| baseExTime                                 | baseline execution time of target application at all P-states |  |

| numCoApp number of co-located applications |                                                               |  |

| coAppMem                                   | sum of co-application memory intensities                      |  |

| targetMem                                  | target application memory intensity                           |  |

| coAppCM/CA                                 | sum of co-application last-level cache misses/cache accesses  |  |

| coAppCA/NI                                 | sum of co-application last-level cache accesses/instructions  |  |

| targetCM/CA                                | target application last-level cache misses/cache accesses     |  |

| targetCA/NI                                | target application last-level cache accesses/instructions     |  |

#### Table 2.2: Model feature sets

| set name | features within set                              |  |

|----------|--------------------------------------------------|--|

| A        | baseExTime                                       |  |

| В        | baseExTime, numCoApp                             |  |

| С        | baseExTime, numCoApp, coAppMem                   |  |

| D        | baseExTime, numCoApp, coAppMem, targetMem        |  |

| E        | baseExTime, numCoApp, coAppMem, targetMem,       |  |

|          | coAppCM/CA, coAppCA/NI                           |  |

| F        | baseExTime, numCoApp, coAppMem, targetMem,       |  |

|          | coAppCM/CA, coAppCA/NI, targetCM/CA, targetCA/NI |  |

### **2.3.3** Generality of the Models

The features shown in Table 2.1 can be combined to create models of various complexities. The model feature sets listed in Table 2.2 represent six possible models, one baseline model (model "A") that uses only the *baseExTime* feature for predictions, and five other models. For each of the five other models, the resource manger (scheduler) has a certain amount of baseline information about the system, the target application, and the other applications co-located on the system. The progression from one model to the next represents a realistic process where the resource manager progressively obtains more detailed information about the computing system and its executing applications.

Designing a methodology that provides several models with various levels of complexity allows a system designer greater freedom to make use of the modeling methodology to predict application performance and energy use. Providing a set of models with a range of complexities allows for a prediction model with a basic feature set to be used when more detailed application execution information for applications in the system is not available. For example, a system designer may not know or have the ability to measure the performance counter derived information (explained in Section 2.4) required to create more complicated models, but could have access to adequate application information (such as baseExTime and NumCoApp) to use the methodology to design simpler models that still give reasonable prediction accuracy and benefit from co-location awareness.

### 2.3.4 Linear Modeling Technique

To predict the impact of application performance degradation and energy use during execution under co-location, twelve linear models were developed: a set of six models for execution time prediction, and a set of six models for energy use prediction. Each of the six models in each set of models were constructed using the six model feature sets listed in Table 2.2. Each linear model is the sum of the products of the utilized features (denoted  $f_i$ ) and the model coefficients determined during training (denoted for the execution time model as  $ct_i$  and denoted for the energy use model as  $ce_i$ ), plus a <u>constant</u> const. Linear regression is used to calculate the values for the coefficients. A general linear model for predicting co-located execution time using N features (linear <u>execution</u> time prediction LETP) takes the form of:

$$LETP = \sum_{i=1}^{N} (ct_i * f_i) + const$$

. (2.1)

The linear prediction of execution time and energy differ only in the objective that the models are trained to predict (execution time or energy use). A general linear model for predicting colocated energy use using N features (linear energy use prediction LEUP) takes the form of:

$$LEUP = \sum_{i=1}^{N} (ce_i * f_i) + const .$$

(2.2)

#### 2.3.5 Neural Network Modeling Technique

From our observation of application execution in the presence of co-location, we noted that there are a few instances of nonlinearity in some of the features. This observed nonlinearity provided the motivation for creating a prediction model using a neural network that can capture such nonlinearities.

Neural networks are a class of machine learning techniques that can be used for creating predictive models [29]. The approach attempts to mimic the function of the human brain by defining several "layers of neurons." Each neuron layer is composed of some number of individual neurons that take the outputs of the previous layer as each of their inputs, with the inputs to the first layer of neurons being the features of the data available in each model (see Tables 2.1 and 2.2 ). The final output is the value of the predicted execution time or energy use that the application will experience under co-location.

Each neuron operates by multiplying each of its N inputs,  $x_i$ , by N corresponding weight parameters,  $w_i$ , summing these results, and finally evaluating the sum with a nonlinear function f. The  $k^{th}$  neuron in layer j (denoted  $y_{jk}$ ) operates according to:

$$y_{jk} = f(\sum_{i=1}^{N} x_i w_i)$$

(2.3)

The nonlinear function f in Equation 2.3 is called the activation function of the neuron, and attempts to mimic the biological process that occurs during activation of an actual neuron. Any sigmoidal function will satisfy this activation function, but the hyperbolic tangent function (tanh) was chosen in particular for this work because it allows for faster convergence when using gradient methods for training the weight parameters [30]. It is this activation function that allows neural networks to capture nonlinearities when modeling.

The neural network is trained by adjusting the weight values at each neuron to minimize an objective function that measures the squared error between the neural network's set of predicted values of the training data and the actual values of the data. Optimal weight values were determined using a *conjugate gradient* because it provides fast convergence [31]. Two separate neural networks were created for the execution time and energy predictions, respectively. As with the linear models, the neural network execution time prediction models were trained using measured execution time values of the target application, and the neural network energy use models were trained using measured energy use values of the target application.

#### 2.3.6 Model Accuracy

All models are evaluated using <u>Mean Percent Error</u> (MPE) and <u>Normalized Root Mean Squared</u> <u>Error</u> (NRMSE) to offer two different measures for comparing model predicted values to actual values. Error measurements are only made for the target application's execution time or energy use in each test, not for all applications co-located in the system.

The magnitudes of the actual values within the data vary greatly (e.g., when modeling execution time, actual values could range from as little as 150 seconds to over 1000 seconds based on the application that is being executed and the state of co-location of the applications in the system). Thus, when finding MPE, a calculation of *relative error*, allows the evaluation of prediction accuracy independent of these magnitudes for each of the M sample points of data. In the equation, predicted values are denoted  $p_j$  and <u>a</u>ctual values are denoted by  $a_j$ . MPE is defined as:

$$MPE = 100 * \frac{1}{M} \sum_{j=1}^{M} \left| \frac{p_j - a_j}{a_j} \right|.$$

(2.4)

NRMSE gives an indication of the variance of the predicted values from the actual values. For M sample points, NRMSE provides a ratio of Root Mean Squared Error (an *absolute error*) and the interval of values that the actual data can take (the largest actual data value  $a_{max}$  minus the smallest actual data value  $a_{min}$ ). Normalized root mean squared error is defined as:

$$NRMSE = \frac{\sqrt{\frac{\sum_{j=1}^{M} (p_j - a_j)^2}{M}}}{a_{max} - a_{min}} .$$

(2.5)

# 2.4 Implementation

## 2.4.1 Testing Environment

This section describes a testing environment that can be used for the modeling methodology's data collection and validation. The testing environment that is described is not only effective and easy to use for collecting the data, but also easy to replicate and can be used on a wide variety of multicore processors.

#### **Operating System**